有限状态机HDL模板

逻辑设计, 顾名思义, 只要理清了 逻辑 和 时序, 剩下的设计只是做填空题而已。

下面给出了有限状态机的标准设计,分别为 VHDL 和 Verilog 代码

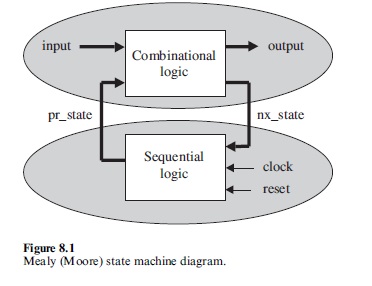

1 有限状态机

2 VHDL模板一

library IEEE;

use ieee.std_logic_1164.all; --! 1) 端口定义

entity <entity_name> is

port

(

DIN : in <data_type>;

RST : in std_logic;

CLK : in std_logic;

DOUT : out <data_type>

);

end <entity_name>; --! 2) 状态定义

architecture <arch_name> of <entity_name> is type state is (IDLE, ST1, ST2, ...);

signal c_state, n_state : state; begin --! 3) 时序逻辑

pfsmsyn: process (rst, clk)

begin

if (rst = '') then

c_state <= IDLE;

elsif (clk'event and clk='') then

c_state <= n_state;

endif;

end process; --! 4) 组合逻辑

pfsmlogic: process (din, c_state)

begin

case c_state is

when IDLE =>

if (din = ...) then

dout <= <value>; -- 输出

c_state <= state1; -- 状态

else ...

end if;

when ST1 =>

... ...

... ...

... ...

when others =>

... ... end case;

end process; end <arch_name>;

3 Verilog模板一

// 1) 端口声明

module fsm(clk, rst, ctrl, dout);

input clk, rst, ctrl;

output [n-:] dout; // n 取决于输出值的位数

reg [n-:] dout; // 2) 状态定义

parameter IDLE = , ST1 = , ST2 = , ST3 = , ....;

reg [m-:] c_state, n_state; // m 取决于‘“状态”数量的位数 // 3) 时序逻辑

always @ (posedge clk or posedge rst)

begin: SEQ

if (rst)

c_state = IDLE;

else

c_state = n_state;

end // 4) 组合逻辑

module @ (ctrl or c_state)

begin: COMB

case (c_state)

IDLE: begin

dout = <value0>;

n_state = ST1;

end

ST1: begin

dout = <value1>;

n_state = ST2;

end

ST2:

. . . . . .

. . . . . .

. . . . . .

endcase

end endmodule

参考资料:

<Circuit Design with VHDL> chapter 8 State Machines

<HDL Chip Design>

有限状态机HDL模板的更多相关文章

- 基于Unity有限状态机框架

这个框架是Unity wiki上的框架.网址:http://wiki.unity3d.com/index.php/Finite_State_Machine 这就相当于是“模板”吧,自己写的代码,写啥都 ...

- 基于Verilog HDL整数乘法器设计与仿真验证

基于Verilog HDL整数乘法器设计与仿真验证 1.预备知识 整数分为短整数,中整数,长整数,本文只涉及到短整数.短整数:占用一个字节空间,8位,其中最高位为符号位(最高位为1表示为负数,最高位为 ...

- 有限状态机FSM(自动售报机Verilog实现)

有限状态机FSM(自动售报机Verilog实现) FSM 状态机就是一种能够描述具有逻辑顺序和时序顺序事件的方法. 状态机有两大类:Mealy型和Moore型. Moore型状态机的输出只与当前状态有 ...

- 如何高效的编写Verilog HDL——进阶版

博主之前写过一篇文章来谈论如何高效的编写Verlog HDL——菜鸟版,在其中主要强调了使用Notepad++来编写Verilog HDL语言的便捷性,为什么说是菜鸟版呢,因为对于新手来说,在还没有熟 ...

- gVim编辑器 模板篇

上文介绍了gVim的常用操作,这次总结一下我自己常用的模板. 安装和配置好gVim后,在Program Files (x86)\Vim目录下有个“_vimrc”文件,双击选择gVim软件打开,在里面添 ...

- html5引擎开发 -- 引擎消息中心和有限状态机 - 初步整理 一

一 什么是有限状态机 FSM (finite-state machine),又称有限状态自动机,简称状态机,是表示有限个状态以及在这些状态之间的转移和动作等行为的数学模型.他对于逻辑以及 ...

- 转载.怎样在Quartus II中转化HDL文件为bsf文件?

步骤1 新建或打开Quartus II工程,用QII自带文本编辑器打开HDL文件. 图1 用QII自带的文本编辑器打开HDL文件 步骤2 选择File>Create / Update>Cr ...

- 算法复习——网络流模板(ssoj)

题目: 题目描述 有 n(0<n<=1000)个点,m(0<m<=1000)条边,每条边有个流量 h(0<=h<35000),求从点 start 到点 end 的最 ...

- win7+vim搭建+verilog HDL IDE

参考地址:http://www.huangdc.com/421 参考文章为2016年,部分更新贴于文章内了 安装下载vim vim在win下叫gvim,下载地址:https://www.vim.org ...

随机推荐

- Flask and uWSGI - unable to load app 0 (mountpoint='') (callable not found or import error)

Here is my directory structure: -/path/to/folder/run.py -|app -|__init__.py -|views.py -|templates - ...

- JavaMail入门第四篇 接收邮件

上一篇JavaMail入门第三篇 发送邮件中,我们学会了如何用JavaMail API提供的Transport类发送邮件,同样,JavaMail API中也提供了一些专门的类来对邮件的接收进行相关的操 ...

- 【Java Saves!】Session 5:计算机器之三--二指禅

人有十指.人类掰着手指头,发明出了0.1.2-9这十个数字.后来手指头不够用了,便发明出数位(个.十.百.千-)和满十进一的规则,称为十进制. 而计算机靠两个手指头工作.在计算机内部,只有0和1两个数 ...

- 基于bootstrap的图片轮播效果展示

<!DOCTYPE html><html lang="zh-CN"> <head> <meta charset="utf-8&q ...

- CentOS修改服务器系统时间

linux安装完毕后,一般都是国外的世界,一点都不方便设置任务,或者导致网站获取本地的时间错乱,所以就需要把服务器的时间改为和本地时间一致,也就是换成中国的时间. 第一条指令:date –s '201 ...

- Mysql基本数据操作

一.mysql中的逻辑对象 mysqld(process_id(threads)+memory+datadir)-->库-->表-->记录(由行与列组成) 什么是关系型数据库:表与表 ...

- 扩展SharePoint链接字段

默认SharePoint中的链接字段有很多限制,例如 输入文字的时候只能录入255个字符 链接显示的是文字 点击链接后只能在当前页面打开链接 - - - - - - -- - - - - - - ...

- C标准库<signal.h>实现

本文地址:http://www.cnblogs.com/archimedes/p/c-library-signal.html,转载请注明源地址. 背景知识 signal.h是C标准函数库中的信号处理部 ...

- 利用UIScrollView实现几个页面的切换

此实例可以了解一下UIScrollView的运用,以及表格跟页面跳转的内容: 原作者地址:http://www.cocoachina.com/bbs/read.php?tid=323514 效果图如下 ...

- android:descendantFocusability=”blocksDescendants”的用法

android:descendantFocusability用法简析 开发中很常见的一个问题,项目中的listview不仅仅是简单的文字,常常需要自己定义listview,自己的Adapter去继承B ...