MMCM/PLL VCO

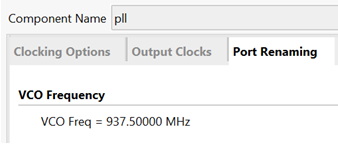

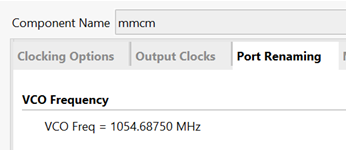

输入输出时钟频率,input 322.265625Mhz, output 312.5Mhz

对于使用MMCM与PLL的不同情况,虽然输入输出频率是一样的,但是,分/倍频系数是不同的,不能使用同一套参数(M/D/O)。

原因:VCO不一致。这个应该是vivado工具计算出来的输出时钟jitter最小的VCO。

根据这个VCO,由ug472中的公式,可以算出,M/D也是不一样的。

碰到的故障:

因为设计原因,MMCM不够用,因此部分模块使用了PLL。

时钟单元的代码,是纯verilog HDL代码,没有使用GUI,CBB模块调用了底层MMCM/PLL原语,使用宏控制。

考虑到输入输出频率一致,使用了同一套M/D/O参数。

测试时发现,使用PLL的channel,功能不对,FIFO有溢出。仔细定位后发现,PLL输出的频率与预期的不完全一致。

通过GUI重新生成PLL IPcore,发现verilog手动例化的PLL与IPcore的PLL代码,M/D/O不一致。

更新使用GUI生成代码中的M/D/O值,问题解决。

Takeaway:

如果确实需要手动例化MMCM/PLL代码,建议先在GUI中根据配置产生IP,然后将底层代码copy到所用的模块。切记不要想当然认为MMCM/PLL功能差不多,相同的输入输出频率,分/倍频系数也是相同的。

MMCM/PLL VCO的更多相关文章

- 7系列FPGA的时钟资源——UG472

时钟架构总览 7系的FPGA使用了专用的全局(Global)和区域(Regional)IO和时钟资源来管理设计中各种的时钟需求.Clock Management Tiles(CMT)提供了时钟合成(C ...

- STM32F407 RCC时钟配置

新上手项目需要使用STM32F407,在使用STM32F1系列时就喜欢自己用库函数设置系统时钟,所以F4也打算这么做,但是遇到了一些问题. 其中百度文库有篇文章关于RCC的文章将的不错,地址:http ...

- stm32f407 定时器 用的APB1 APB2 及 定时器频率

上午想要用Timer10做相对精确的延时功能,但是用示波器发现实际延时数值总是只有一半,百思不得其解.仔细查阅各处资料结合实际研究后对stm32f407的14个定时器的时钟做一个总结: 下面来源: h ...

- STM32F103X datasheet学习笔记---RCC(reset and clock control)

1.前言 本文主要记录stm32 关于reset 和 clock部分 datasheet的内容. 2.reset 有三种类型的reset:system reset, power reset, back ...

- 7 Serial Configuration 理解(三)

*Dynamic Reconfiguration Port(DRP) 动态重配置端口:在7系列FPGA中,配置存储器主要用于实现用户逻辑,连接和I / O,但它也用于其他目的. 例如,它用于指定功能块 ...

- 73.Vivado使用误区与进阶——在Vivado中实现ECO功能

关于Tcl在Vivado中的应用文章从Tcl的基本语法和在Vivado中的应用展开,继上篇<用Tcl定制Vivado设计实现流程>介绍了如何扩展甚至是定制FPGA设计实现流程后,引出了一个 ...

- Xilinx FPGA的专用时钟引脚及时钟资源相关

主要参考了https://www.eefocus.com/liu1teng/blog/12-02/237897_4533d.html .Xilinx UG471.UG472以及Xilinx Forum ...

- K60时钟分析

转载:https://blog.csdn.net/hcx25909/article/details/7164650 1.飞思卡尔K60时钟系统 飞思卡尔K60时钟系统如上图所示,可以 ...

- Xilinx约束学习笔记(二)—— 定义时钟

2. 定义时钟 2.1 关于时钟 为了获得最佳精度路径覆盖信息,必须正确定义时钟. 时钟要定义在时钟树的根 pin 或 port 上,称为 source point. 时钟的边缘应该由周期和波形进行组 ...

- DCM、PLL、PMCD、MMCM相关

摘自网上 : http://xilinx.eetop.cn/viewnews-1482 The DCM is a Digital Clock Manager - at its heart it is ...

随机推荐

- NTP同步时间

什么是NTPNTP:Network Time Protocol(网络时间协议) ️ NTP 是用于同步网络中计算机时间的协议.它的用途是把计算机的时钟同步到世界协调时UTC. UTC:Universa ...

- NewStarCTF 公开赛 2022 RE WP

Week 2 Re 前可见古人,后得见来者 chipher = [0x51, 0x5B, 0x4C, 0x56, 0x59, 0x4D, 0x50, 0x56, 0x54, 0x43, 0x7D, 0 ...

- Java线程池和Spring异步处理高级篇

开发过程中我们会遇到很多使用线程池的场景,例如异步短信通知,异步发邮件,异步记录操作日志,异步处理批量Excel解析.这些异步处理的场景我们都可以把它放在线程池中去完成,当然还有很多场景也都可以使用线 ...

- 基于声网 Flat 构建白板插件应用“成语解谜”的最佳实践

前言 本文作者赵杭天.他参加了"2022 RTE 编程挑战赛"--"赛道二 场景化白板插件应用开发" , 并凭借作品"成语解谜"获得了该赛道 ...

- 一个bug重温对JRE和JDK的关系思考

前几天做一个springboot项目时,导入的JAVA版本是17,然后后面想更贴近下企业中使用的JDK版本就改成了JDK 1,8,然后就编译错误,bug如下 java: java.lang.Unsup ...

- P/Invoke之C#调用动态链接库DLL

本编所涉及到的工具以及框架: 1.Visual Studio 2022 2..net 6.0 P/Invok是什么? P/Invoke全称为Platform Invoke(平台调用),其实际上就是一种 ...

- react抽离配置文件、配置@符号、调整src文件夹---配置scss、编写项目的页面结构、创建各个页面 src/views、开始路由、入口文件处修改代码、修改App.js布局文件、添加底部的导航布局、构建个人中心。。。声明式跳转路由、使用React UI库请求渲染首页数据、

1.回顾 2.react项目的配置 react默认创建的项目配置文件在 node_modules/react-scripts 文件夹内部 2.1 抽离配置文件 cnpm run eject cnpm ...

- broadcom Ethernet BCM57412 驱动更新记录(dkms方式)

一 背景 现场Dell R740xd2机器使用网卡Broadcom 57412 10Gb SFP+,固件版本22.21.06.80.bnxt_en.ko内核模块是该网卡的驱动,我们默认的驱动版本为1. ...

- kubernetes 启用 PHP + Nginx 网页环境

kubernetes 启用 PHP + Nginx 网页环境 传统安装方式进行安装步骤较多,使用kubernetes可以实现快速启用环境,在测试或者线上都可以做到快速 启用 编写 yaml 文件 [r ...

- android 6.0动态权限的申请

一下9组权限需要动态申请//通讯录(读.写.查询)group:android.permission-group.CONTACTS permission:android.permission.WRITE ...