verilog流水线加法器

- 四位加法器

- 两级加法实现

verilog code

module pipeliningadder(

output reg [3:0] s,

output reg co,

input [3:0] a,

input [3:0] b,

input ci,

input clk,

input rstn

);

reg [3:0] a_tmp;

reg [3:0] b_tmp;

reg [1:0] a_tmp2;

reg [1:0] b_tmp2;

reg ci_tmp;

reg [1:0] s_tmp3;

reg co_low;

reg [1:0] s_low;

reg co_hign;

reg [1:0] s_hign;

always@(posedge clk,negedge rstn)

begin

if(!rstn)

begin

a_tmp <= 4'b0;

b_tmp <= 4'b0;

ci_tmp <= 1'b0;

end

else

begin //将输入的数据缓存起来

a_tmp <= a;

b_tmp <= b;

ci_tmp <= ci;

end

end

always@(posedge clk,negedge rstn)

begin

if(!rstn)

begin

co_low <= 1'b0;

s_low <= 2'b0;

a_tmp2 <= 2'b0;

b_tmp2 <= 2'b0;

end

else

begin //低两位相加,缓存高两位

{co_low,s_low} <= a_tmp[1:0] + b_tmp[1:0] + ci_tmp;

a_tmp2 <= a_tmp[3:2];

b_tmp2 <= b_tmp[3:2];

end

end

always@(posedge clk,negedge rstn)

begin

if(!rstn)

begin

co_hign <= 2'b0;

s_hign <= 2'b0;

end

else

begin //高两位相加及与之间的低两位一并输出

{co_hign,s_hign} <= a_tmp2 + b_tmp2 + co_low;

s_tmp3 <= s_low; //寄存上一级的结果

end

end

always@(posedge clk,negedge rstn)

begin

if(!rstn)

begin

co <= 1'b0;

s <= 4'b0;

end

else

begin

{co,s} = {co_hign,s_hign,s_tmp3}; //合并上两级计算结果,输出结果

end

end

endmodule

testbench

module pipeliningadder_tb;

wire [3:0] s;

wire co;

reg [3:0] a;

reg [3:0] b;

reg ci;

reg clk;

reg rstn;

initial

begin

clk = 0;

rstn = 0;

@(posedge clk) rstn = 1;

a = 4'b0000; b = 4'b0000; ci = 0;

@(posedge clk) a = 4'b1111; b = 4'b1111; ci = 0;

@(posedge clk) a = 4'b1100; b = 4'b1001; ci = 0;

@(posedge clk) a = 4'b0111; b = 4'b0110; ci = 0;

@(posedge clk) a = 4'b0101; b = 4'b0101; ci = 1;

@(posedge clk) a = 4'b1110; b = 4'b1001; ci = 1;

@(posedge clk) a = 4'b0010; b = 4'b0110; ci = 1;

@(posedge clk) a = 4'b0110; b = 4'b1101; ci = 1;

@(posedge clk) a = 4'b1110; b = 4'b1110; ci = 1;

@(posedge clk) a = 4'b1100; b = 4'b0110; ci = 1;

@(posedge clk) a = 4'b1100; b = 4'b0101; ci = 1;

@(posedge clk) a = 4'b0011; b = 4'b1010; ci = 1;

@(posedge clk) $finish;

end

always #5 clk = ~clk;

initial begin

$fsdbDumpfile("test.fsdb");

$fsdbDumpvars();

end

pipeliningadder u_pipeliningadder(

.s(s),

.co(co),

.a(a),

.b(b),

.ci(ci),

.clk(clk),

.rstn(rstn)

);

endmodule

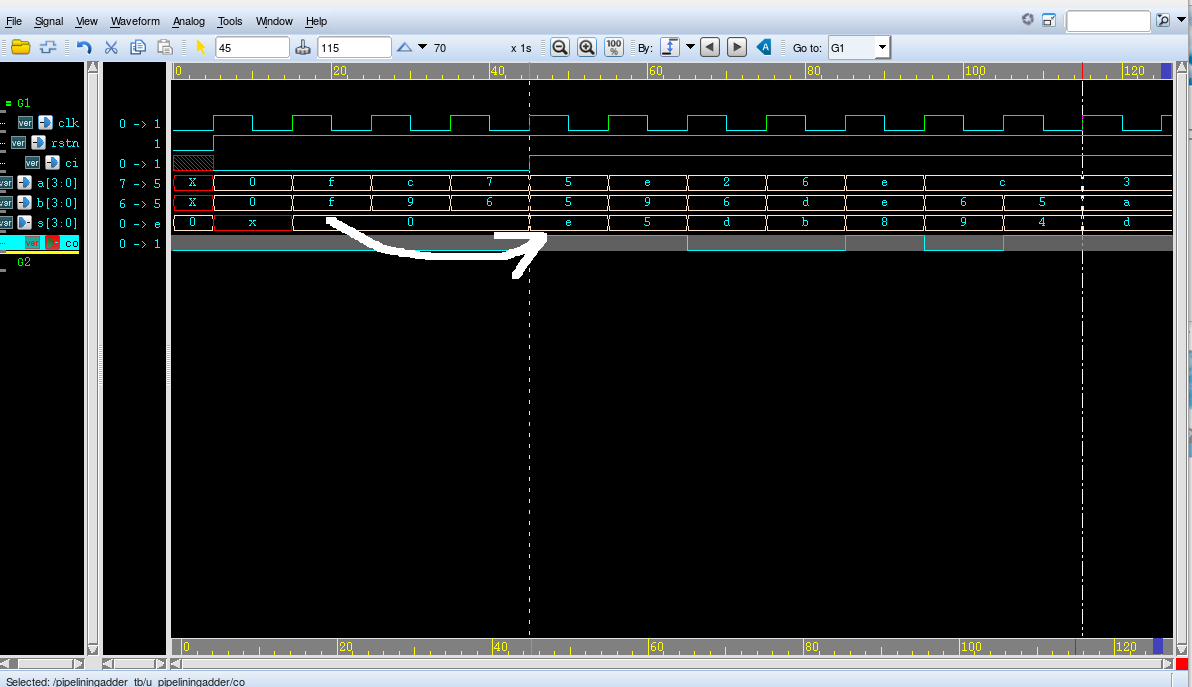

verdi波形查看

总结

使用流水线实现可以缩短关键路径,以提高运算频率,加快运算。

其他相关加法器实现方法:verilog 实现加法器

参考资料

[1]. 加法器的verilog实现

verilog流水线加法器的更多相关文章

- verilog 实现加法器

半加器 如果不考虑来自低位的进位将两个1二进制数相加,称为半加. 实现半加运算的逻辑电路称为半加器. 真值表 逻辑表达式和 \begin{align}\notag s = a{b}' + {a}'b ...

- 【FPGA学习】Verilog之加法器

在fpga工程应用设计中,随处可见加法器,乘法器等等.现在将一些常用模块和心得体会先记录下来,以便日后使用. 一位半加器: module halfadder(cout,sum,a,b); output ...

- verilog设计加法器

概述 本文利用了硬件行为描述.数据流描述.结构描述三种方法分别写了几个加法器 一位半加法器 即两个一位的二进制数相加,得到其正常相加的结果的最后一位. 仿真波形图 硬件行为描述 设计文件 123456 ...

- 流水线(pipe-line)简介

1.什么是流水线设计技术? 答:所谓流水线设计实际上是把规模较大.层次较多的组合逻辑电路分为几个级,在每一级插入寄存器组并暂存数据. K级就是有K个寄存器组,从上到下没有反馈电路. 2.流水线设计的深 ...

- 剑指Offer - 九度1507 - 不用加减乘除做加法

剑指Offer - 九度1507 - 不用加减乘除做加法2013-11-29 20:00 题目描述: 写一个函数,求两个整数之和,要求在函数体内不得使用+.-.*./四则运算符号. 输入: 输入可能包 ...

- 流水线cpu —Verilog HDL

一.准备工作 先看看书(<计算机原理与设计 Verilog HDL版>),搞懂一点原理.然后照着书上的代码写一写(用8.4的就可以了,不用8.6的). 注意mux2x32,mux4,cla ...

- verilog实现16位五级流水线的CPU带Hazard冲突处理

verilog实现16位五级流水线的CPU带Hazard冲突处理 该文是基于博主之前一篇博客http://www.cnblogs.com/wsine/p/4292869.html所增加的Hazard处 ...

- sobel流水线操作Verilog程序

sobel算子的verilog实现,采用了流水线操作 module sobel_computer ( clock , reset, OrigDataEn, //SobelAluEn, OrigData ...

- 四级流水线的8bit加法器

以流水线实现8bit 加法器. //date : 2013/8/23 //designer :pengxiaoen //function : module pipeline ( clock ,rese ...

随机推荐

- Starting nagios:This account is currently not available nagios

nagios在启动时报错 # service nagios restartRunning configuration check…done.Stopping nagios: done.Starting ...

- Max Min Middle

/*三者中的中间数*/#define Max(a,b) (a>b?a:b) #define Min(a,b) (a<b?a:b) int MiddleOfThree(int a, int ...

- c#0银行存款计算器

简介: 为银行存款客户提供一个超级计算器,简单直观操作界面,提供一个银行本意到期金额结算查询程序,方便用户选择存款方式. 功能截图: 实验步骤:利用工具栏建造窗体设计如图: 1.建立2个GroupBo ...

- GitHub——如何更新已经fork的代码

github上有个很方便的功能叫fork,将别人的工程一键复制到自己账号下.这个功能很方便,但有点不足的是,当源项目更新后,你fork的分支并不会一起更新,需要自己手动去更新.下面记录下网上找到的更新 ...

- 读书笔记 -part1

自从毕业以后到现在~看的书是越来越少了 の其实好像貌似从来没有认认真真的看书 除非工作遇到难于解决的问题迫不得已才去翻书看 有些问题也是莫名其妙的就这样解决了 于是乎被人美名其曰“高人”或&quo ...

- 初始化JQuery方法与(function(){})(para)匿名方法介绍

一.初始化JQuery对象 DOM加载完成时运行代码 1.$(document).ready(function(){ 全写 // 在这里写你的代码... }); 2.jQuery(function() ...

- explode 结合 str_replace对获取的URL处理手记

今天更新我的一个FKQQ的程序.我的一个PHP文件接收到HQ的QQ号码的字符串.因为获取的内容有大量的垃圾内容所以我用str_replace做了一个处理代码如下: $xx1 = preg_replac ...

- 0X0000124

求教卡饭网友,都快疯掉了. 最近搞设计,电脑频发出现蓝屏,今晚都出现三次了,新装的win7 64位系统,都是安装的原版光驱. 错误代码基本上都是:0x00000124 (0x000 ...

- Linux 在一个命令行上执行多个命令(转载)

对于单个命令执行我想大多数人都是明了的,也就是在一个命令行上执行一条命令.那对于在一行上执行多个命令怎么办呢,其实也很简单,只需在各命令之间加上特殊命令符号,我们常规使用到的有3个特殊命令符号. 1. ...

- rsyslog 直接kill进程,在重新启动会全部发送日志

<pre name="code" class="html">jrhapt11:/root# ps -ef | grep rsyslog root 8 ...