verilog流水线加法器

- 四位加法器

- 两级加法实现

verilog code

module pipeliningadder(

output reg [3:0] s,

output reg co,

input [3:0] a,

input [3:0] b,

input ci,

input clk,

input rstn

);

reg [3:0] a_tmp;

reg [3:0] b_tmp;

reg [1:0] a_tmp2;

reg [1:0] b_tmp2;

reg ci_tmp;

reg [1:0] s_tmp3;

reg co_low;

reg [1:0] s_low;

reg co_hign;

reg [1:0] s_hign;

always@(posedge clk,negedge rstn)

begin

if(!rstn)

begin

a_tmp <= 4'b0;

b_tmp <= 4'b0;

ci_tmp <= 1'b0;

end

else

begin //将输入的数据缓存起来

a_tmp <= a;

b_tmp <= b;

ci_tmp <= ci;

end

end

always@(posedge clk,negedge rstn)

begin

if(!rstn)

begin

co_low <= 1'b0;

s_low <= 2'b0;

a_tmp2 <= 2'b0;

b_tmp2 <= 2'b0;

end

else

begin //低两位相加,缓存高两位

{co_low,s_low} <= a_tmp[1:0] + b_tmp[1:0] + ci_tmp;

a_tmp2 <= a_tmp[3:2];

b_tmp2 <= b_tmp[3:2];

end

end

always@(posedge clk,negedge rstn)

begin

if(!rstn)

begin

co_hign <= 2'b0;

s_hign <= 2'b0;

end

else

begin //高两位相加及与之间的低两位一并输出

{co_hign,s_hign} <= a_tmp2 + b_tmp2 + co_low;

s_tmp3 <= s_low; //寄存上一级的结果

end

end

always@(posedge clk,negedge rstn)

begin

if(!rstn)

begin

co <= 1'b0;

s <= 4'b0;

end

else

begin

{co,s} = {co_hign,s_hign,s_tmp3}; //合并上两级计算结果,输出结果

end

end

endmodule

testbench

module pipeliningadder_tb;

wire [3:0] s;

wire co;

reg [3:0] a;

reg [3:0] b;

reg ci;

reg clk;

reg rstn;

initial

begin

clk = 0;

rstn = 0;

@(posedge clk) rstn = 1;

a = 4'b0000; b = 4'b0000; ci = 0;

@(posedge clk) a = 4'b1111; b = 4'b1111; ci = 0;

@(posedge clk) a = 4'b1100; b = 4'b1001; ci = 0;

@(posedge clk) a = 4'b0111; b = 4'b0110; ci = 0;

@(posedge clk) a = 4'b0101; b = 4'b0101; ci = 1;

@(posedge clk) a = 4'b1110; b = 4'b1001; ci = 1;

@(posedge clk) a = 4'b0010; b = 4'b0110; ci = 1;

@(posedge clk) a = 4'b0110; b = 4'b1101; ci = 1;

@(posedge clk) a = 4'b1110; b = 4'b1110; ci = 1;

@(posedge clk) a = 4'b1100; b = 4'b0110; ci = 1;

@(posedge clk) a = 4'b1100; b = 4'b0101; ci = 1;

@(posedge clk) a = 4'b0011; b = 4'b1010; ci = 1;

@(posedge clk) $finish;

end

always #5 clk = ~clk;

initial begin

$fsdbDumpfile("test.fsdb");

$fsdbDumpvars();

end

pipeliningadder u_pipeliningadder(

.s(s),

.co(co),

.a(a),

.b(b),

.ci(ci),

.clk(clk),

.rstn(rstn)

);

endmodule

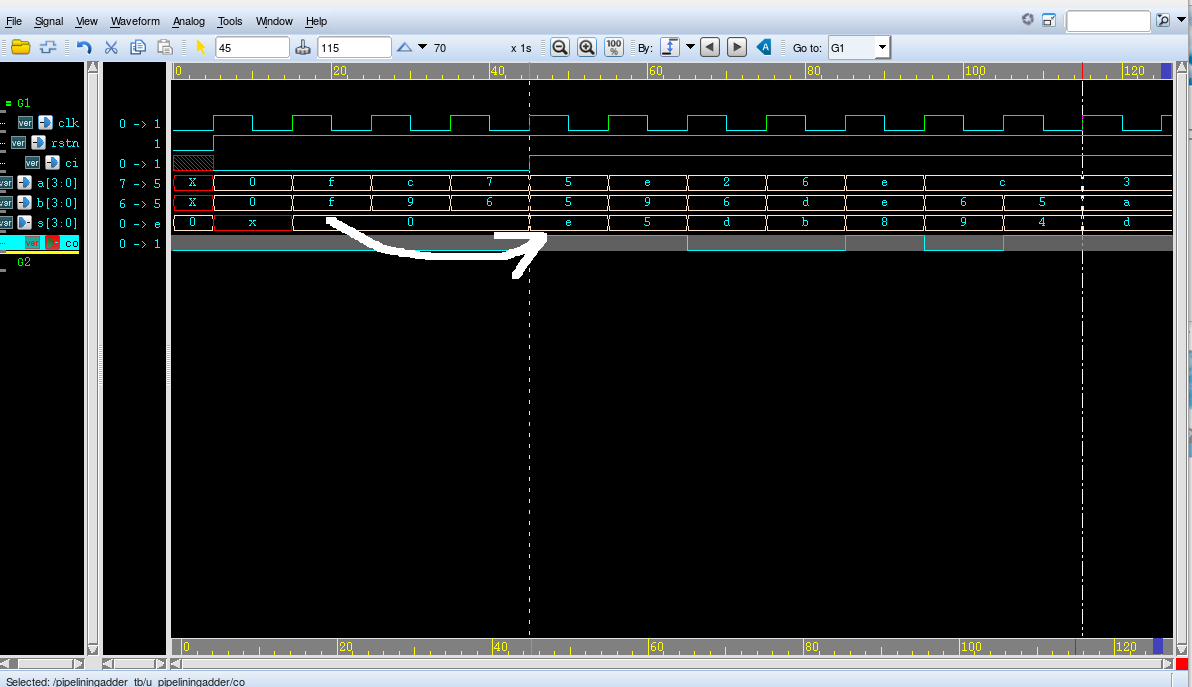

verdi波形查看

总结

使用流水线实现可以缩短关键路径,以提高运算频率,加快运算。

其他相关加法器实现方法:verilog 实现加法器

参考资料

[1]. 加法器的verilog实现

verilog流水线加法器的更多相关文章

- verilog 实现加法器

半加器 如果不考虑来自低位的进位将两个1二进制数相加,称为半加. 实现半加运算的逻辑电路称为半加器. 真值表 逻辑表达式和 \begin{align}\notag s = a{b}' + {a}'b ...

- 【FPGA学习】Verilog之加法器

在fpga工程应用设计中,随处可见加法器,乘法器等等.现在将一些常用模块和心得体会先记录下来,以便日后使用. 一位半加器: module halfadder(cout,sum,a,b); output ...

- verilog设计加法器

概述 本文利用了硬件行为描述.数据流描述.结构描述三种方法分别写了几个加法器 一位半加法器 即两个一位的二进制数相加,得到其正常相加的结果的最后一位. 仿真波形图 硬件行为描述 设计文件 123456 ...

- 流水线(pipe-line)简介

1.什么是流水线设计技术? 答:所谓流水线设计实际上是把规模较大.层次较多的组合逻辑电路分为几个级,在每一级插入寄存器组并暂存数据. K级就是有K个寄存器组,从上到下没有反馈电路. 2.流水线设计的深 ...

- 剑指Offer - 九度1507 - 不用加减乘除做加法

剑指Offer - 九度1507 - 不用加减乘除做加法2013-11-29 20:00 题目描述: 写一个函数,求两个整数之和,要求在函数体内不得使用+.-.*./四则运算符号. 输入: 输入可能包 ...

- 流水线cpu —Verilog HDL

一.准备工作 先看看书(<计算机原理与设计 Verilog HDL版>),搞懂一点原理.然后照着书上的代码写一写(用8.4的就可以了,不用8.6的). 注意mux2x32,mux4,cla ...

- verilog实现16位五级流水线的CPU带Hazard冲突处理

verilog实现16位五级流水线的CPU带Hazard冲突处理 该文是基于博主之前一篇博客http://www.cnblogs.com/wsine/p/4292869.html所增加的Hazard处 ...

- sobel流水线操作Verilog程序

sobel算子的verilog实现,采用了流水线操作 module sobel_computer ( clock , reset, OrigDataEn, //SobelAluEn, OrigData ...

- 四级流水线的8bit加法器

以流水线实现8bit 加法器. //date : 2013/8/23 //designer :pengxiaoen //function : module pipeline ( clock ,rese ...

随机推荐

- 在iptables和selinux中放行smb服务

配置selinux [root@localhost samba]# getsebool -a | grep samba 查找selinux中对samba的限制项samba_domain_control ...

- Entity Framework 的枚举类型

新增数据模型,新增“实体”之后,新增“枚举类型”,创建Enum值,将“实体”中的列和Enum关联,选中“实体”中的列属性改变类型为Enum名称,生成数据库…… 如下转自:http://item.con ...

- php遍历数据库

数据库 <?php mysql_connect("localhost","root",""); mysql_set_charset(& ...

- [java] Java NIO 学习笔记 I

如今在运行时优化方面,JVM 已然前进了一大步.现在 JVM 运行字节码的速率已经接近本地 编译代码,借助动态运行时优化,其表现甚至还有所超越.这就意味着,多数 Java 应用程序已不 再受 CPU ...

- Ubuntu 13.04 用Sublime Text 2 编译运行 JAVA

将下面的代码粘贴到JavaC.sublime-build中: { "cmd": ["javac \"$file_name\" && j ...

- java Socket 长连接 心跳包 客户端 信息收发 demo

今天写了个socket的测试小程序,代码如下 import java.io.IOException; import java.io.InputStream; import java.io.Output ...

- jquery升级到新版本报错[jQuery] Cannot read property ‘msie’ of undefined错误的解决方法(转)

最近把一个项目的jQuery升级到最新版,发现有些页面报错Cannot read property 'msie' of undefined.上jQuery网站上搜了一下,原因是$.browser这个a ...

- poj 3628 Bookshelf 2

http://poj.org/problem?id=3628 01背包 #include <cstdio> #include <iostream> #include <c ...

- 嵌入式linux内核制作

今天来总结一下mini2440的内核制作过程. 一. 将内核文件拷贝至目标目录,解压. 二.清除中间文件 命令:make distclean 三.配置内核文件 将开发板厂商制作好的内核文件拷贝至内核文 ...

- USACO6.5-Closed Fences:计算几何

Closed Fences A closed fence in the plane is a set of non-crossing, connected line segments with N c ...