Verilog的各种坑

Verilog语言和软件语言不一样,有些时候理所当然的编写,也没有报语法错误,可是功能就是不对。唉,把遇到的坑都记在本篇博客吧。

1. initial begin...end里面不能有always,如果非要在里面达到always的效果,那用forever就行了。

2. reg [3:0] a=4'd7; 这样写是对的,

wire [3:0] a=4'd7; 这样写是错的。

3. 时序电路建议赋初始值,组合电路则不需要。

4. Verilog中不建议使用 * 和 / ,%可以偶尔使用。

5. &&、||、!是逻辑符,结果为1(真)或0(假)。

&、|、~ 是按位符,结果是化为2进制后,再按位进行比较后的结果。

6. 三目运算符是允许嵌套的,例如:assign a = (b>6) ? 1 : (b<5) ? 1 : 0 ;

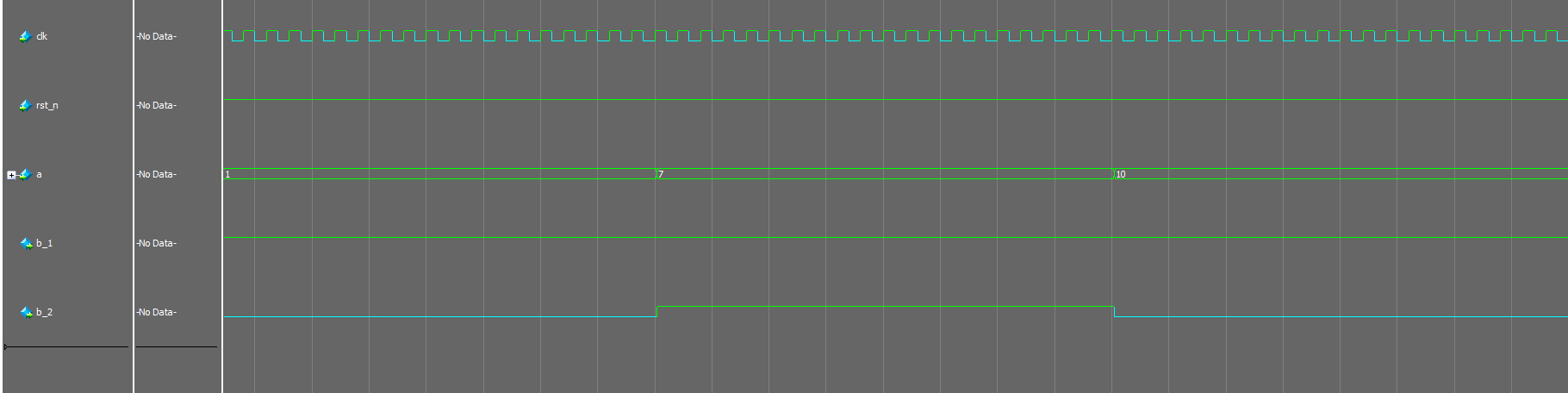

7.如果你想表达 5 < a < 9,那么你直接这样写是错的,应该写成 5 < a && a < 9 ,不信?我们看看代码和波形!

//======================================================================

// --- 名称 : test

// --- 作者 : xianyu_FPGA

// --- 日期 :

// --- 描述 : 5<a<9 5<a && a<9 的区别

/* -----------------------------

| a | 1 | 7 | 10 |

-----------------------------

| 希望的 | 0 | 1 | 0 |

-----------------------------

| b_1 | 1 | 1 | 1 |

-----------------------------

| b_2 | 0 | 1 | 0 |

-----------------------------

结论:b_2的表达方式才是对的!

*/

//====================================================================== module test

//---------------------<端口声明>---------------------------------------

(

input clk , //时钟,50Mhz

input rst_n , //复位,低电平有效

input [:] a ,

output reg b_1 ,

output reg b_2

); //----------------------------------------------------------------------

//-- 程序开始

//----------------------------------------------------------------------

always @(*)begin

if(<a<)

b_1 = ;

else

b_1 = ;

end always @(*)begin

if(<a && a<)

b_2 = ;

else

b_2 = ;

end endmodule

8.组合逻辑中,如果en1有效是一种情况,en2有效是一种情况,en1||en2有效又是一种情况,那么en1||en2有效应该写在第一个,否则会导致逻辑错误。

9.本来[3:0]led==4’b1101,

(1) 如果led <= 1;则led==4’b0001,如果led <= 4’b1111,则led==4’b1111。

(2) 如果led <= 0;则led==4’b0000。

10.[a-:b]:例如[23 -:8]等价于[23 : 16]。

11.[7:0]a <= 1’b1 << cnt:cnt=0时,a=0000_0001;cnt=1时,a=0000_0010,以此类推。

Verilog的各种坑的更多相关文章

- 关于Verilog HDL的一些技巧、易错、易忘点(不定期更新)

本文记录一些关于Verilog HDL的一些技巧.易错.易忘点等(主要是语法上),一方面是方便自己忘记语法时进行查阅翻看,另一方面是分享给大家,如果有错的话,希望大家能够评论指出. 关键词: ·技巧篇 ...

- 基于UVM的verilog验证

Abstract 本文介绍UVM框架,并以crc7为例进行UVM的验证,最后指出常见的UVM验证开发有哪些坑,以及怎么避免. Introduction 本例使用环境:ModelSim 10.2c,UV ...

- 基于UVM的verilog验证(转)

reference:https://www.cnblogs.com/bettty/p/5285785.html Abstract 本文介绍UVM框架,并以crc7为例进行UVM的验证,最后指出常见的U ...

- Verilog乘法器

乘法器,不能用乘号直接表示,略坑呀 坑归坑,做还是要做的 思路:首先乘法分为有符号乘与无符号乘,所以建立两个module分别运算有符号与无符号.然后在总module中用case语句判断输出应赋的值. ...

- Arduino+AS608指纹锁避坑记

Arduino+AS608指纹锁避坑记 .title { text-align: center; margin-bottom: 0.2em } .subtitle { text-align: cent ...

- 如何一步一步用DDD设计一个电商网站(九)—— 小心陷入值对象持久化的坑

阅读目录 前言 场景1的思考 场景2的思考 避坑方式 实践 结语 一.前言 在上一篇中(如何一步一步用DDD设计一个电商网站(八)—— 会员价的集成),有一行注释的代码: public interfa ...

- 多线程爬坑之路-Thread和Runable源码解析之基本方法的运用实例

前面的文章:多线程爬坑之路-学习多线程需要来了解哪些东西?(concurrent并发包的数据结构和线程池,Locks锁,Atomic原子类) 多线程爬坑之路-Thread和Runable源码解析 前面 ...

- Spark踩坑记——Spark Streaming+Kafka

[TOC] 前言 在WeTest舆情项目中,需要对每天千万级的游戏评论信息进行词频统计,在生产者一端,我们将数据按照每天的拉取时间存入了Kafka当中,而在消费者一端,我们利用了spark strea ...

- 多线程爬坑之路-学习多线程需要来了解哪些东西?(concurrent并发包的数据结构和线程池,Locks锁,Atomic原子类)

前言:刚学习了一段机器学习,最近需要重构一个java项目,又赶过来看java.大多是线程代码,没办法,那时候总觉得多线程是个很难的部分很少用到,所以一直没下决定去啃,那些年留下的坑,总是得自己跳进去填 ...

随机推荐

- 保护 SSH 的三把锁

转自:https://www.ibm.com/developerworks/cn/aix/library/au-sshlocks/index.html 简介 如果需要远程访问计算机并启用了 Secur ...

- 3-开发共享版APP(接入指南)-设备接入说明:使用隐藏配置

https://www.cnblogs.com/yangfengwu/p/11273226.html 该APP安装包下载链接: http://www.mnif.cn/appapk/IotDevelop ...

- 通过三层交换机实现不同VLAN间的通信

主机的IP地址以及子网掩码已列出,下面将讲解如何配置利用三层交换机来实现不同VLAN间的相互通信 SW1的命令: en //进入特权模式 conf t //全局模式 vlan 10 // ...

- tensorflow手写数字识别(有注释)

import tensorflow as tf import numpy as np # const = tf.constant(2.0, name='const') # b = tf.placeho ...

- 暂时性死区TDZ理解与总结

为什么会出现暂时性死区? 先来看看 ES6 标准中对 let/const 声明中的解释 第13章,有如下一段文字:The variables are created when their contai ...

- 块元素&行内元素

大多数HTML 元素被定义为块级元素或内联元素.块级元素在浏览器显示时,通常会以新行来开始(和结束) block元素特点 1 总是在新行上开始: 2 高度,行高以及外边距和内边距都可控制: 3 宽度缺 ...

- 多线程 interrupt()方法

java interrupt()方法只是设置线程的中断标记,当对处于阻塞状态的线程调用interrupt方法时(处于阻塞状态的线程是调用sleep, wait, join 的线程),会抛出Interr ...

- 一、JavaScript基础

一.区分大小写 ECMAScript中的一切(变量.函数名和操作符)都区分大小写,(js用于行为交互.数据交互.逻辑交互) 二.标识符 指变量.函数.属性的名字,或者函数的参数 命名规则:1.第一个字 ...

- Service Function Chaining Resource Allocation: A Survey

摘要: 服务功能链(SFC)是未来Internet的一项关键技术. 它旨在克服当前部署模型的僵化和静态限制. 该技术的应用依赖于可以将SFC最佳映射到衬底网络的算法. 这类算法称为"服务功能 ...

- RocketMQ官方启动脚本不支持jdk11的修改

以rocketmq4.5.0为例 主要涉及classpath和启动配置. nameserver: vim /opt/rocketmq/bin/runserver.sh 删除 -XX:+UseConcM ...