Verilog的各种坑

Verilog语言和软件语言不一样,有些时候理所当然的编写,也没有报语法错误,可是功能就是不对。唉,把遇到的坑都记在本篇博客吧。

1. initial begin...end里面不能有always,如果非要在里面达到always的效果,那用forever就行了。

2. reg [3:0] a=4'd7; 这样写是对的,

wire [3:0] a=4'd7; 这样写是错的。

3. 时序电路建议赋初始值,组合电路则不需要。

4. Verilog中不建议使用 * 和 / ,%可以偶尔使用。

5. &&、||、!是逻辑符,结果为1(真)或0(假)。

&、|、~ 是按位符,结果是化为2进制后,再按位进行比较后的结果。

6. 三目运算符是允许嵌套的,例如:assign a = (b>6) ? 1 : (b<5) ? 1 : 0 ;

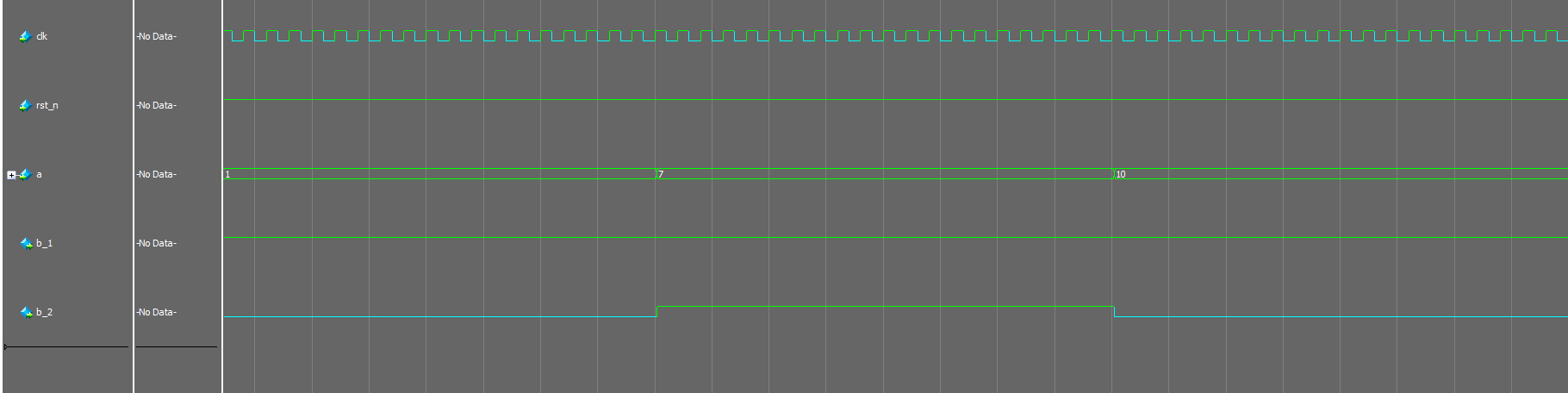

7.如果你想表达 5 < a < 9,那么你直接这样写是错的,应该写成 5 < a && a < 9 ,不信?我们看看代码和波形!

//======================================================================

// --- 名称 : test

// --- 作者 : xianyu_FPGA

// --- 日期 :

// --- 描述 : 5<a<9 5<a && a<9 的区别

/* -----------------------------

| a | 1 | 7 | 10 |

-----------------------------

| 希望的 | 0 | 1 | 0 |

-----------------------------

| b_1 | 1 | 1 | 1 |

-----------------------------

| b_2 | 0 | 1 | 0 |

-----------------------------

结论:b_2的表达方式才是对的!

*/

//====================================================================== module test

//---------------------<端口声明>---------------------------------------

(

input clk , //时钟,50Mhz

input rst_n , //复位,低电平有效

input [:] a ,

output reg b_1 ,

output reg b_2

); //----------------------------------------------------------------------

//-- 程序开始

//----------------------------------------------------------------------

always @(*)begin

if(<a<)

b_1 = ;

else

b_1 = ;

end always @(*)begin

if(<a && a<)

b_2 = ;

else

b_2 = ;

end endmodule

8.组合逻辑中,如果en1有效是一种情况,en2有效是一种情况,en1||en2有效又是一种情况,那么en1||en2有效应该写在第一个,否则会导致逻辑错误。

9.本来[3:0]led==4’b1101,

(1) 如果led <= 1;则led==4’b0001,如果led <= 4’b1111,则led==4’b1111。

(2) 如果led <= 0;则led==4’b0000。

10.[a-:b]:例如[23 -:8]等价于[23 : 16]。

11.[7:0]a <= 1’b1 << cnt:cnt=0时,a=0000_0001;cnt=1时,a=0000_0010,以此类推。

Verilog的各种坑的更多相关文章

- 关于Verilog HDL的一些技巧、易错、易忘点(不定期更新)

本文记录一些关于Verilog HDL的一些技巧.易错.易忘点等(主要是语法上),一方面是方便自己忘记语法时进行查阅翻看,另一方面是分享给大家,如果有错的话,希望大家能够评论指出. 关键词: ·技巧篇 ...

- 基于UVM的verilog验证

Abstract 本文介绍UVM框架,并以crc7为例进行UVM的验证,最后指出常见的UVM验证开发有哪些坑,以及怎么避免. Introduction 本例使用环境:ModelSim 10.2c,UV ...

- 基于UVM的verilog验证(转)

reference:https://www.cnblogs.com/bettty/p/5285785.html Abstract 本文介绍UVM框架,并以crc7为例进行UVM的验证,最后指出常见的U ...

- Verilog乘法器

乘法器,不能用乘号直接表示,略坑呀 坑归坑,做还是要做的 思路:首先乘法分为有符号乘与无符号乘,所以建立两个module分别运算有符号与无符号.然后在总module中用case语句判断输出应赋的值. ...

- Arduino+AS608指纹锁避坑记

Arduino+AS608指纹锁避坑记 .title { text-align: center; margin-bottom: 0.2em } .subtitle { text-align: cent ...

- 如何一步一步用DDD设计一个电商网站(九)—— 小心陷入值对象持久化的坑

阅读目录 前言 场景1的思考 场景2的思考 避坑方式 实践 结语 一.前言 在上一篇中(如何一步一步用DDD设计一个电商网站(八)—— 会员价的集成),有一行注释的代码: public interfa ...

- 多线程爬坑之路-Thread和Runable源码解析之基本方法的运用实例

前面的文章:多线程爬坑之路-学习多线程需要来了解哪些东西?(concurrent并发包的数据结构和线程池,Locks锁,Atomic原子类) 多线程爬坑之路-Thread和Runable源码解析 前面 ...

- Spark踩坑记——Spark Streaming+Kafka

[TOC] 前言 在WeTest舆情项目中,需要对每天千万级的游戏评论信息进行词频统计,在生产者一端,我们将数据按照每天的拉取时间存入了Kafka当中,而在消费者一端,我们利用了spark strea ...

- 多线程爬坑之路-学习多线程需要来了解哪些东西?(concurrent并发包的数据结构和线程池,Locks锁,Atomic原子类)

前言:刚学习了一段机器学习,最近需要重构一个java项目,又赶过来看java.大多是线程代码,没办法,那时候总觉得多线程是个很难的部分很少用到,所以一直没下决定去啃,那些年留下的坑,总是得自己跳进去填 ...

随机推荐

- 浏览器事件循环 & nodejs事件循环

第1篇:如何理解EventLoop——宏任务和微任务篇 宏任务(MacroTask)引入 在 JS 中,大部分的任务都是在主线程上执行,常见的任务有: 渲染事件 用户交互事件 js脚本执行 网络请求. ...

- (转)React事件处理函数必须使用bind(this)的原因

1.JavaScript自身特性说明如果传递一个函数名给一个变量,之后通过函数名()的方式进行调用,在方法内部如果使用this则this的指向会丢失.示例代码:首先我们创建test对象并直接调用方法 ...

- nbbnbnbnbnb

1.本章学习总结(2分) 1.1 学习内容总结 结构体的定义与赋值 结构类型定义的一般形式为: struct 结构名 { 类型名 结构成员1: 类型名 结构成员2: ... 类型名 结构成员3: }; ...

- ES6 解构对象和数组

1.解构对象 let saveFiled = { extension: "jpg", name:"girl", size:14040 }; ES5 functi ...

- 「ZJOI2019」Minmax搜索

传送门 Solution 叶子节点的变化区间是连续的,可得知非叶子节点的权值变化区间也是连续的 由此可知,\(W\)的变化值的可行域也是连续的,所以只需要看它能否变为\(W+1\)或\(W-1\) 对 ...

- Markdown文字添加颜色

转自:原文地址 添加红色 效果: 写法: $\color{red}{red}$ 添加绿色 效果: 写法: $\color{green}{green}$ 添加蓝色 效果: 写法: $\color{blu ...

- SpringMVC(下)

一.访问静态资源 在进行Spring MVC的配置时,通常我们会配置一个dispatcher servlet用于处理对应的URL 在设置url-pattern时可以设置三种形式 (1)/* :拦截所有 ...

- unity2019新建LWRP项目出错:Failed to resolve project template

原因不详,但是在C盘创建项目的确会出现这个问题,改到D盘或E盘就没这个问题了

- Maven在jar中生成重复的pom.xml和pom.properties文件

eclispe maven打包的时候总是出现"生成的jar的META-INF中,重复的pom.xml和pom.properties文件.",maven命令直接打包则没有这个问题. ...

- 企业架构 Red Hat Drools KIE Project 三大核心产品

美团放弃Drools自研规则引擎: https://blog.csdn.net/qq_18603599/article/details/80767912 Drools rule engine虽然好,但 ...