回看《例说FPGA》---DDR2控制器集成与读写测试

回看《例说FPGA》

---DDR2控制器集成与读写测试

1.DDR2 IP核的配置

需要弄清楚的选项主要有:

需要弄清楚的选项主要有:

PLL reference clock frequency

Memory clock frequency

Controller data rate

对于DDR2 芯片的选型,可以在Memory Presets 里面选择,如果没有符合的器件,可以任意选中一个器件,点击modify parameters 按钮,在 preset Editor 里面进行参数配置。

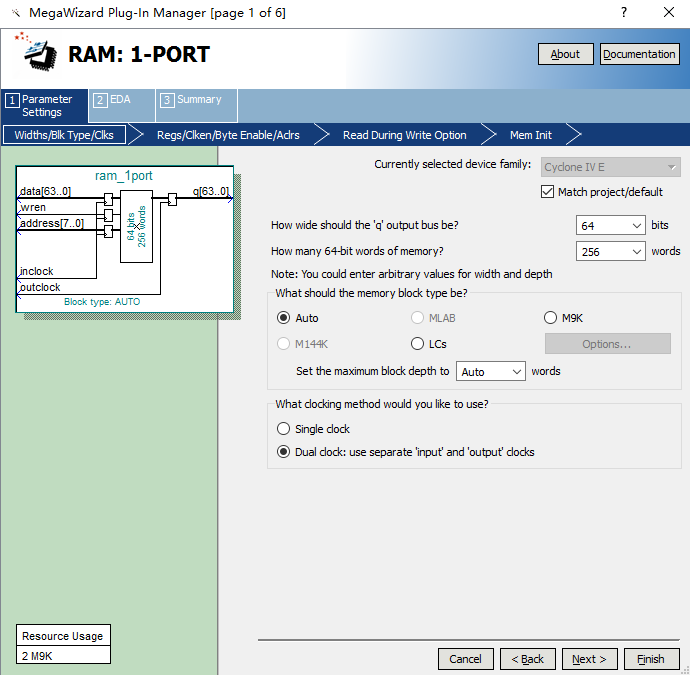

2.片上RAM的配置

需要设置的选项有:

输出数据的位宽

存储器的深度

双时钟或单时钟

双时钟意味着输入输出采用不同的时钟:

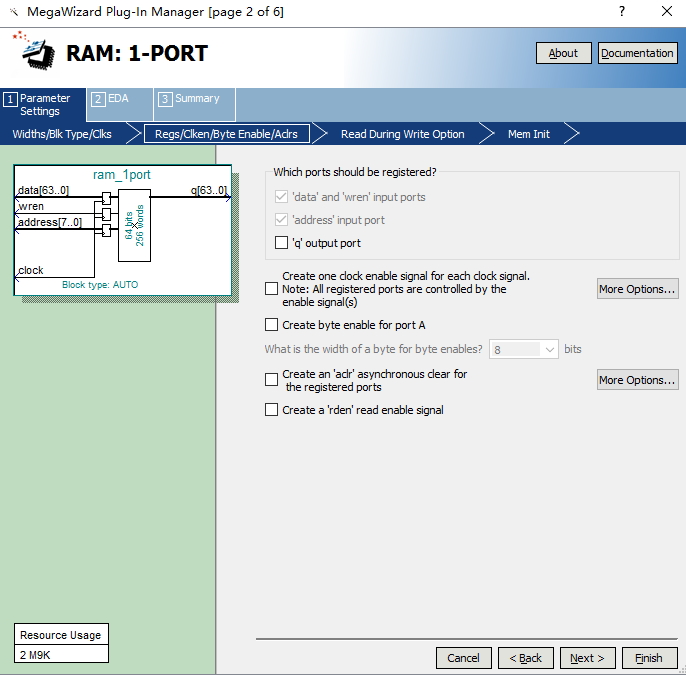

在regs/clken/byte enable/aclrs选项卡中,需要设置的是:

Which ports should be registered? ‘ q output port’,如果选中,则在输出端加上一个触发器,输出数据时候,就会用clock信号打节拍。如果不选中,则:

3.数据源产生模块

3.数据源产生模块

实验的整体框图如下图所示:

数据源产生模块实现的功能为:

每秒定时DDR2数据写入控制;

每秒定时DDR2数据读出控制;

将读出的数据写入片上RAM中(RAM IP核在此模块中进行实例化);

此模块主要用来与DDR2 controller IP核进行通信,首先需要对DDR2 controller的信号多一些了解:

module ddr2_contral (

local_address,

local_write_req,

local_read_req,

local_burstbegin,

local_wdata,

local_be,

local_size,

global_reset_n,

pll_ref_clk,

soft_reset_n,

local_ready,

local_rdata,

local_rdata_valid,

local_refresh_ack,

local_init_done,

reset_phy_clk_n,

mem_odt,

mem_cs_n,

mem_cke,

mem_addr,

mem_ba,

mem_ras_n,

mem_cas_n,

mem_we_n,

mem_dm,

phy_clk,

aux_full_rate_clk,

aux_half_rate_clk,

reset_request_n,

mem_clk,

mem_clk_n,

mem_dq,

mem_dqs); input [:] local_address;

input local_write_req;

input local_read_req;

input local_burstbegin;

input [:] local_wdata;

input [:] local_be;

input [:] local_size;

input global_reset_n;

input pll_ref_clk;

input soft_reset_n;

output local_ready;

output [:] local_rdata;

output local_rdata_valid;

output local_refresh_ack;

output local_init_done;

output reset_phy_clk_n;

output [:] mem_odt;

output [:] mem_cs_n;

output [:] mem_cke;

output [:] mem_addr;

output [:] mem_ba;

output mem_ras_n;

output mem_cas_n;

output mem_we_n;

output [:] mem_dm;

output phy_clk;

output aux_full_rate_clk;

output aux_half_rate_clk;

output reset_request_n;

inout [:] mem_clk;

inout [:] mem_clk_n;

inout [:] mem_dq;

inout [:] mem_dqs;

ddr2 controller模块的接口可以分为三类:

第一类:系统接口,包含系统或PLL的复位,时钟等接口;

第二类:以local开头的接口,是DDR2 IP核与用户逻辑间的接口;(数据源产生模块主要用到的就是这类接口信号,需要弄懂这些信号的操作时序)

第三类:以mem开头的接口,是DDR2 IP核与FPGA外部DDR2芯片的接口;(只需要做引脚锁定,编程基本用不到)

关于使用DDR2 IP核用户外部逻辑操作loca信号的时序图如下:

在遇到local_ready拉低的读操作,下列信号必须保持到local_ready拉高为止:

local_read_req;

local_size;

local_addr;

写数据的时候,整个过程中,必须保持local_write_req信号一直有效。

逻辑代码:

module data_source(

clk, //75MHz

rst_n,

local_address,

local_write_req,

local_read_req,

local_wdata,

local_ready,

local_rdata,

local_rdata_valid,

local_init_done

); // 1/75MHz = 13.33ns;

input clk;

input rst_n;

output [:]local_address;

output local_write_req;

output local_read_req;

output [:]local_wdata;

input local_ready;

input [:]local_rdata;

input local_rdata_valid;

input local_init_done; reg[:] scnt;

reg[:] times; //计数器,当local_init_done有效时,计数器scnt开始计数

always @(posedge clk or negedge rst_n)

if(!rst_n) scnt <= 'd0;

else if(local_init_done) scnt <= scnt+'b1; wire timer_wrreq = (scnt == 'h00_001_000); // 55us

wire timer_rdreq = (scnt == 'h00_005_000); // 273us //每当timer_rdreq有效时,计数器times增加1,此模块用来计数读取数据的个数

always @(posedge clk or negedge rst_n)

if(!rst_n) times <= 'd0;

else if(timer_rdreq) times <= times+'b1; //状态机

parameter SIDLE = 'd0;

parameter SWRDB = 'd1;

parameter SRDDB = 'd2;

parameter SSTOP = 'd3; reg[:] cstate;

reg[:] num; always @(posedge clk or negedge rst_n)

if(!rst_n) cstate <= SIDLE;

else begin

case(cstate)

SIDLE: begin //控制状态机的跳转,timer_wrreq有效,则跳转到SWRDB,timer_rdreq有效,则跳转到SRDDB

if(timer_wrreq) cstate <= SWRDB;

else if(timer_rdreq) cstate <= SRDDB;

else cstate <= SIDLE;

end

SWRDB: begin //如果写入255个数据,并且local_ready有效,则状态结束

if((num == 'd255) && local_ready) cstate <= SSTOP;

else cstate <= SWRDB;

end

SRDDB: begin ////如果读取255个数据,并且local_ready有效,则状态结束

if((num == 'd255) && local_ready) cstate <= SSTOP;

else cstate <= SRDDB;

end

SSTOP: cstate <= SIDLE;

default: cstate <= SIDLE;

endcase

end always @(posedge clk or negedge rst_n)

if(!rst_n) num <= 'd0;

else if((cstate == SWRDB) || (cstate == SRDDB)) begin //如果状态处在SWRDB或者是SRDDB时,进入下一个判断阶段

if(local_ready) num <= num+'b1; //如果local_ready有效时,num开始计数

else ;

end

else num <= 'd0; assign local_address = (cstate == SWRDB) ? {'h0a55,2'd1,num[:]}:{'h0a55,2'd1,num[:]}; //地址采用num这个寄存器来进行地址偏移

assign local_wdata = {times,{num[:],'b00},times,{num[5:0],2'b01},times,{num[:],'b10},times,{num[5:0],2'b11}};

assign local_write_req = (cstate == SWRDB); //当状态机处在SWRDB时,发出写请求

assign local_read_req = (cstate == SRDDB); //当状态机处在SRDDB时,发出读请求 reg[:] ram_addr;

always @(posedge clk or negedge rst_n)

if(!rst_n) ram_addr <= 'd0;

else if(timer_rdreq) ram_addr <= 'd0; //当timer_rdreq读数请求有效时,ram_addr清零,即读数据请求到来时,ram_addr指向第一个地址

else if(local_rdata_valid) ram_addr <= ram_addr+'b1; //当local_rdata_valid信号有效时候,片上ram_addr开始偏移

else ; //此ram只写入,不输出

ram_1port u1 (

.address(ram_addr),

.clock(clk),

.data(local_rdata),

.wren(local_rdata_valid),

.q()

); endmodule

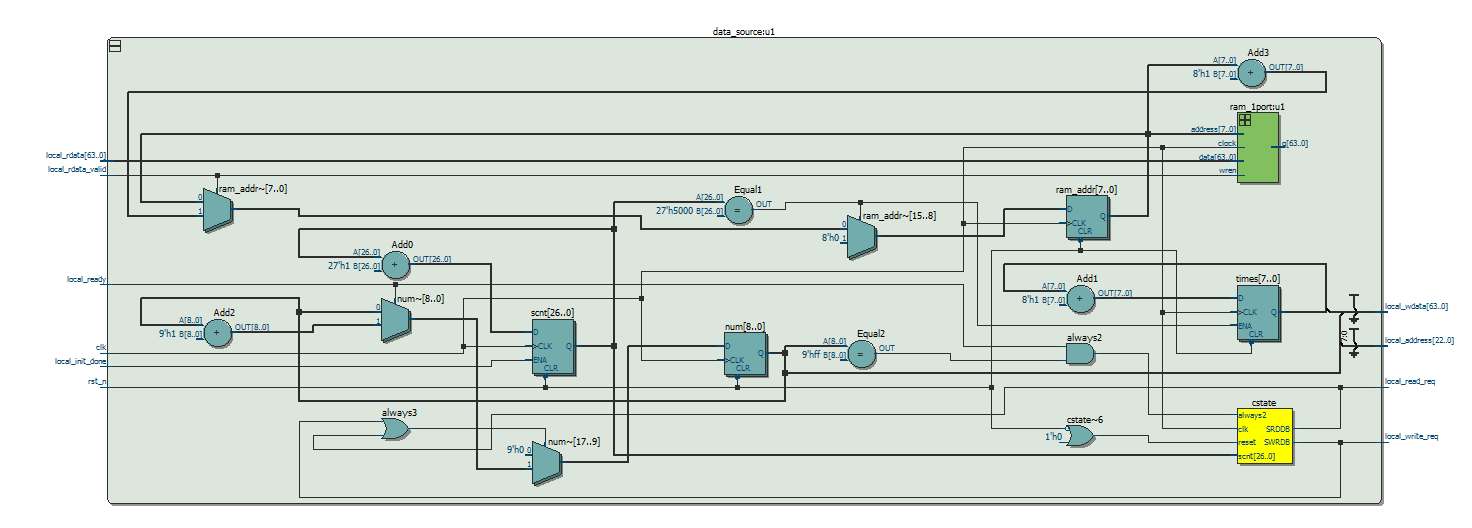

综合结果,RTL图:

回看《例说FPGA》---DDR2控制器集成与读写测试的更多相关文章

- Vue 2.5 发布了:15篇前端热文回看

Vue 2.5 发布了:15篇前端热文回看 2017-11-02 前端大全 (点击上方公众号,可快速关注) 本文精选了「前端大全」2017 年 10 月的 15 篇热门文章.其中有职场分享.技术分享和 ...

- Altera DDR2控制器学习笔记

Altera DDR2控制器使用IP的方式实现,一般很少自己写控制器代码. ddr22 ddr22_inst ( .aux_full_rate_clk (mem_aux_full_rate_clk), ...

- 【RPA之家转载RPA创新产业峰会回看】机器人流程自动化专利态势报告

[RPA之家转载RPA创新产业峰会回看]机器人流程自动化专利态势报告 自动化的一个专利情况的监测,就是全球监测的情况.今天我可能给大家汇报的主要是三个方面,第一个方面就是讲一下全球投资智能化的专利的一 ...

- CNTV视频回看下载地址

这其实不是新方法了,这个方法早在五六年前大家就在用,至今也没失效.但是五六年前那时候这个方法可以下载到过去三个月内CNTV直播过的视频,而现在只能下到一个星期的.之所以要下载回看版本,是因为比栏目版本 ...

- 利用Nginx搭建RTMP视频直播,点播服务器,ffmpeg推流,回看

一.环境和工具 ubuntu 14.04 desktop 不用server的原因是一部分的演示用到了linux视频播放和直播软件,自己还要装桌面,麻烦. 不建议使用 最新的16TLS,我一开始 ...

- 6 大主流 Web 框架优缺点对比:15篇前端热文回看

摘自:http://blog.csdn.net/VhWfR2u02Q/article/details/78993079 注:以下文章,点击标题即可阅读 <6 大主流 Web 框架优缺点对比> ...

- 2020 .NET 开发者峰会顺利在苏州落幕,相关数据很喜人以及线上直播回看汇总

在2019年上海中国.NET开发者大会的基础上,2020年12月19-20日 继续以"开源.共享.创新" 为主题的第二届中国 .NET 开发者峰会(.NET Conf China ...

- 2021 .NET 开发者峰会顺利在网上落幕,线上直播回看汇总

.NET Conf China 2021 是面向开发人员的社区峰会,基于 .NET Conf 2021的活动,庆祝 .NET 6 的发布和回顾过去一年来 .NET 在中国的发展成果展示,它是由中国各地 ...

- 基于FPGA的DDR3多端口读写存储管理系统设计

基于FPGA的DDR3多端口读写存储管理系统设计 文章出处:电子技术设计 发布时间: 2015/03/12 | 1747 次阅读 每天新产品 时刻新体验专业薄膜开关打样工厂,12小时加急出货 机载 ...

随机推荐

- POJ 2369 Permutations(置换群概念题)

Description We remind that the permutation of some final set is a one-to-one mapping of the set onto ...

- ImportError: No module named 'xml'

/********************************************************************************* * ImportError: No ...

- kali的安装

https://www.youtube.com/watch?v=sB3bchzlwio 注意视频中选择的是kali 2016.2版本, 在VMware中选择了Linux-Debian 8.*64(好像 ...

- GitHub教程手册、使用流程

简述GitHub的使用方法 本文提供全流程,中文翻译.Chinar坚持将简单的生活方式,带给世人!(拥有更好的阅读体验 -- 高分辨率用户请调整网页缩放比例至200%) 1 注册过GitHub的朋友, ...

- 打开视图 :1449 - the user specified as a definer ('root'@'%')does not exist

从一个数据库数据迁移到本地localhost 程序在调用到数据库的视图时报错,直接在数据库中打开视图时也报错,类似: mysql 1449 : The user specified as a ...

- 配置apache-maven-3.6.0时所遇到的坑(一)

在命令行窗口中输入:mvn -v 或 直接 mvn 时报错:“错误: 找不到或无法加载主类 org.codehaus.plexus.classworlds.launcher.Lau ...

- 用requestAnimationFrame优化Web动画

requestAnimationFrame是什么? 在浏览器动画程序中,我们通常使用一个定时器来循环每隔几毫秒移动目标物体一次,来让它动起来.如今有一个好消息,浏览器开发商们决定:“嗨,为什么我们不在 ...

- ACM-ICPC 2018 沈阳赛区网络预赛-D:Made In Heaven(K短路+A*模板)

Made In Heaven One day in the jail, F·F invites Jolyne Kujo (JOJO in brief) to play tennis with her. ...

- NetCore平台下使用RPC框架Hprose

NetCore下使用RPC框架Hprose https://www.jianshu.com/p/c903fca44d5d Hprose是国内非常优秀的RPC框架,和其它RPC框架比较起来,其它框架一般 ...

- java中实现Comparable接口实现自定义排序

class Student implements Comparable{ String name; int gpa; @Override public int compareTo(Object arg ...