PCIE基本知识

- 前言

之前主要都在做FPGA算法层面的东西,最近觉得对于接口方面的知识比较欠缺,打算以PCI-E为例来系统的学习一下接口方面的知识。

- PCI-E全称PCI Express,是一种高速总线技术。各种PCI-E设备通过PCI-E协议互相连接,形成PCI-E系统,其拓扑结构如下所示:

其中,根联合体是连接CPU,主储存器到PCI-E总线结构的设备,相当于PCI系统中的北桥。FSB为Front Side Bus,是连接CPU与北桥的总线。可以根联合体上延伸出多个PCI-E接口。交换开关也可以引出多个PCI-E端口,从而连接更多的PCI-E端点设备。这里的端点设备也类似于显卡等PCI-E设备,可以是网卡,蓝牙设备,硬盘等。PCI-E-PCI桥保证了PCI设备也能接入PCI-E系统,增加了兼容性。

- 下面分析PCI-E的传输协议

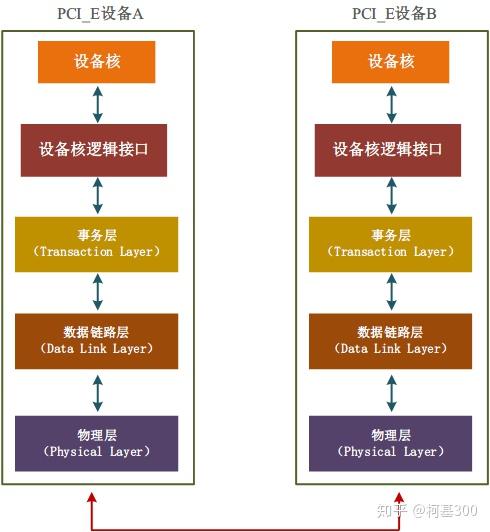

PCI-E协议规定采用三层分层协议来实现数据的传输,类似于网络通信中的TCP/IP通信协议,如下图所示:

上图展示了PCI-E设备A喝PCI-E设备B的通信协议,其中设备核和设备核接口可以简单的理解为应用层和应用层的接口,我们主要关心的是下面的三层,即事务层(TL层),数据链路层(DL层)和物理层(PL层)。

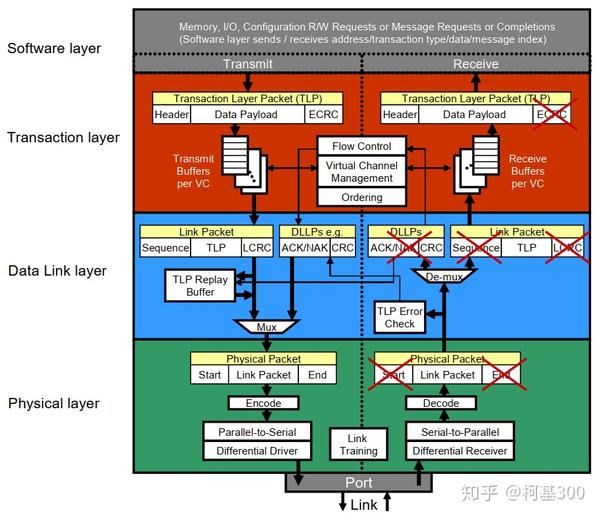

PCI_E设备之间通过数据包的形式进行传输,因此可以将三层的数据包分别表示为TLP(Transcation Layer package),DLLP和PLP。PCI-E设备发送端首先通过应用层和应用层接口传输TLP对应协议的数据格式给TL层,随后DL层对TLP进行二次打包形成DLLP在传输到PL层,PL层对数据DLLP进行编码后通过模拟信号来进行传输,接收端进行逆向操作得到最后的TLP,并最终解码成应用层需要的数据。

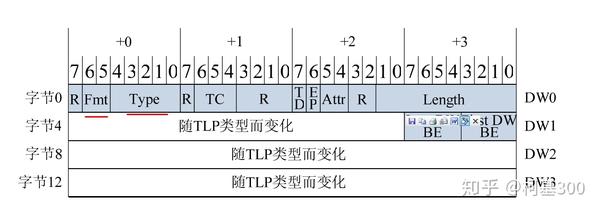

- TL层为数据添加包头(Header)和ECRC,这里的ECRC表示(End to end CRC),表示事务层的校验CRC编码。一个TLP如图所示:

Header是TLP的核心部分,其大小主要在3DW或4DW(12字节或16字节,96bit or 128bit),以4DW(128bit为例),其DW0~DW3的结构如图所示:

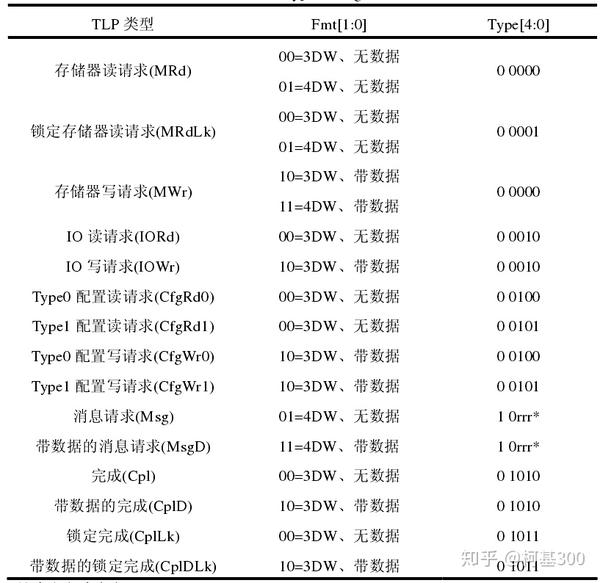

以DW0为例,DW0[9:0]表示数据长度(length),其最大值为1DW*2^10 = 4KB;DW0[13:12]表示数据包的属性,DW0[13] == 1表示使能PCI-X式的宽松排序,DW0[12] == 1表示不要求系统硬件去监控Cache;DW0[22:20]可以设置TC0~TC7四种不同的状态,默认TC0,用于流量控制;DW0[16] TD==1表示TLP包含ECRC;至于DW0[30:29]的Fmt和DW0[28:24]的Type,主要负责配置寄存器的一些读写请求和配置,如下表所示:

除此之外还有很多字段是根据不同的TLP类型而变化的,具体的可以配置TLP可以查询:PCI_Express_Specification这本PDF第二章。

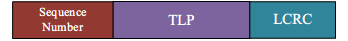

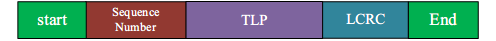

- DL层介于TL层和PL层,在发送端对TLP进行打包后发送到PL层,接收端则对PL层接包在传输到TL层,一个DL层传输的Package如下图所示:

DL层主要实现了三个功能:数据交换;错误检测/重试;初始化以及电源管理。

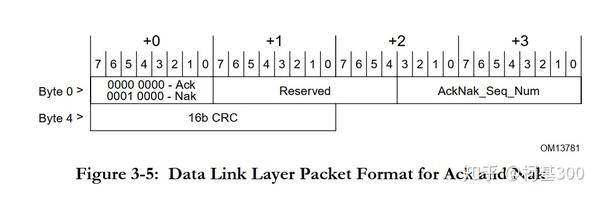

在错误检测/重试功能的实现中,DL层通过为TLP添加了Sequence Number和LCRC来实现。需要注意的是,PCI-E 设备B的DL层在接收到对应的Package时需要,返回一个应答包来确认或否定确认,即Ack/Nak DLLP,如下所示:

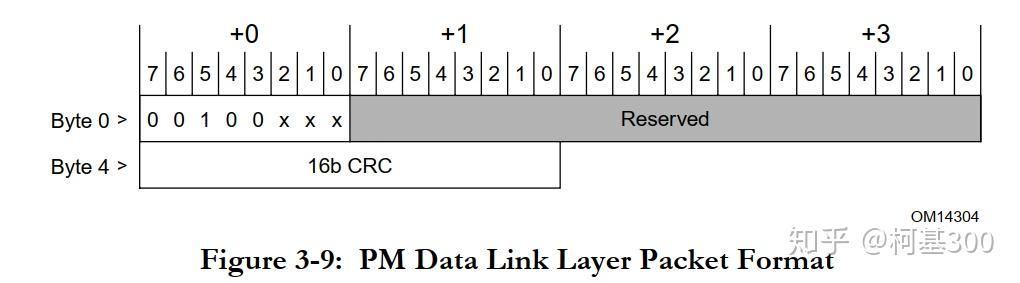

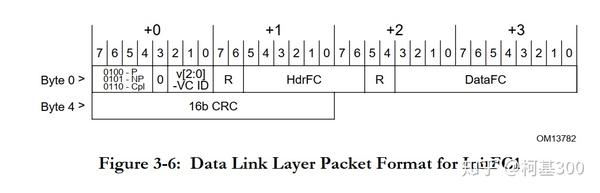

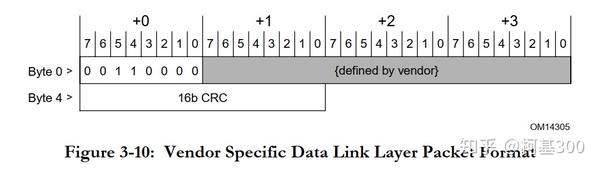

除此之外,根据不同的用途,DLLP可以分为很多种,大致可以分为四种常用类型,即对TLP的应答包—Ack/Nak DLLP,电源管理DLLP,流控制DLLP以及厂商自定义DLLP,分别如下所示:

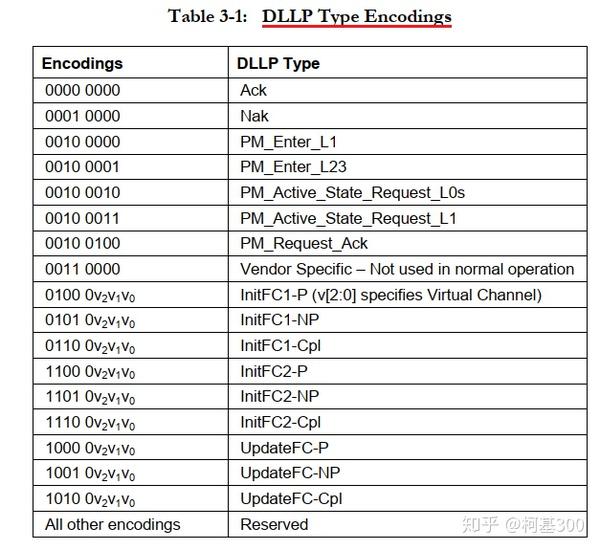

其中,Ack/Nak DLLP中的Ack和Nak分别表示确认Sequcence Number——成功收到一定数量的TLP和否定确认Sequcence Number——来启动重试功能;fig3-6中的FC1表示流控制(Flow Control);fig 3-9中的PM表示Power Management。关于Byte 0[31:24]表示DLLP Type字段,其各个字段的编码以及对应功能如下标所示:

除了上述功能,DL层还提供了数据完整性检查和CRC校验等功能,具体可以参考 PCI_Express_Specification第三章。

- 发送端PL层将DL层过来的package进行编码并发送,其中涉及逻辑子模块和电气子模块。逻辑子模块将上层的数据处理后送入电气层,在逻辑层对上层传输过来的Package进行的操作主要是添加一个帧头和帧尾:

一个完成的PCI-E发送-接收模型如下图所示:

PCI_E协议的总体介绍到这里就告一段落了,如果以上协议的逻辑部分通过FPGA去纯撸代码实现感觉还是比较困难的,后面有空再去研究一下xilinx 的IP实现。

PCIE基本知识的更多相关文章

- 转:PCIe基础知识

PCIe基础知识 版权声明:本文为博主原创文章,未经博主允许不得转载. https://blog.csdn.net/zqixiao_09/article/details/51842542 PCIe ...

- FPGA实战操作(2) -- PCIe总线(协议简述)

目录 1. PCIe基础知识 2. 事务层协议 2.1 数据包结构 2.2 帧头含义详述 3. 报文举例 3.1 寄存器读报文 3.2 完成报文 4. 机制简述 4.1 Non-Posted和Post ...

- PCIE学习链接集合

<PCIE基础知识+vivado IP core设置> https://blog.csdn.net/eagle217/article/details/81736822 <一步一步开始 ...

- 012 PCIe总线的基础知识

一.PCIe总线的基础知识 与PCI总线不同,PCIe总线使用端到端的连接方式,在一条PCIe链路的两端只能各连接一个设备,这两个设备互为是数据发送端和数据接收端.PCIe总线除了总线链路外,还具有多 ...

- 4.1 PCIe总线的基础知识

与PCI总线不同,PCIe总线使用端到端的连接方式,在一条PCIe链路的两端只能各连接一个设备,这两个设备互为是数据发送端和数据接收端.PCIe总线除了总线链路外,还具有多个层次,发送端发送数据时将通 ...

- [转帖]PCI-E的部分知识

PCI-E PCI-E全称是PCI Express,是新一代的总线接口.采用了目前业内流行的点对点串行连接,比起PCI以及更早期的计算机总线的共享并行架构,每个设备都有自己的专用连接,不需要向整个总线 ...

- PCIe基础篇(一)、基础知识扫盲

1.PCIe:Peripheral Component interconnect Expess,外围组件接口互联,属于第三代IO总线,PCIe的传输速率指的是实际的有效传输速率,为RAW data(原 ...

- PCIe知识摘要记录

摘: 一. 在PCIe的Spec中,并没有特别详细的关于Root Complex的定义,从实际的角度来讲,可以把Root Complex理解为CPU与PCIe总线系统通信的媒介.Endpoint处于P ...

- 第1章 PCI总线的基本知识

PCI总线作为处理器系统的局部总线,主要目的是为了连接外部设备,而不是作为处理器的系统总线连接Cache和主存储器.但是PCI总线.系统总线和处理器体系结构之间依然存在着紧密的联系. PCI总线作为系 ...

随机推荐

- C# 中 AppDomain 的一些理解

C# 中 AppDomain 的一些理解 前言 一直想写一个这样的程序:与其它的程序完全解耦,但可以动态的加载其它程序,并执行其中的特定方法,执行完后可以卸载,完全不影响该程序本身.最近无意间发现了 ...

- Docker 容器间的单向连接

Docker 容器间的单向连接 前言 a. 本文主要为 Docker的视频教程 笔记. b. 环境为 CentOS 7.0 云服务器 c. 上一篇:Dockerfile 自动制作 Docker 镜像( ...

- MSSQL数据库安全实验

管理SQL Server认证模式 (1)确认 SQL Server 验证 ①在桌面上单击"开始",选择"程序"→"Microsoft SQL Serv ...

- 如何在word中美观地插入编程代码

零.缘起 在整理Java笔记时,想把代码直接贴到word文档中,原来一直截图很麻烦,所以找到以下方法. 思想:问题比答案更重要!你能想到问题,才知道去百度搜索. 一.打开网站 http://www.p ...

- 看完小白也会使用,Android投屏神器scrcpy详细教程

楔子 做为一个软件测试工程师,在使用手机测试的时候,缺陷附件想附上截图.视频,需要从手机把图片.视频发送到拷贝或发送到电脑,非常麻烦. 所以想到使用投屏软件,把手机的屏幕投屏到电脑,便可以直接在电脑上 ...

- 做PPT总是很难找到好看、有质感的图片,怎么办?

1.制作PPT时,要想提升整体质感,就需要插入一些图片.当你进入到这个阶段,就意味着你剩下用来做PPT的时间,可能比较紧张了.所以,你的重中之重是,在最短的时间内找到合适的照片. 2.想快速找到好看. ...

- php curl 发送post请求

PHP curl_init函数 resource curl_init ([ string $url = NULL ] ) 初始化一个新的会话,返回一个cURL句柄,供curl_setopt(), cu ...

- 案例分享 | dubbo 2.7.12 bug导致线上故障

本文已收录 https://github.com/lkxiaolou/lkxiaolou 欢迎star.搜索关注微信公众号"捉虫大师",后端技术分享,架构设计.性能优化.源码阅读. ...

- CF932G-Palindrome Partition【PAM】

正题 题目链接:https://www.luogu.com.cn/problem/CF932G 题目大意 给出一个长度为\(n\)的字符串,将其分为\(k\)段(\(k\)为任意偶数),记为\(p\) ...

- 关于spring boot+maven项目大面积报红

有时候我们使用git拉取代码,首先代码本身是没有任何问题的,但我们拉取的代码却大面积报红,模块间的类显示无法加载上方导进来的包一片灰, 代码部分大面积报红,在代码可以确定没问题的情况下,可这样操作: ...