FPGA最小系统分析与电路设计

《FPGA最小系统分析与电路设计》

部分节选自《FPGA应用开发入门与典型.pdf 》

FPGA最小系统包括:FPGA芯片、下载电路、外部时钟、复位电路和电源。

如果使用NIOS II软嵌入式处理器还要包括SDRAM和Flash。

)配置管脚

MSEL[1..0]:用于选择配置模式,FPGA有多种配置模式,如主动、被动、

快速、正常、串行、并行等,以此管脚进行选择;

DATA0:FPGA串行数据输入,连接置配置芯片的串行数据输出管脚;

DCLK:FPGA串行时钟输出,为配置器件提供串行时钟;

nCSO(I/O):FPGA片选信号输出,连接至配置器件的nCS管脚;

ASDO(I/O):FPGA串行数据输出,连接至配置器件的ASDI管脚;

nCEO:下载链器件使能输出,在一条下载链种,当一个器件配置完成后,

此信号使能下一个器件开始进行配置。下载链的最后一个器件的nCEO应

悬空。

nCE:下载链器件使能输入,连接至上一个器件的nCEO,下载链的第一个

器件的nCE接地。

nCONFIG:用户配置模式起始信号;

nSTATUS:配置状态信号;

CONF_DONE:配置结束信号。

)电源引脚

VCCINT:内核电压,与工艺有关,例如130nm工艺为1.5V,90nm工艺为1.2V;

VCCIO:端口电压,一般为3.3V,也可以选择为5V、1.8V、1.5V;

VREF:参考电压;

GND:信号地。

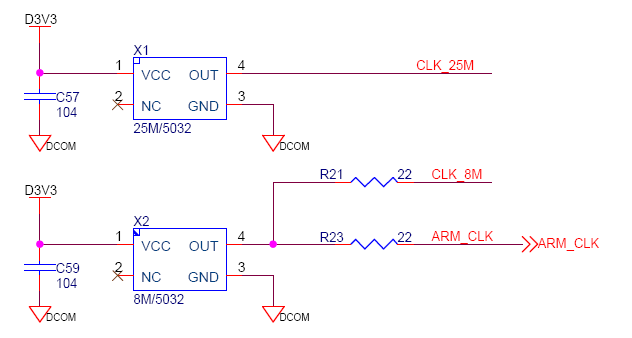

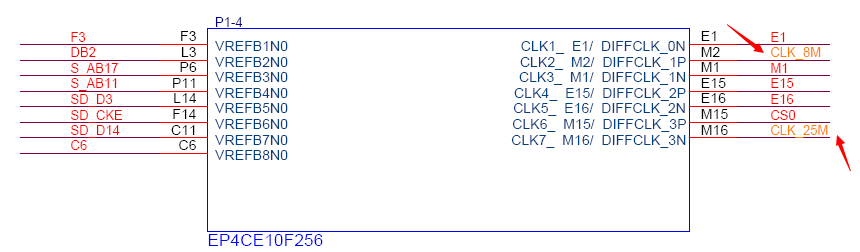

)时钟管脚

VCC_PLL:锁相环管脚电压,直接连VCCIO。

VCCA_PLL:锁相环模拟电压,一般通过滤波器连到VCCINT上。

GNDA_PLL:锁相环模拟地。

GNDD_PLL:锁相环数字地。

CLKnum(LVDSCLKnump):锁相环时钟输入,支持LVDS时钟输入,p接正端,num

表示PLL序号。

CLKnum(LVDSCLKnumn):锁相环时钟输入,支持LVDS时钟输入,n接负端,num

表示PLL序号。

PLLnum_OUTp(I/O):锁相环时钟输出,支持LVDS时钟输入,p接正端,num

表示PLL序号。

PLLnum_OUTn(I/O):锁相环时钟输出,支持LVDS时钟输入,n接正端,num

表示PLL序号。

)JTAG模式与AS模式

FPGA是SRAM型结构,本身不能固话程序。因此FPGA需要一片Flash结构的配置

芯片来存储逻辑配置信息,用于上电配置。

以Altera公司的FPGA为例,配置芯片分为串行(EPCSx系列)和并行(EPCx系列)

其中EPCx为老款配置芯片,体积大,价格高,现在常用EPCSx系列芯片。

JTAG模式是直接将程序下载到FPGA芯片上运行,可以无限擦写,AS模式是将程序

下载到编程配置芯片上,然后再配置FPGA。

)高速SDRAM

SDRAM可作为软嵌入式系统的(NIOS II)的程序运行空间,或者作为大量数据的缓

冲区。SDRAM是通用的存储设备,只要容量和数据位宽相同,不同公司生产的芯片

都是兼容的。

常用的有HY57V系列、三星K4S系列和美光MT48LC系列。

)电源设计:

AMS11117可以提供1A电流,线性电源(适用于144管脚以下、5万逻辑门以

下的FPGA)。

AS2830(或LT1085/6)可以提供3A电流,线性电源(适用于240管脚以下,

30万逻辑门以下的FPGA)。

TPS54350可以提供3A电流,开关电源(适用于大封装大规模的高端FPGA)。

)硬件调试方法

(1)先焊接电源部分,使用万用表测试,排除电源短路等情况后,上电测

试电压是否正确。

(2)然后焊接FPGA及其相关的下载电路,排除引脚粘连,再次测了电源地

之间是否有短路现象,上电测试电压是否正确,然后将手排除静电后触摸

FPGA有无发烫现象。如果出现FPGA发烫现象,一般是出现总线冲突的现象。

这种情况下需要检查外围总线是否出现竞争问题,通常是多片存储器片选

信号同时选通造成。

(3)以上步骤通过后,连接JTAG,上电运行,打开Quartus II,并打开

Programmer,点击Auto DEtect看能否检测到FPGA。

(4)焊接时钟电路、复位电路,并向FPGA下载一个程序,检查是否正常工作。

普及下 来自网友COM张 http://group.chinaaet.com/116/5263

刚学FPGA,谁能给俺解释一下SDRAM ,SRAM ,FLASH在FPGA中起的作用?最好能详细点~谢谢啦

在FPGA开发板上除了内部onchip memory,都有几种不同的存储器,比如SDRAM,SRAM,FLASH,EPCS。

1.EPCS

FPGA只是一个装载软核配置信息的一个工具,它是基于SRAM的查找表,上电的时候需要重新配置,因此一定需要一个配置芯片。一般来说Altera公司Cyclone或者CycloneII系列FPGA相应的配置器件会选择EPCS系列串行FLASH。一般使用AS模式下载EPCS系列器件。但有时候可能遇到AS模式不能成功下载的案例,原理图以及PCB板都是按照推荐电路设计,这时候我们可以通过Flash Loader检验EPCS器件是否良好。即通过JTAG方式下载EPCS系列器件。如果这种方式还是不能进行正确的AS模式的下载的话,可能EPCS器件本身已经不能正常工作了,此时可以建议更换配置芯片了。

在AS模式下,由目标FPGA来主动输出控制和同步信号(包括配置始终)给Altera专用的串行配置芯片EPCS*。

2.FLASH

属于EEPROM(电擦除可编程只读存储器),一种不挥发性(Non-Volatile )内存,在没有电流供应的条件下也能够长久地保持数据,其存储特性相当于硬盘,这项特性正是闪存得以成为各类便携型数字设备的存储介质的基础。

在FPGA开发板中一般用来存储应用程序(C程序等)。用户可以将程序或用户数据烧写入Flash,可以通过NiosII IDE中提供的工具“Flash Programmer”来实现,非常方便,当然也可以自己写代码来将数据烧写入Flash。

3.SDRAM

SDRAM是多Bank结构,例如在一个具有两个Bank的SDRAM的模组中,其中一个Bank在进行预充电期间,另一个Bank却马上可以被读取,这样当进行一次读取后,又马上去读取已经预充电Bank的数据时,就无需等待而是可以直接读取了。这也就大大提高了存储器的访问速度。为了实现这个功能,SDRAM需要增加对多个Bank的管理,实现控制其中的Bank进行预充电。在一个具有两个以上Bank的SDRAM中,一般会多一根叫做BAn的引脚,用来实现在多个Bank之间的选择。在FPGA开发板中一般作为NIOS 处理器的RAM和程序运行空间。

4.SRAM

一个SRAM中的位单元通常由4~6只晶体管组成,利用双稳态触发器来保存信息,当这个位单元被赋予0或1的状态之后,它会保持这个状态直到下次被赋予新的状态,或者断电之后才会更改或消失。SRAM的速度相对比较快,而且比较省电,但是存储1位的信息需要4~6只晶体管,制造成本较高。

SRAM也有它的缺点,即它的集成度较低,相同容量的DRAM内存可以设计为较小的体积,但是SRAM却需要很大的体积。

FPGA最小系统分析与电路设计的更多相关文章

- FPGA最小系统设计

以EP4CE6E22I7为例,设计FPGA最小系统. 程序存储设计 一般使用EPCS4I8N: FPGA_DATA0:13 FPGA_DCLK :12 FPGA_nCS:8 ASDO:6 时钟 待续

- 系统分析与设计个人作业:WordCount

本次作业gitee地址:https://gitee.com/ackary/WordCount 一.项目简介 1.基础功能 基础功能部分主要实现的功能是统计一个程序设计语言源文件的字符数.单词数.行数, ...

- SATA主机协议的FPGA实现之物理层设计

SATA主机协议的FPGA实现之物理层设计 接上一篇文章,这里讲解SATA主机协议的物理层的实现过程. 下图是标准SATA协议文档中给出的物理层结构.可以看到它包含控制模块.时钟数据提取单元.同步 ...

- 文献综述十六:基于UML的中小型超市管理系统分析与设计

一.基本信息 标题:基于UML的中小型超市管理系统分析与设计 时间:2016 出版源:Journal of Xiangnan University 文件分类:uml技术系统的研究 二.研究背景 开发一 ...

- 基于FPGA的HDMI显示设计(三)

上一篇:基于FPGA的VGA显示设计(二) 10月10日 ~ 20日期间实习,令我万万没想到的是实习题目是 “便携式高清电视显示屏测试系统原型设计” 也就是 “基于FPGA的视频显示”. 实习要求用 ...

- 基于FPGA的VGA显示设计(二)

上一篇:基于FPGA的VGA显示设计(一) 参照 CrazyBingo 的 基于FPGA的VGA可移植模块终极设计代码 的工程代码风格,模块化处理了上一篇的代码,并增加了一点其它图形. 顶层 ...

- RQNOJ 622 最小重量机器设计问题:dp

题目链接:https://www.rqnoj.cn/problem/622 题意: 一个机器由n个部件组成,每一种部件都可以从m个不同的供应商处购得. w[i][j]是从供应商j处购得的部件i的重量, ...

- 干货分享,FPGA硬件系统的设计技巧

PGA的硬件设计不同于DSP和ARM系统,比较灵活和自由.只要设计好专用管脚的电路,通用I/O的连接可以自己定义.因此,FPGA的电路设计中会有一些特殊的技巧可以参考. 1. FPGA管脚兼容性设计 ...

- 系统分析与设计lesson6

| 分类 作业 | 1.用例建模 a. 阅读 Asg_RH 文档,绘制用例图. 按 Task1 要求,请使用工具 UMLet,截图格式务必是 png 并控制尺寸 b. 选择你熟悉的定旅馆在线服务系统 ...

随机推荐

- kernel里面出现了类似isegfault at xxx ip 错误

今天同时碰到了错误如下,但是没有core,当时通过代码审查解决了问题,后续再查的时候发现可以使用addr2line 查找代码行, segfault at 10000 ip b7f0f48a sp bf ...

- hdu Inverting Cups

这题需要分类讨论: 第一种情况: n为奇数m为偶数的情况无解,因为m为偶数,每次翻转将把从正面翻到反面的个数x减去从反面翻到正面的个数y,得到的数必定为偶数.因为x+y为偶数,x-y也为偶数.而总个数 ...

- dpi,ppi,dip,dp,px和sp

一 基本概念 1. dpi (dots per inch)每英寸多少点:ppi( Pixel per inch),每英寸像素数.针对显示器的设计时,dpi=ppi. 2. dip (device in ...

- 《GK101任意波发生器》升级固件发布(版本:1.0.2build955)

一.固件说明: 硬件版本:0,logic.3 固件版本:1.0.2.build955 编译日期:2015-12-14 ====================================== 二. ...

- 文件上传(springMVC+ckeditor)

1.首先添加springMVC文件上传的jar commons-fileupload-1.2.2.jar和commons-io-2.0.1.jar (maven项目可以使用 <dependenc ...

- java数组排序问题:array.sort()是从小到大排序,那么如何从大到小排序?

别告诉我从i=a.length开始打印然后i--!因为数组没变啊,只是打印顺序变了.有木有啥别的方法,除了冒泡插入选择.. nteger [] array=new Integer[]{1,2,3,4, ...

- 2016.09.14,英语,《Using English at Work》全书笔记

半个月时间,听完了ESLPod出品的<Using English at Work>,笔记和自己听的时候的备注列在下面.准备把每个语音里的快速阅读部分截取出来,放在手机里反复听. 下一阶段把 ...

- Tortoise SVN 不显示 Log Message 具体信息的解决方法

今天加入新项目,在 Tortoise SVN Check out 完项目之后,发现右键 show log 不显示 Log Message 的具体信息: 因为是新加入的项目,问了原来负责这个项目的同事, ...

- Web 在线文件管理器学习笔记与总结(11)获取文件夹信息 (12)返回上一级操作

(11)获取文件夹信息 文件夹没有修改操作. index.php: <?php require 'dir.func.php'; require 'file.func.php'; require ...

- 第二章、 Linux 如何学习

第二章. Linux 如何学习 最近更新日期:2009/08/06 1. Linux当前的应用角色 1.1 企业环境的利用 1.2 个人环境的使用 Linux当前的应用角色 在第一章Linux是什么当 ...