S5PV210_时钟系统

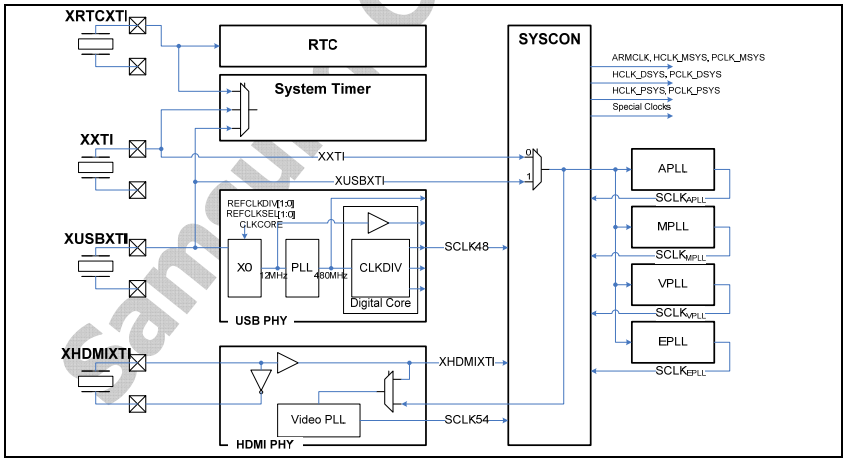

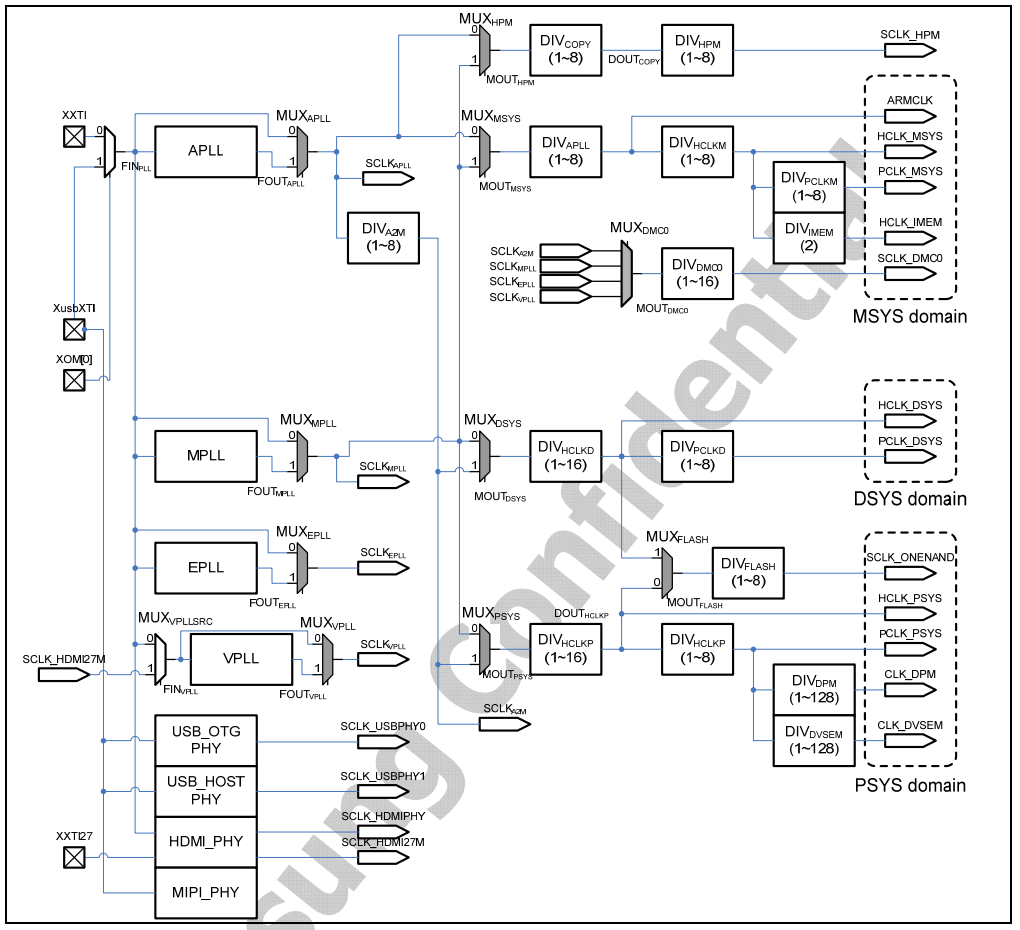

1、S5PV210的时钟获得:外部晶振+内部时钟发生器+内部PLL产生高频时钟+内部分频器分频

S5PV210外部有4个W晶振接口,可以根据需要来决定在哪里接晶振。接了晶振之后上电相应的模块就能产生振荡,产生原始时钟。原始时钟经过一系列的筛选开关进入相应的PLL电路生成倍频后的高频时钟。高频时钟再经过分频到达芯片内部各模块上。(有些模块,譬如串口内部还有进一步的分频器进行再次分频使用)

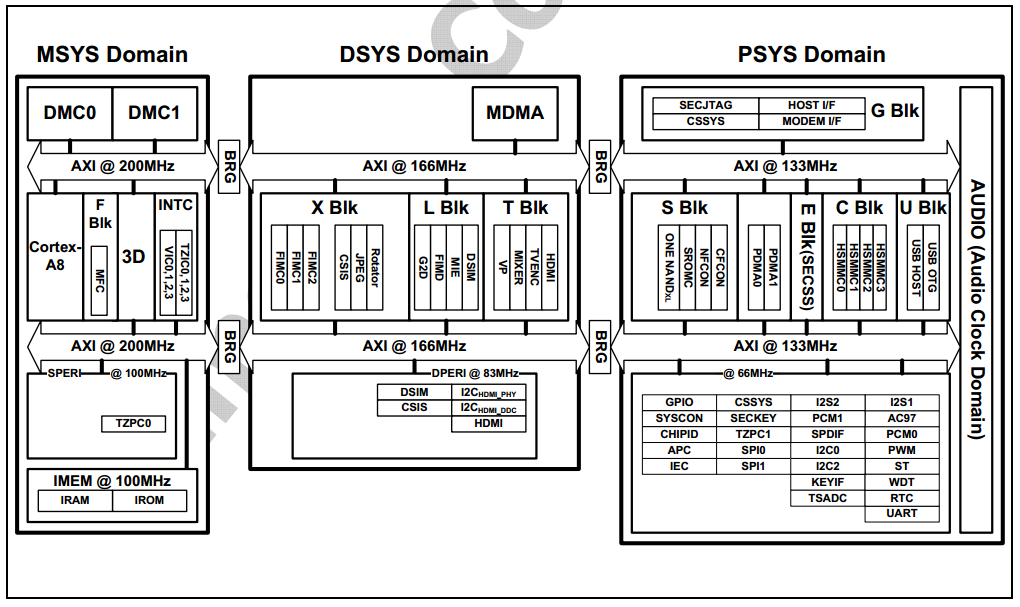

2、时钟域:MSYS、DSYS、PSYS

MSYS(main system):CPU(Cortex-A8内核)、DRAM控制器(DMC0和DMC1)、SRAM(IRAM&IROM)、INTC、SPERI(configuration inerface)······

ARMCLK: 给cpu内核工作的时钟,也就是所谓的主频。

HCLK_MSYS: MSYS域的高频时钟,给DMC0和DMC1使用

PCLK_MSYS: MSYS域的低频时钟

HCLK_IMEM:给iROM和iRAM(合称iMEM)使用

DSYS(display system): 都是和视频显示、编解码等有关的模块(FIMC、FIMD、JPEG)

HCLK_DSYS:DSYS域的高频时钟

PCLK_DSYS:DSYS域的低频时钟

PSYS(peripheral system): 和内部的各种外设时钟有关,譬如串口、SD接口、I2C、AC97、USB等

HCLK_PSYS:PSYS域的高频时钟

PCLK_PSYS:PSYS域的低频时钟

3、关于PLL(包括APLL \ MPLL \ EPLL \ VPLL)

APLL:Cortex-A8内核 MSYS域

MPLL&EPLL:DSYS PSYS

VPLL:Video视频相关模块

4、时钟设置的关键寄存器

xPLL_LOCK 控制PLL锁定周期

xPLL_CON 打开/关闭PLL电路,设置PLL的倍频参数,查看PLL锁定状态

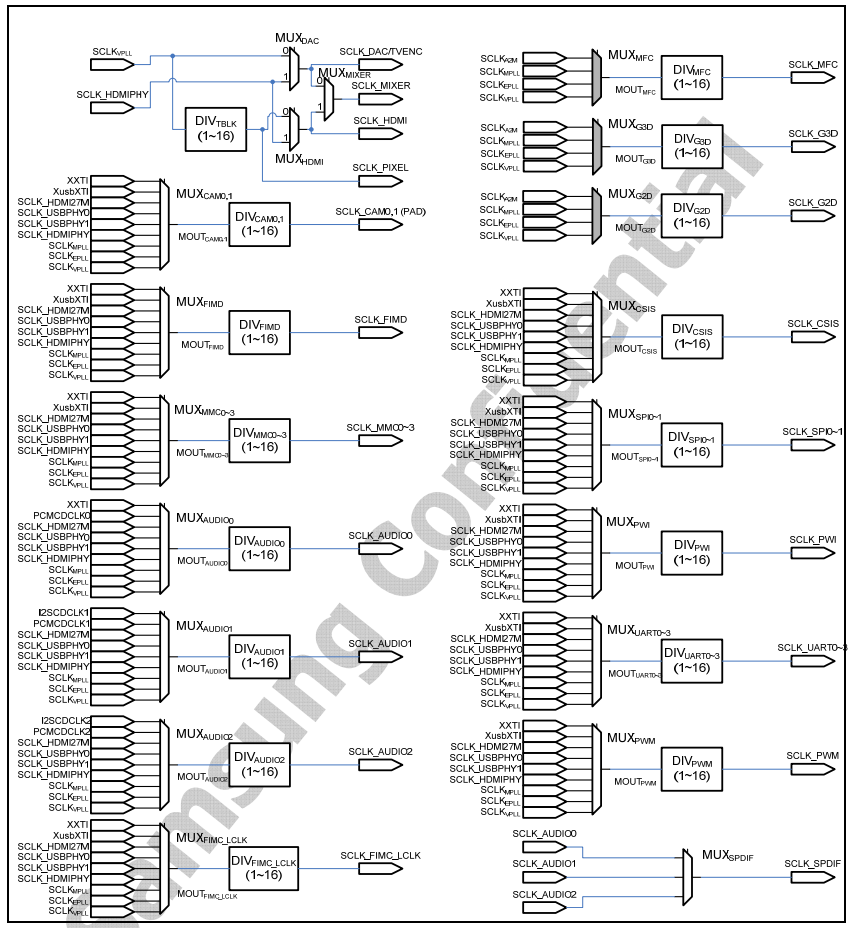

CLK_SRCn(n:0~6) 设置时钟来源,对应时钟框图中的MUX开关

CLK_SRC_MASK 决定MUX开关n选1后是否能继续通过

CLK_DIV 各模块的分频器参数配置

CLK_GATE_x 类似于CLK_SRC_MASK,对时钟进行开关控制

CLK_DIV_STATn、CLK_MUX_STATn 查看DIV和MUX的状态(已经完成还是在进行中)

5、代码设置时钟逻辑步骤:

(1)先选择不使用PLL。让外部24MHz原始时钟直接过去,绕过APLL那条路

ldr r0, =ELFIN_CLOCK_POWER_BASE

//设置各种时钟开关,暂时不使用PLL

ldr r1, =0x0

//CLK_SRC bit[0]就是APLL_SEL,(APLL_SEL:control MUXAPLL(0:FINPLL,1:FOUTAPLL))

str r1, [r0, #CLK_SRC0_OFFSET]

(2)设置锁定时间。默认值为0x0FFF,保险起见我们设置为0xFFFF

//设置锁定时间,使用默认值即可

// 设置PLL后,时钟从Fin提升到目标频率时,需要一定的时间,即锁定时间

ldr r1, =0x0000FFFF

str r1, [r0, #APLL_LOCK_OFFSET]

str r1, [r0, #MPLL_LOCK_OFFSET]

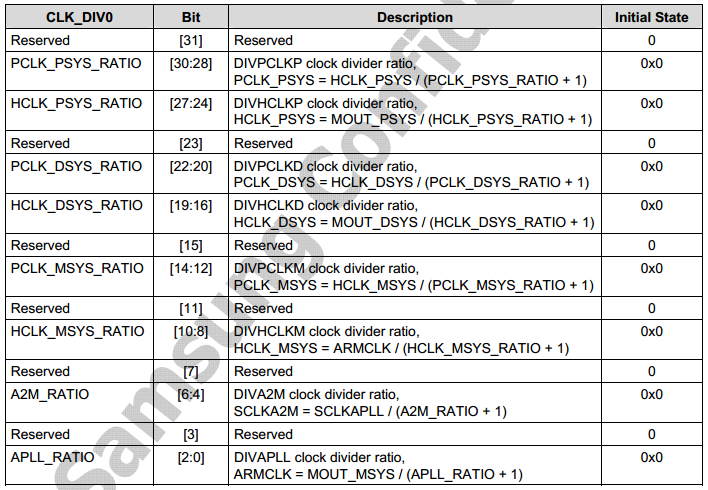

(3)设置分频系统,由PLL出来的最高时钟如何分频得到各个分时钟

//设置分频

// 清bit[0~31]

ldr r1, [r0, #CLK_DIV0_OFFSET]

ldr r2, =CLK_DIV0_MASK

bic r1, r1, r2

ldr r2, =0x14131440

orr r1, r1, r2

str r1, [r0, #CLK_DIV0_OFFSET]

0x14131440的含义:

PCLK_PSYS = HCLK_PSYS / 2

HCLK_PSYS = MOUT_PSYS / 5

PCLK_DSYS = HCLK_DSYS / 2

HCLK_DSYS = MOUT_DSYS / 4

·······

HCLK_MSYS = ARMCLK / 5

ARMCLK = MOUT_MSYS / 1

(4)设置PLL,主要是设置PLL的倍频系统,决定由输入端24MHz的原始频率可以得到多大的输出频率。我们按照默认设置值设置输出为ARMCLK为1GHz

#define set_pll(mdiv, pdiv, sdiv) (1<<31 | mdiv<<16 | pdiv<<8 | sdiv)

#define APLL_VAL set_pll(APLL_MDIV,APLL_PDIV,APLL_SDIV)

#define MPLL_VAL set_pll(MPLL_MDIV,MPLL_PDIV,MPLL_SDIV) //设置PLL

// FOUT = MDIV*FIN/(PDIV*2^(SDIV-1))=0x7d*24/(0x3*2^(1-1))=1000 MHz

ldr r1, =APLL_VAL

str r1, [r0, #APLL_CON0_OFFSET]

// FOUT = MDIV*FIN/(PDIV*2^SDIV)=0x29b*24/(0xc*2^1)= 667 MHz

ldr r1, =MPLL_VAL

str r1, [r0, #MPLL_CON_OFFSET]

(5)打开PLL。前面4步已经设置好了所有的开关和分频系数,该步骤打开PLL后PLL开始工作,锁定频率后输出,然后经过分频得到各个频率。

//设置各种时钟开关,使用PLL

ldr r1, [r0, #CLK_SRC0_OFFSET]

ldr r2, =0x10001111

orr r1, r1, r2

str r1, [r0, #CLK_SRC0_OFFSET]

6、汇编代码

// 时钟控制器基地址

#define ELFIN_CLOCK_POWER_BASE 0xE0100000 // 时钟相关的寄存器相对时钟控制器基地址的偏移值

#define APLL_LOCK_OFFSET 0x00

#define MPLL_LOCK_OFFSET 0x08 #define APLL_CON0_OFFSET 0x100

#define APLL_CON1_OFFSET 0x104

#define MPLL_CON_OFFSET 0x108 #define CLK_SRC0_OFFSET 0x200

#define CLK_SRC1_OFFSET 0x204

#define CLK_SRC2_OFFSET 0x208

#define CLK_SRC3_OFFSET 0x20c

#define CLK_SRC4_OFFSET 0x210

#define CLK_SRC5_OFFSET 0x214

#define CLK_SRC6_OFFSET 0x218

#define CLK_SRC_MASK0_OFFSET 0x280

#define CLK_SRC_MASK1_OFFSET 0x284 #define CLK_DIV0_OFFSET 0x300

#define CLK_DIV1_OFFSET 0x304

#define CLK_DIV2_OFFSET 0x308

#define CLK_DIV3_OFFSET 0x30c

#define CLK_DIV4_OFFSET 0x310

#define CLK_DIV5_OFFSET 0x314

#define CLK_DIV6_OFFSET 0x318

#define CLK_DIV7_OFFSET 0x31c #define CLK_DIV0_MASK 0x7fffffff // M、P、S的配置值都是查数据手册中典型时钟配置值的推荐配置得来的。

#define APLL_MDIV 0x7d //

#define APLL_PDIV 0x3

#define APLL_SDIV 0x1 #define MPLL_MDIV 0x29b //

#define MPLL_PDIV 0xc

#define MPLL_SDIV 0x1 #define set_pll(mdiv, pdiv, sdiv) (1<<31 | mdiv<<16 | pdiv<<8 | sdiv)

#define APLL_VAL set_pll(APLL_MDIV,APLL_PDIV,APLL_SDIV)

#define MPLL_VAL set_pll(MPLL_MDIV,MPLL_PDIV,MPLL_SDIV) .global clock_init

clock_init:

ldr r0, =ELFIN_CLOCK_POWER_BASE // 1 设置各种时钟开关,暂时不使用PLL

ldr r1, =0x0

//CLK_SRC bit[0]就是APLL_SEL,(APLL_SEL:control MUXAPLL(0:FINPLL,1:FOUTAPLL))

str r1, [r0, #CLK_SRC0_OFFSET] // 2 设置锁定时间,使用默认值即可

// 设置PLL后,时钟从Fin提升到目标频率时,需要一定的时间,即锁定时间

ldr r1, =0x0000FFFF

str r1, [r0, #APLL_LOCK_OFFSET]

str r1, [r0, #MPLL_LOCK_OFFSET] // 3 设置分频

// 清bit[0~31]

ldr r1, [r0, #CLK_DIV0_OFFSET]

ldr r2, =CLK_DIV0_MASK

bic r1, r1, r2

ldr r2, =0x14131440

orr r1, r1, r2

str r1, [r0, #CLK_DIV0_OFFSET] // 4 设置PLL

// FOUT = MDIV*FIN/(PDIV*2^(SDIV-1))=0x7d*24/(0x3*2^(1-1))=1000 MHz

ldr r1, =APLL_VAL

str r1, [r0, #APLL_CON0_OFFSET]

// FOUT = MDIV*FIN/(PDIV*2^SDIV)=0x29b*24/(0xc*2^1)= 667 MHz

ldr r1, =MPLL_VAL

str r1, [r0, #MPLL_CON_OFFSET] // 5 设置各种时钟开关,使用PLL

ldr r1, [r0, #CLK_SRC0_OFFSET]

ldr r2, =0x10001111

orr r1, r1, r2

str r1, [r0, #CLK_SRC0_OFFSET] mov pc, lr

7、C语言代码

// 时钟控制器基地址

#define ELFIN_CLOCK_POWER_BASE 0xE0100000 // 时钟相关的寄存器相对时钟控制器基地址的偏移值

#define APLL_LOCK_OFFSET 0x00

#define MPLL_LOCK_OFFSET 0x08 #define APLL_CON0_OFFSET 0x100

#define APLL_CON1_OFFSET 0x104

#define MPLL_CON_OFFSET 0x108 #define CLK_SRC0_OFFSET 0x200

#define CLK_SRC1_OFFSET 0x204

#define CLK_SRC2_OFFSET 0x208

#define CLK_SRC3_OFFSET 0x20c

#define CLK_SRC4_OFFSET 0x210

#define CLK_SRC5_OFFSET 0x214

#define CLK_SRC6_OFFSET 0x218

#define CLK_SRC_MASK0_OFFSET 0x280

#define CLK_SRC_MASK1_OFFSET 0x284 #define CLK_DIV0_OFFSET 0x300

#define CLK_DIV1_OFFSET 0x304

#define CLK_DIV2_OFFSET 0x308

#define CLK_DIV3_OFFSET 0x30c

#define CLK_DIV4_OFFSET 0x310

#define CLK_DIV5_OFFSET 0x314

#define CLK_DIV6_OFFSET 0x318

#define CLK_DIV7_OFFSET 0x31c #define CLK_DIV0_MASK 0x7fffffff // M、P、S的配置值都是查数据手册中典型时钟配置值的推荐配置得来的。

#define APLL_MDIV 0x7d //

#define APLL_PDIV 0x3

#define APLL_SDIV 0x1 #define MPLL_MDIV 0x29b //

#define MPLL_PDIV 0xc

#define MPLL_SDIV 0x1 #define set_pll(mdiv, pdiv, sdiv) (1<<31 | mdiv<<16 | pdiv<<8 | sdiv)

#define APLL_VAL set_pll(APLL_MDIV,APLL_PDIV,APLL_SDIV)

#define MPLL_VAL set_pll(MPLL_MDIV,MPLL_PDIV,MPLL_SDIV) #define REG_CLK_SRC0 (ELFIN_CLOCK_POWER_BASE + CLK_SRC0_OFFSET)

#define REG_APLL_LOCK (ELFIN_CLOCK_POWER_BASE + APLL_LOCK_OFFSET)

#define REG_MPLL_LOCK (ELFIN_CLOCK_POWER_BASE + MPLL_LOCK_OFFSET)

#define REG_CLK_DIV0 (ELFIN_CLOCK_POWER_BASE + CLK_DIV0_OFFSET)

#define REG_APLL_CON0 (ELFIN_CLOCK_POWER_BASE + APLL_CON0_OFFSET)

#define REG_MPLL_CON (ELFIN_CLOCK_POWER_BASE + MPLL_CON_OFFSET) #define rREG_CLK_SRC0 (*(volatile unsigned int *)REG_CLK_SRC0)

#define rREG_APLL_LOCK (*(volatile unsigned int *)REG_APLL_LOCK)

#define rREG_MPLL_LOCK (*(volatile unsigned int *)REG_MPLL_LOCK)

#define rREG_CLK_DIV0 (*(volatile unsigned int *)REG_CLK_DIV0)

#define rREG_APLL_CON0 (*(volatile unsigned int *)REG_APLL_CON0)

#define rREG_MPLL_CON (*(volatile unsigned int *)REG_MPLL_CON) void clock_init(void)

{

// 1 设置各种时钟开关,暂时不使用PLL

rREG_CLK_SRC0 = 0x0; // 2 设置锁定时间,使用默认值即可

// 设置PLL后,时钟从Fin提升到目标频率时,需要一定的时间,即锁定时间

rREG_APLL_LOCK = 0x0000ffff;

rREG_MPLL_LOCK = 0x0000ffff; // 3 设置分频

// 清bit[0~31]

rREG_CLK_DIV0 = 0x14131440; // 4 设置PLL

// FOUT = MDIV*FIN/(PDIV*2^(SDIV-1))=0x7d*24/(0x3*2^(1-1))=1000 MHz

rREG_APLL_CON0 = APLL_VAL;

// FOUT = MDIV*FIN/(PDIV*2^SDIV)=0x29b*24/(0xc*2^1)= 667 MHz

rREG_MPLL_CON = MPLL_VAL; // 5 设置各种时钟开关,使用PLL

rREG_CLK_SRC0 = 0x10001111;

}

S5PV210_时钟系统的更多相关文章

- 9.S5PV210的时钟系统

1.时钟域:MSYS.DSYS.PSYS(1)因为S5PV210的时钟体系比较复杂,内部外设模块太多,因此把整个内部的时钟划分为3大块,叫做3个域.(2)MSYS: CPU(Cortex-A8内核). ...

- STM32时钟系统

一.在STM32中,有五个时钟源,为HSI.HSE.LSI.LSE.PLL. ①HSI是高速内部时钟,RC振荡器,频率为8MHz. ②HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率 ...

- 总结:S5PV210时钟系统

在数据手册<S5PV210_UM_REV1.1>中的section 02_system/3 CLOCK CONTROLLER(354页) 一.时钟域 在S5PV210的SoC中,时钟系 ...

- STM8时钟系统详解

就我个人看来,研究一块单片机,分为新手和老手两种模式,新人迫切的想先用,你得告诉他们怎么样最快的写出一个能跑起来的程序,告诉他们每一个外设的使用方式,老手不同,用的单片机多了外设对于他们而言没太多好奇 ...

- S3C2440时钟系统详解

在讲述系统时钟之前,因为这些设备都是挂靠在系统时钟上的,所以必须先说系统时钟,S3C2440的时钟系统如下 外部时钟源分两种,晶振或者外部频率,由om3-2选择,时钟电路根据两种选择也有两种 我们来分 ...

- Stm32复习之时钟系统

地点:南图 这部分的内容是整个STM32学习知识的核心,不管是什么微控制器处理器,时钟系统都是其核心类似于人之心脏,因此学好理解这一章节至关重要. 为了便于理解这一系统,将从以下几个层次来讲.(忘了是 ...

- 关于STM32时钟系统

初学STM32,感觉最蛋疼的是它的时钟系统,每次看到它的那个时钟树就有点晕,虽然看了很多这方面的资料,甚至也已经写过很多STM32的模块代码,做过一些小项目,但一直还是对这一块模模糊糊,似懂非懂,所以 ...

- IDC:时钟系统

ylbtech-IDC:时钟系统 主要应用于要求有统一时间进行生产,调度的单位如:电力,机场.轻轨.地铁.体育场馆.酒店.医院.部队.油田.水利工程等领域.大区域时钟系统主要由母钟和多台子钟构成. 1 ...

- 【STM32H7教程】第14章 STM32H7的电源,复位和时钟系统

完整教程下载地址:http://forum.armfly.com/forum.php?mod=viewthread&tid=86980 第14章 STM32H7的电源,复位和时钟系 ...

随机推荐

- 让DIV中文字换行显示

1. <style> div { white-space:normal; word-break:break-all; word-wrap:break-word; } </style& ...

- jQuery 插件-(初体验一)

1.jquery有2个扩展方法: jquery.fn.extend=jquery.prototype.extend jquery.extend (两者的区别放在后面文章说) 2.具体实例结构: //创 ...

- Android学习路线

第一阶段:Java面向对象编程 1.Java基本数据类型与表达式,分支循环. 2.String和StringBuffer的使用.正则表达式. 3.面向对象的抽象,封装,继承,多态,类与对象,对象初始化 ...

- angular2系列教程(五)Structural directives、再谈组件生命周期

今天,我们要讲的是structural directives和组件生命周期这两个知识点.structural directives顾名思义就是改变dom结构的指令.著名的内建结构指令有 ngIf, n ...

- C++服务器开发之基于对象的编程风格

Thread.h #ifndef _THREAD_H_ #define _THREAD_H_ #include <pthread.h> #include <boost/functio ...

- 灵活可扩展的工作流管理平台Airflow

1. 引言 Airflow是Airbnb开源的一个用Python写就的工作流管理平台(workflow management platform).在前一篇文章中,介绍了如何用Crontab管理数据流, ...

- Uploadify 结合 Web API 2 上传问题

最近使用jQuery.Uploadify和Web API配合来做上传,碰到问题,还木有办法解决,记录一下: 环境:jQuery 1.10.2,Uploadify 3.2.1,SWFObject 2.2 ...

- SQL Server 2012 清理日志 截断日志的方法

MEDIA数据库名 ALTER DATABASE MEDIA SET RECOVERY SIMPLE WITH NO_WAIT ALTER DATABASE MEDIA SET RECOVERY SI ...

- JavaScript弹窗

警告框: alert("警告信息!"); alert("警告\n信息!"); 确认框: var t=confirm("请确认!"); // ...

- java代码解压zip文件

import java.io.File; import java.io.FileOutputStream; import java.io.IOException; import java.io.Inp ...