Modelsim中的Verilog语言使用

一、建立工程

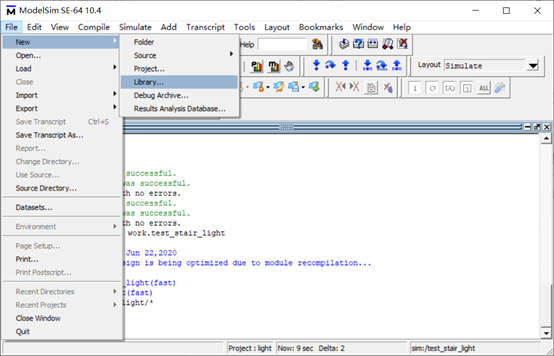

1.在建立工程(project)前,先建立一个工作库(library),一般将这个 library 命名为 work。尤其是第一次运行 modelsim 时,是没有这个“work”的。但我们的 project 一般都是在这个work下面工作的,所以有必要先建立work。

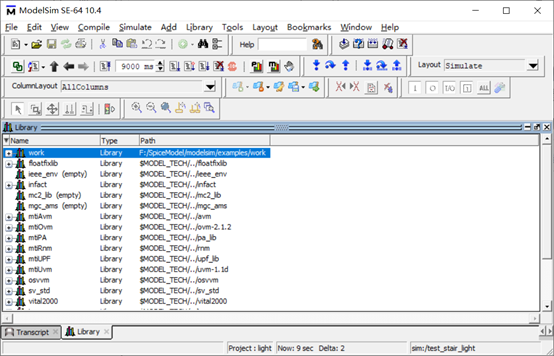

2.点击 library 后会弹出一个对话框,问是否要创建 work,点击 OK。就能看见 work。

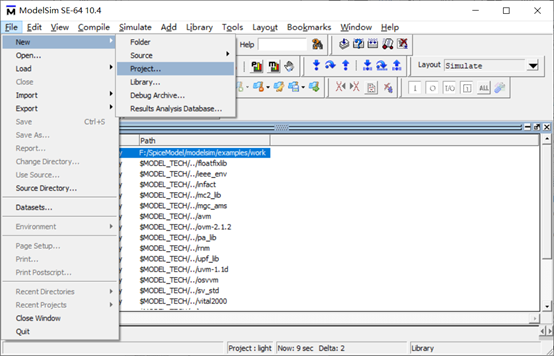

3. 如果在 library 中有 work,就不必执行上一步骤了,直接新建工程。

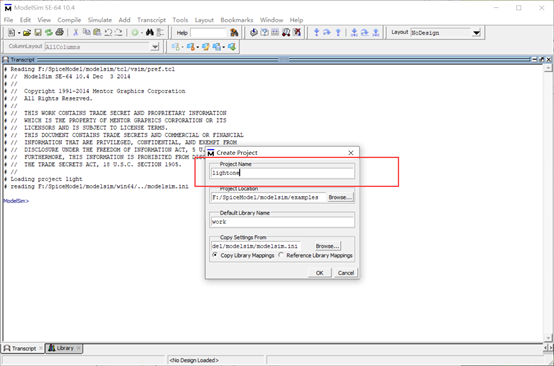

4.点击后会出现

5.在 Project Name 中写入工程的名字,这里我们写一个楼道灯,所以命名lightone,然后点击 OK。会出现

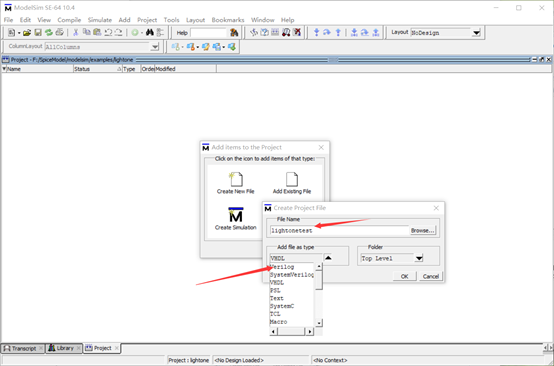

6.由于我是要仿一个自己写的程序,所以这里我们选择 Create New File。

7.在 File Name 中写入文件名(这里的 file name 和刚刚建立的 project name 可以一致也可以不一致)。注意 Add file as type 要选择成 Verilog(默认的是 VHDL),然后 OK。

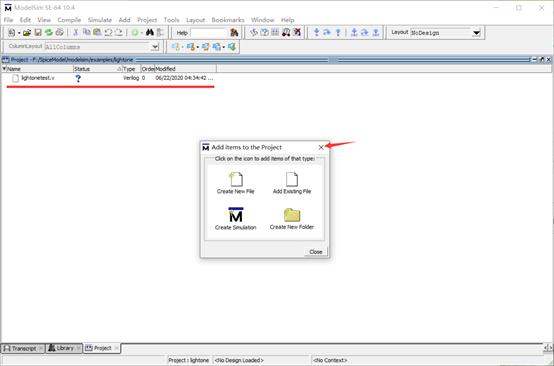

8.发现屏幕中间的那个对话框没有自己消失,我们需要手动关闭它,点close。 并且在project 中出现了一个lightonetest.v的文件,这个就是我们刚刚新建的那个file。这样工程就建立完毕了。

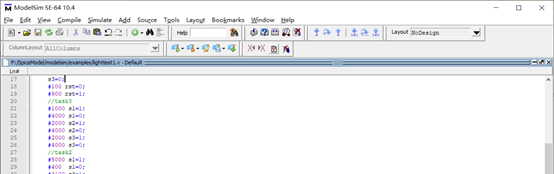

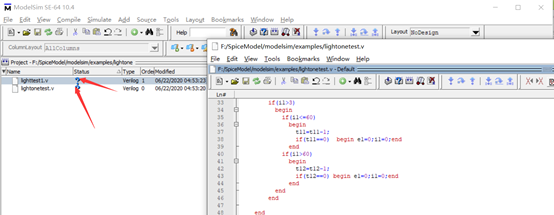

二、书写代码

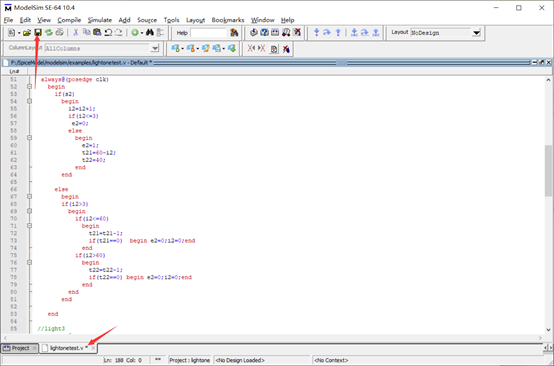

写主程序:双击lightonetest.v 文件会出现程序编辑区,在这个区间里写好自己的程序.

1.这时候记得保存文件,这时,只需要点击保存,就会发现“保存”的图标变成了阴影,这样编译才有效。

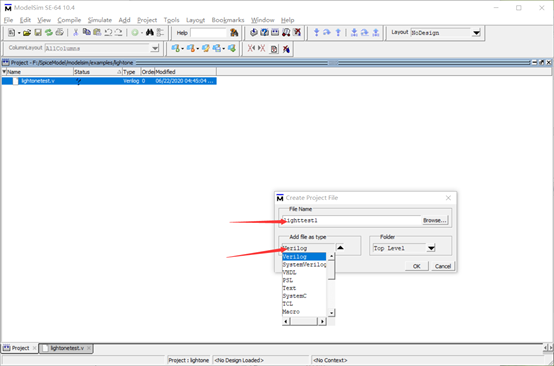

2.写测试程序,每一个主程序(实现我们需要的某种功能的程序),都要配套的编写一个测试程序,为了我们方便检测主程序的功能。

3.再次创建文件

4.书写测试代码

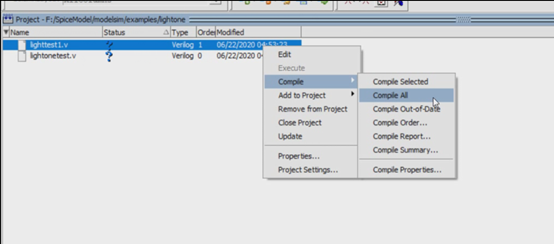

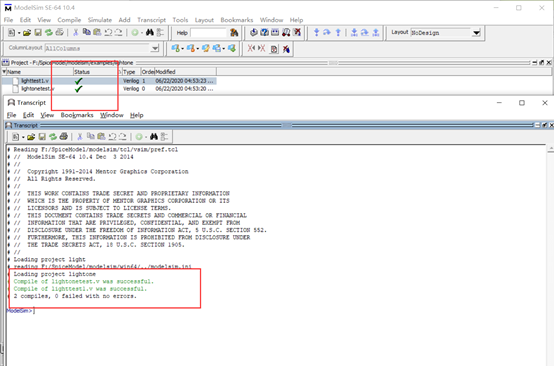

三、编译代码

编译成功后,文件后面的?变成了对勾,并且在最下方的 Transcript栏中出现了 successful字样,说明编译成功,否则会报错,就要回到程序中修改,只有编译成功后,才能往后面进行。

四、软件仿真

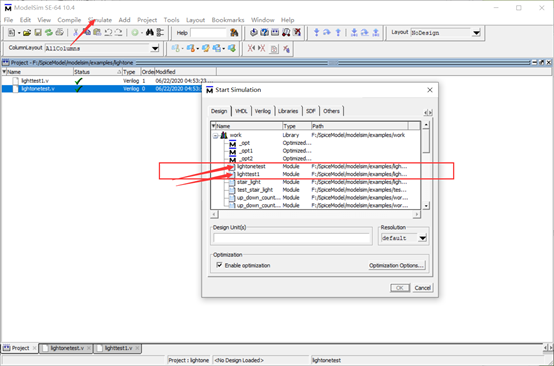

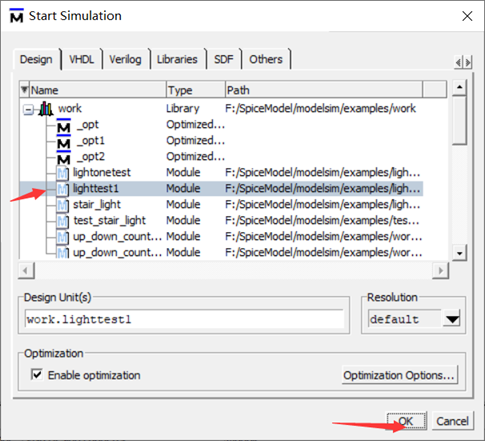

点击屏幕上方的simulate,再点击start simulate,再点击 work 前的“+”号,将其展开,会看到两个文件,文件名就是我们自己写的。

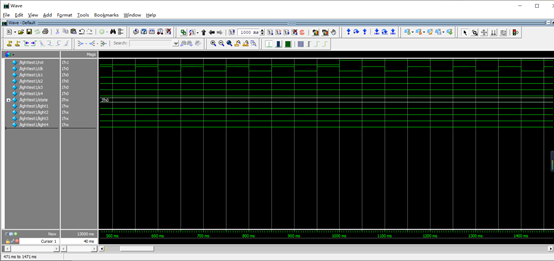

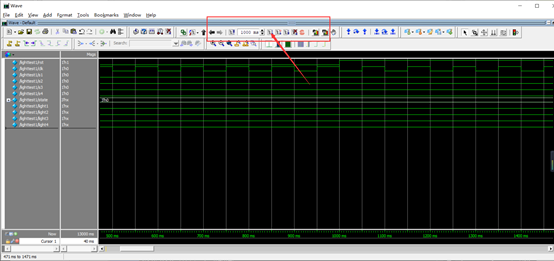

这样,看波形的窗口就会出现,将红色圈圈中的仿真时间步改成 1000ms,然后按旁边的运

行按键,波形就出现了。按住 ctrl 滚动鼠标滑轮可以缩放波形。

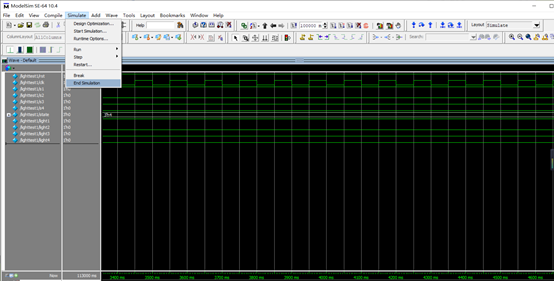

当 modelsim 在仿真中的时候需要停止仿真可以这样手动关闭,以便进行其他操作。

Modelsim中的Verilog语言使用的更多相关文章

- Verilog语言中的系统任务和系统函数

Verilog语言中预先定义了一些任务和函数,用于完成一些特殊的功能,它们被称为系统任务和系统函数,这些函数大多数都是只能在Testbench仿真中使用的,使我们更方便的进行验证. `timescal ...

- 基于MATLAB2016b图形化设计自动生成Verilog语言的积分模块及其应用

在电力电子变流器设备中,常常需要计算发电量,由于电力电子变流器设备一般是高频变流设备,所以发电量的计算几乎时实时功率的积分,此时就会用到一个积分模块.发电量计算的公式如下:Q=∫P. FPGA由于其并 ...

- Verilog语言实现并行(循环冗余码)CRC校验

1 前言 (1) 什么是CRC校验? CRC即循环冗余校验码:是数据通信领域中最常用的一种查错校验码,其特征是信息字段和校验字段的长度可以任意选定.循环冗余检查(CRC)是一种数据传输检错功能, ...

- 87.在ModelSim中添加Xilinx ISE仿真库

在ModelSim中添加Xilinx ISE仿真库 说明: l ModelSim一定要安装在不带空格的目录下,即不要安装在“Program Files”目录下.如作者是安装在D:\softwares\ ...

- 在ModelSim中添加Xilinx仿真库

在ModelSim中添加Xilinx仿真库 说明: l ModelSim一定要安装在不带空格的目录下,即不要安装在“Program Files”目录下.如作者是安装在D:\softwares\Mode ...

- Verilog语言:还真的是人格分裂的语言

人气腹语术师天愿在现场披露了被人偶搭档夺取灵魂的腹语术师将妻子杀害的表演节目.天愿真的陷入了多重人格,命令自己杀害妻子和子的人偶的人格出现了.为了不(让自己)杀害和弟子登川有外遇的妻子,天愿提出委托想 ...

- Verilog 语言 001 --- 入门级 --- 编写一个半加器电路模块

Verilog 语言编写一个 半加器 电路模块 半加器 的电路结构: S = A 异或 B C = A 与 B 1. 程序代码 module h_adder (A, B, SO, CO); input ...

- FPGA基础(verilog语言)——语法篇

verilog语言简介 verilog语言是一种语法类似于c的语言,但是与c语言也有不同之处,比如: 1.verilog语言是并行的,每个always块都是同时执行,而c语言是顺序执行的 2.veri ...

- 从RTL视图到Verilog语言-转可乐豆原创

从RTL视图到Verilog语言 曾经听过某位大牛都说:“当你的学习FPGA到一个境界的时候,你看到的硬件描述语言,将不再是单纯的语言,而是由一个个逻辑门组成的电路图,一旦达到这个境界,方能把代码写到 ...

- quartus和modelsim中使用mif和hex文件

.mif和.hex文件都是Quartus支持的数据文件格式,常被用作内存初始化文件.可是,M odelSim却不支持.mif文件,只支持.hex文件格式,这意味着如果你的设计采用了.mif文件 ,你的 ...

随机推荐

- js右键生成菜单

<!DOCTYPE html> <html lang="en"> <head> <meta charset="UTF-8&quo ...

- AspectRatio、Card 卡片组件

一.Flutter AspectRatio 组件 AspectRatio 的作用是根据设置调整子元素 child 的宽高比. AspectRatio 首先会在布局限制条件允许的范围内尽可能的扩展,wi ...

- git diff如何确定差异所在函数context

问题 在使用git diff 展示c/c++文件修改内容时,除了显示修改上下文外,输出还贴心的展示了修改所在的函数.尽管这个展示并不总是准确,但是能够做到大部分情况下准确也已经相当不错:是不是git内 ...

- oracl ocp认证到底有没有用!!!

从一个网友听说有个OCP专家认证,我们本地也有,要1万3,问题是我想真的学东西而不是为了考证,不知道这个培训能学到多少呀.

- dendrogram

https://ww2.mathworks.cn/help/stats/dendrogram.html

- 获取内存及cpu信息

<dependency> <groupId>com.github.oshi</groupId> <artifactId>oshi-core</ar ...

- Comparator与Comparable实现List中某一对象属性排序

//实体类实现 Comparable接口 进行降序排序 public class TestCompare implements Comparable<TestCompare>{ priva ...

- js判断当值的比较小的背景为红色

<!DOCTYPE html> <html> <head> <title></title> </head> <body&g ...

- 基于Python的简单读卡上位机界面

使用到的模块,pyserial pyqt5 pymysql (我先是实现在命令行下通过串口进行对板子硬件的控制,比如Led ,beep等,在实现检测卡(是否选卡成功),连接卡(验证哪一个扇区),读 ...

- IIS10.0 Web平台安装程序无法安装URL重写工具

Windows10系统的IIS10.0需要安装URL rewrite重写模块2.0,提示"很遗憾,无法安装下列产品",解决方法: win键+R键,运行regedit,打开注册表编辑 ...