分频器的Verilog实现

一、占空比50%的奇数分频

1、实现思路

实现奇数(N)分频,分别用上升沿计数到(N-1)/2,再计数到N-1;用下降沿计数到(N-1)/2,再计数到N-1,得到两个波形,然后把它们相或即可得到N分频。

2、代码

module fp_odd(clk_in,rst_n,cnt_p,cnt_n,clk_p,clk_n,clk_out);

parameter N=;

input clk_in;

input rst_n;

output[:] cnt_p;

output[:] cnt_n;

output clk_p;

output clk_n;

output clk_out; reg[:] cnt_p;

reg[:] cnt_n;

reg clk_p;

reg clk_n; always @(posedge clk_in or negedge rst_n)

begin

if(!rst_n) cnt_p <= ;

else

begin

if(cnt_p == N-) cnt_p <= ;

else cnt_p <= cnt_p + 'b1;

end

end always @(posedge clk_in or negedge rst_n)

begin

if(!rst_n) clk_p <= ;

else

begin

if(cnt_p == (N-)/) clk_p <= !clk_p;

else if(cnt_p == N-) clk_p <= !clk_p;

else clk_p <= clk_p;

end

end always @(negedge clk_in or negedge rst_n)

begin

if(!rst_n) cnt_n <= ;

else

begin

if(cnt_n == N-) cnt_n <= ;

else cnt_n <= cnt_n + 'b1;

end

end always @(negedge clk_in or negedge rst_n)

begin

if(!rst_n) clk_n <= ;

else

begin

if(cnt_n == (N-)/) clk_n <= !clk_n;

else if(cnt_n == N-) clk_n <= !clk_n;

else clk_n <= clk_n;

end

end assign clk_out = clk_p | clk_n; endmodule

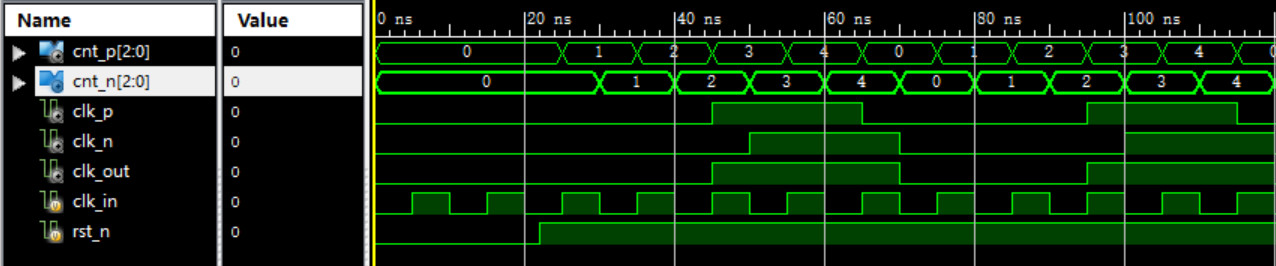

3、仿真波形

分频器的Verilog实现的更多相关文章

- 分频器的verilog设计

笔者最近由于实验室老师的任务安排重新又看了一下分频器的verilog实现,现总结如下,待以后查看之用(重点是查看计数器计到哪个值clk_out进行状态翻转) 1.偶数分频占空比为50% 其实质还是一个 ...

- 基于Verilog的奇数偶数小数分频器设计

今天呢,由泡泡鱼工作室发布的微信公共号“硬件为王”(微信号:king_hardware)正式上线啦,关注有惊喜哦.在这个普天同庆的美好日子里,小编脑洞大开,决定写一首诗赞美一下我们背后伟大的团队,虽然 ...

- Verilog设计分频器(面试必看)

分频器是指使输出信号频率为输入信号频率整数分之一的电子电路.在许多电子设备中如电子钟.频率合成器等,需要各种不同频率的信号协同工作,常用的方法是以稳定度高的晶体振荡器为主振源,通过变换得到所需要的各种 ...

- 基于verilog的分频器设计(奇偶分频原理及其电路实现:上)

在一个数字系统中往往需要多种频率的时钟脉冲作为驱动源,这样就需要对FPGA的系统时钟(频率太高)进行分频.分频器主要分为奇数分频,偶数分频,半整数分频和小数分频,在对时钟要求不是很严格的FPGA系统中 ...

- 基于Verilog的偶数、奇数、半整数分频以及任意分频器设计

在FPGA的学习过程中,最简单最基本的实验应该就是分频器了.由于FPGA的晶振频率都是固定值,只能产生固定频率的时序信号,但是实际工程中我们需要各种各样不同频率的信号,这时候就需要对晶振产生的频率进行 ...

- FGPA 中的计数器Verilog语言(时钟分频器)

在quartusII8.0中为ALTERAFPGA设置一个分频器(计数器) 输入时钟48Mhz 输出时钟9600HZ /* 实验名称: 计数器 ** 程序功能: 将48Mhz的时钟分频为9600Hz ...

- Verilog分频器

verilog设计进阶 时间:2014年5月6日星期二 主要收获: 1.自己动手写了第一个verilog程序. 题目: 利用10M的时钟,设计一个单周期形状例如以下的周期波形. 思考: 最開始的想法是 ...

- 基于verilog的分频器设计(半整数分频,小数分频:下)

第二种方法:对进行奇数倍n分频时钟,首先进行n/2分频(带小数,即等于(n-1)/2+0.5),然后再进行二分频得到.得到占空比为50%的奇数倍分频.下面讲讲进行小数分频的设计方法. 小数分频:首先讲 ...

- Verilog HDL学习_1:分频器/PWM的实现

(一)参考学习资料 (二)实际操作 1. 相关变量计算: First Initial Second Initial Upper case H X ASCII (Dec) 72 88 Lengths ...

随机推荐

- iphone上mitmproxy证书设置

PC端安装mitmproxy并添加证书后,基本问题不大,都能正常运行起来 手机端iphone上下载安装mitmproxy证书: 1.手机和PC在同一个局域网中,设置wifi代理为PC端的ip,端口为m ...

- prometheus告警插件-alertmanager

prometheus本身不支持告警功能,主要通过插件alertmanage来实现告警.AlertManager用于接收Prometheus发送的告警并对于告警进行一系列的处理后发送给指定的用户. pr ...

- python-json函数

json函数使用 JSON 函数需要导入 json 库:import jsonjson函数包含:json.dumps,json.loads,json.load,json.dump #1.json.du ...

- Ubuntu18.04: GPU Driver 390.116 + CUDA9.0 + cuDNN7 + tensorflow 和pytorch环境搭建

1.close nouveau 终端输入:sudo gedit /etc/modprobe.d/blacklist.conf 末尾加两行 blacklist nouveau options nouve ...

- macaca 初试

看到macaca的介绍,在移动端和PC端的自动化UI测试都同时支持, 联想到最近的行业都是同时对移动端和PC端(较少,几乎不维护)追求UI自动化测试,打算拿来试一下. 首先上macaca的地址:htt ...

- dp背包问题

0-1背包 1.问题定义: 给定n种物品和背包.物品i的重量是wi,价值是vi,每种物品只有一个,背包容量为C.问:应该如何选择装入背包的物品,使得装入背包中的物品总值最大. 2.算法思路: 选择装入 ...

- Linux下通过vi修改只读文件

打开一个只读文件 $ vi /etc/crontab 此时会进入crontab的编辑界面,通过按键 ESC 可以进入命令模式,按键 I 进入插入模式 但是!如果此时没有权限进行修改的话,虽然可以插入编 ...

- 12、类成员访问修饰符public/private/producted/readonly

1.private 类的私有成员 private 类的私有成员,只能在内部访问,在外部访问不到,无法被继承,我们可以将不需要被外部修改的定义为私有的 私有成员,只能在内部访问,在外部访问不到 priv ...

- 了解计算机与操作系统发展阶段以及android操作系统的发展史

计算机与操作系统发展阶段 计算机的发展: 第一代(1946-1957年),电子管计算机 第二代(1958-1964年),晶体管计算机 第三代 (1964—1970年),集成电路数字机 第四代 (19 ...

- 在浏览器端获取文件的MD5值

前几天接到一个奇怪的需求,要在web页面中计算文件的md5值,还好这个项目是只需兼容现代浏览器的,不然要坑死了. 其实对文件进行md5,对于后端来说是及其简单的.比如使用Node.js,只要下面几行代 ...