分频器的Verilog实现

一、占空比50%的奇数分频

1、实现思路

实现奇数(N)分频,分别用上升沿计数到(N-1)/2,再计数到N-1;用下降沿计数到(N-1)/2,再计数到N-1,得到两个波形,然后把它们相或即可得到N分频。

2、代码

module fp_odd(clk_in,rst_n,cnt_p,cnt_n,clk_p,clk_n,clk_out);

parameter N=;

input clk_in;

input rst_n;

output[:] cnt_p;

output[:] cnt_n;

output clk_p;

output clk_n;

output clk_out; reg[:] cnt_p;

reg[:] cnt_n;

reg clk_p;

reg clk_n; always @(posedge clk_in or negedge rst_n)

begin

if(!rst_n) cnt_p <= ;

else

begin

if(cnt_p == N-) cnt_p <= ;

else cnt_p <= cnt_p + 'b1;

end

end always @(posedge clk_in or negedge rst_n)

begin

if(!rst_n) clk_p <= ;

else

begin

if(cnt_p == (N-)/) clk_p <= !clk_p;

else if(cnt_p == N-) clk_p <= !clk_p;

else clk_p <= clk_p;

end

end always @(negedge clk_in or negedge rst_n)

begin

if(!rst_n) cnt_n <= ;

else

begin

if(cnt_n == N-) cnt_n <= ;

else cnt_n <= cnt_n + 'b1;

end

end always @(negedge clk_in or negedge rst_n)

begin

if(!rst_n) clk_n <= ;

else

begin

if(cnt_n == (N-)/) clk_n <= !clk_n;

else if(cnt_n == N-) clk_n <= !clk_n;

else clk_n <= clk_n;

end

end assign clk_out = clk_p | clk_n; endmodule

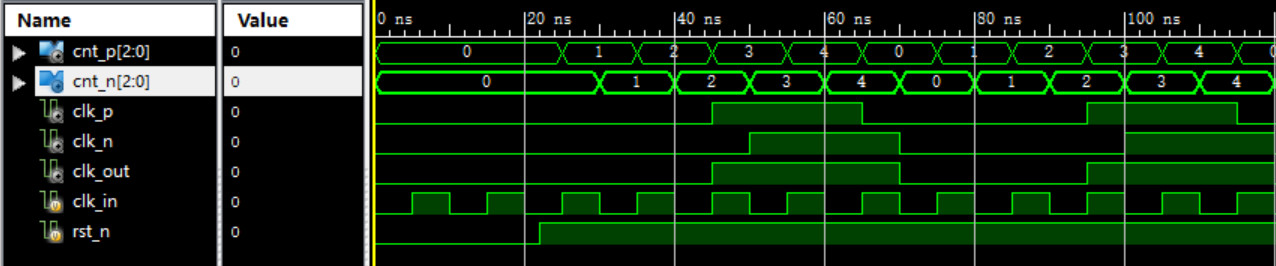

3、仿真波形

分频器的Verilog实现的更多相关文章

- 分频器的verilog设计

笔者最近由于实验室老师的任务安排重新又看了一下分频器的verilog实现,现总结如下,待以后查看之用(重点是查看计数器计到哪个值clk_out进行状态翻转) 1.偶数分频占空比为50% 其实质还是一个 ...

- 基于Verilog的奇数偶数小数分频器设计

今天呢,由泡泡鱼工作室发布的微信公共号“硬件为王”(微信号:king_hardware)正式上线啦,关注有惊喜哦.在这个普天同庆的美好日子里,小编脑洞大开,决定写一首诗赞美一下我们背后伟大的团队,虽然 ...

- Verilog设计分频器(面试必看)

分频器是指使输出信号频率为输入信号频率整数分之一的电子电路.在许多电子设备中如电子钟.频率合成器等,需要各种不同频率的信号协同工作,常用的方法是以稳定度高的晶体振荡器为主振源,通过变换得到所需要的各种 ...

- 基于verilog的分频器设计(奇偶分频原理及其电路实现:上)

在一个数字系统中往往需要多种频率的时钟脉冲作为驱动源,这样就需要对FPGA的系统时钟(频率太高)进行分频.分频器主要分为奇数分频,偶数分频,半整数分频和小数分频,在对时钟要求不是很严格的FPGA系统中 ...

- 基于Verilog的偶数、奇数、半整数分频以及任意分频器设计

在FPGA的学习过程中,最简单最基本的实验应该就是分频器了.由于FPGA的晶振频率都是固定值,只能产生固定频率的时序信号,但是实际工程中我们需要各种各样不同频率的信号,这时候就需要对晶振产生的频率进行 ...

- FGPA 中的计数器Verilog语言(时钟分频器)

在quartusII8.0中为ALTERAFPGA设置一个分频器(计数器) 输入时钟48Mhz 输出时钟9600HZ /* 实验名称: 计数器 ** 程序功能: 将48Mhz的时钟分频为9600Hz ...

- Verilog分频器

verilog设计进阶 时间:2014年5月6日星期二 主要收获: 1.自己动手写了第一个verilog程序. 题目: 利用10M的时钟,设计一个单周期形状例如以下的周期波形. 思考: 最開始的想法是 ...

- 基于verilog的分频器设计(半整数分频,小数分频:下)

第二种方法:对进行奇数倍n分频时钟,首先进行n/2分频(带小数,即等于(n-1)/2+0.5),然后再进行二分频得到.得到占空比为50%的奇数倍分频.下面讲讲进行小数分频的设计方法. 小数分频:首先讲 ...

- Verilog HDL学习_1:分频器/PWM的实现

(一)参考学习资料 (二)实际操作 1. 相关变量计算: First Initial Second Initial Upper case H X ASCII (Dec) 72 88 Lengths ...

随机推荐

- node中 path.resolve 和path.join的区别

path.resolve('a','b','c') 返回a/b/c path.resolve理论上总是以前一个路径作为基础路径,然后匹配当前路径,当前路径会有三种情况根目录(/),当前目录(./),上 ...

- 『高性能模型』Roofline Model与深度学习模型的性能分析

转载自知乎:Roofline Model与深度学习模型的性能分析 在真实世界中,任何模型(例如 VGG / MobileNet 等)都必须依赖于具体的计算平台(例如CPU / GPU / ASIC 等 ...

- leetcode-979-树

https://leetcode.com/problems/distribute-coins-in-binary-tree/ n个硬币随机分布在n个点上,要求每个点都拥有一个硬币,问最小的花费. 对每 ...

- 一个空格引起的错误。 python

'render_field' tag requires a form field followed by a list of attributes and values in the form att ...

- java Arrays.asList方法注意事项

1. 简介 Arrays.asList()方法可以将数组转化为长度固定的列表. 该方法强调了列表的长度是固定的,因此不能使用list的add和remove方法修改list长度. 2. 示例 impor ...

- win10安装配置nodejs

下载node 官网下载node 接下来在命令提示符里(win+R)输入node -v和npm -v,如图所示,表示安装完成. 测试, 配置node 在nodejs文件目录下,新建文件夹node ...

- 2017年11月23日**科技面试java工程师面试总结

从整个面试看了,表现并不理想,有很多不足. 1.关于手机页面闪现问题的处理.从原理上观察,页面闪现是因为异步请求导致的.在进入页面中首先会加载默认的东西,此时也会访问数据库端,会用ajax判断是否满足 ...

- Spring学习之实例化bean的三种方式

实例化bean的三种方式 构造器实例化bean Person.java public class Person { private String name; private Integer age; ...

- vi编辑器和系统分区

作业一:1) 将用户信息数据库文件和组信息数据库文件纵向合并为一个文件/1.txt(覆盖) cat /etc/passwd /etc/group > /1.txt2) 将用户信息数据库文件和用户 ...

- 【转载】27.SpringBoot和SpringMVC的区别

版权声明:本博客为记录本人JAVA自学之路而开,内容大多从网上学习与整理所得,若侵权请告知! https://blog.csdn.net/u014590757/article/details/7960 ...