FPGA基础学习(7) -- 内部结构之CLB

一直以来,觉得自己关于FPGA方面,摸不到“低”——对底层架构认识不清,够不着“高”——没真正独立做过NB的应用,如高速、复杂协议或算法、神经网络加速等高大上的应用,所以能力和认识水平都处于中间水平。这段时间做时序优化,感觉心有余而力不足了,可能要触及手动布局布线了,打开Device布局图才开始有兴趣探究一些底层结构的东西。

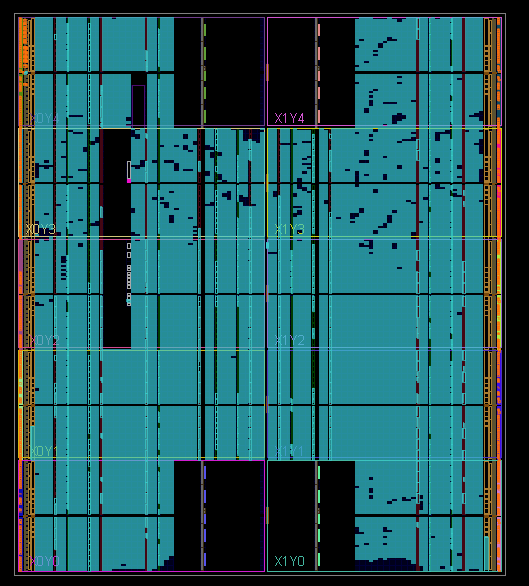

看吧,资源已经用了80%的A7 200芯片

可能翻开任何一本有关FPGA的书籍,上来就会介绍FPGA的历史,原理,内部结构什么的,大部分人看着都极其枯燥,常常要么直接略过,要么就看一遍,久了也就忘记了(部分靠翻译文档的书作者该好好反思)。我硬着头皮去弥补之前缺失的一些基础知识,结合Xilinx A7 芯片,总结一下自己的收获。

1. 总览

平台:Vivado

芯片:XC7A200

FPGA主要有六部分组成:可编程输入输出单元、可编程逻辑单元、完整的时钟管理、嵌入块状RAM、布线资源、内嵌的底层功能单元和内嵌专用硬件模块。其中最为主要的是可编程输出输出单元、可编程逻辑单元和布线资源。

放大,这些就是内部资源,主要是逻辑单元和块状RAM及一些内嵌功能单元

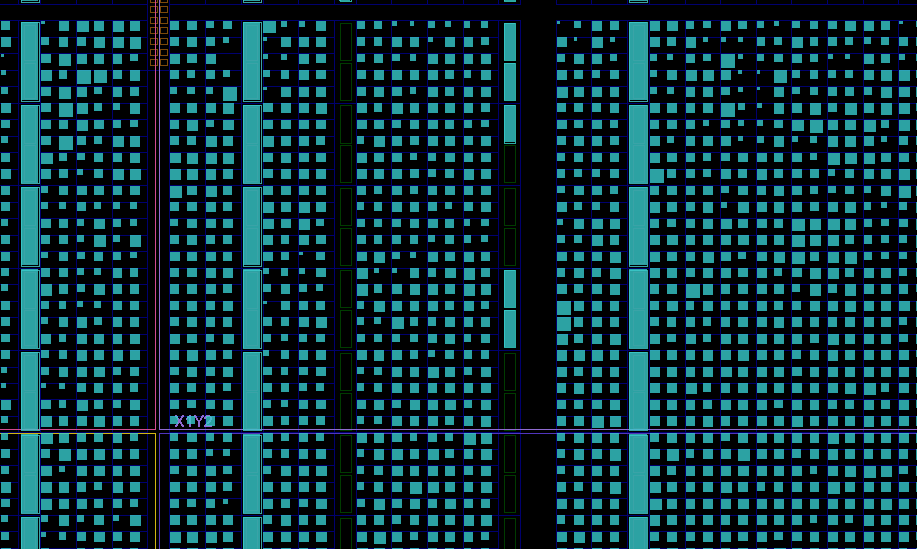

再放大,这些逻辑单元的内部结构也出来了,像大型“停车场”

2. 可配置逻辑单元

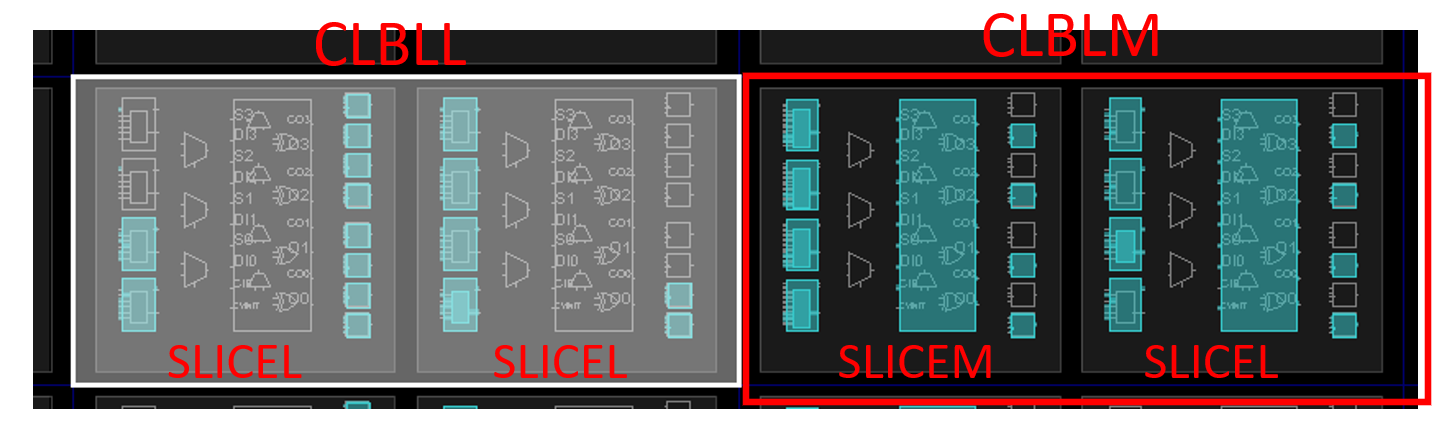

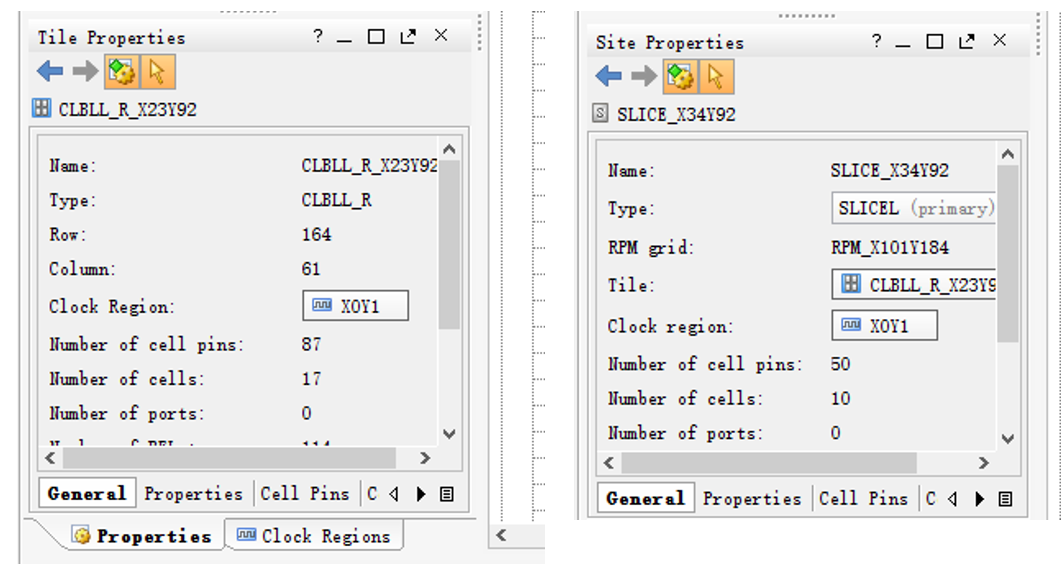

可配置逻辑单元(Configurable Logic Block,CLB)在FPGA中最为丰富,由两个SLICE组成。由于SLICE有SLICEL(L:Logic)和SLICEM(M:Memory)之分,因此CLB可分为CLBLL和CLBLM两类。

点击内部的逻辑单元,通过阴影区别包含的范围,你可以清晰的看到结构划分的层级。在旁边窗口可以清晰的看到选中部分的属性(Properties)。

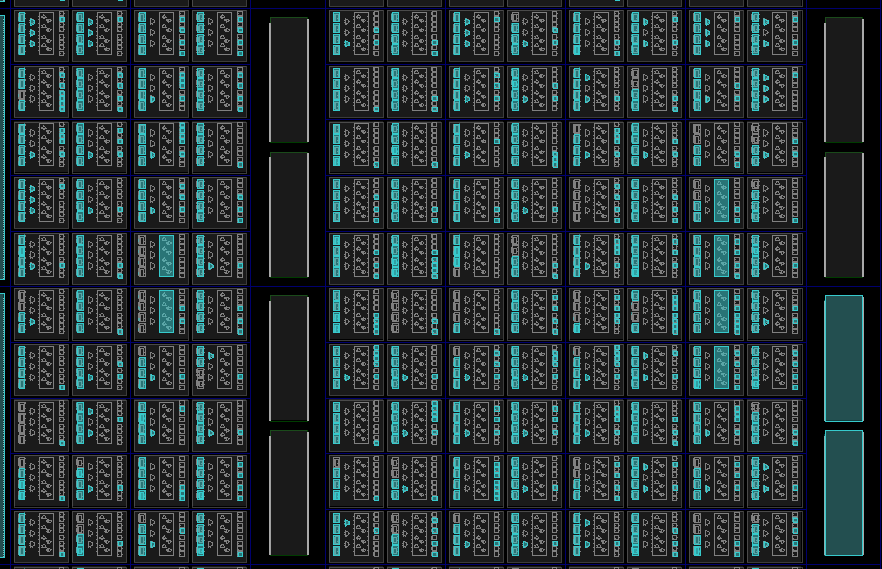

来,再放大,放大到一个SLICEL,如下图所示。

SLICEL和SLICEM内部都包含4个6输入查找表(Look-Up-Table,LUT6)、3个数据选择器(MUX)、1个进位链(Carry Chain)和8个触发器(Flip-Flop),下面分部分介绍的时候,时不时可以再回头看这张结构图。

2.1 6输入查找表(LUT6)

虽然SLICEL和SLICEM的结构组成一样,但两者更细化的结构上略有不同,区别在于LUT6上(如下图所示),从而导致LUT6的功能有所不同(如下表格所示)。

| LUT功能 | SLICEL | SLICEM |

|---|---|---|

| 逻辑函数发生器 | v | v |

| ROM | v | v |

| 分布式RAM | v | |

| 移位寄存器 | v |

上边的功能可以看到,不论是SLICEL还是SLICEM,他们的LUT6都可以作为ROM使用,配置为64x1(占用1个LUT6,64代表深度,1代表宽度)、128x1(占用2个LUT6)和256(占用4个LUT6)的ROM。

另外既然SLICEM中的M代表memory的意思,所以增加了更多存储功能。可以配置为RAM,尤其指分布式RAM。其中RAM的写操作为同步,而读操作是异步的,即与时钟信号无关。如果要实现同步读操作,则要额外占用一个触发器,从而增加了意识时钟的延迟(Latency),但提升了系统的性能。这就解释了为什么我们实现RAM同步读写的时候,读出输出要延迟一个clk。一个LUT6可配置64x1的RAM,当RAM的深度大于64时,会占用额外的MUX(F7AMUX,F7BMUX,F8MUX,即一个SLICE中的那3个MUX)。

SLICEM中的LUT还可以配置为移位寄存器,每个LUT6可实现深度为32的移位寄存器,且同一个SLICEM中的LUT6(4个)可级联实现128深度的移位寄存器。

2.2 选择器(MUX)

SLICE中的三个MUX(Multiplexer:F7AMUX,F7BMUX和F8MUX)可以和LUT6联合共同实现更大的MUX。事实上,一个LUT6可实现4选1的MUX。

SLICE中的F7MUX(F7AMUX和F7BMUX)的输入数据来自于相邻的两个LUT6的O6端口。

一个F7MUX和相邻的两个LUT6可实现一个8选1的MUX。因此,一个SLICE可实现2个8选1的MUX。

4个LUT6、F7AMUX、F7BMUX和F8MUX可实现一个16选1的MUX。因此,一个SLICE可实现一个16选1的MUX。

2.3 进位链(Carry Chain)

进位链用于实现加法和减法运行。就是结构图中,中间那个大的部分,可以看到它内部实际还包含4个MUX和4个2输入异或门(XOR)。

异或运算是加法运算中必不可少的运算。

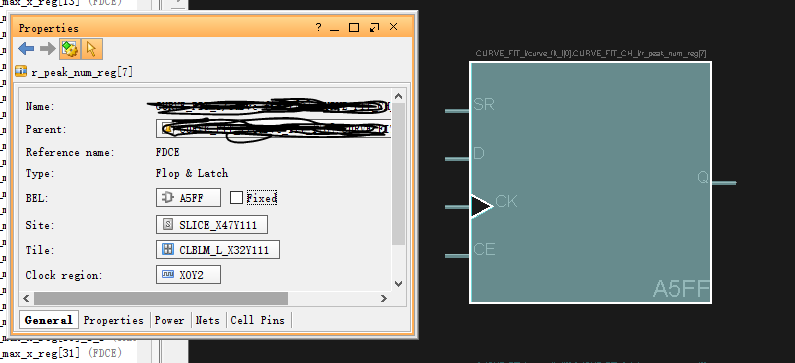

2.4 触发器(Flip-Flop)

每个SLICE中有8个触发器。这个8个触发器可分为两大类:4个只能配置为边沿敏感的D触发器(Flip-Flop)和4个即可配置为边沿敏感的D触发器又可配置为电平敏感的锁存器(Flop&Latch)。当后者被用作锁存器的时候,前者将无法使用。

当这8个触发器都用作D触发器时,他们的控制端口包括使能端CE、置位/复位端口S/R和时钟端口CLK是对应共享的,也就是就是说共用的。{CE,S/R,CLK}称为触发器的控制集。显然,在具体的设计中,控制集种类越少越好,这样可以提高触发器的利用率。那么怎样减少控制集种类呢?我的理解是:

- 减少时钟种类,即频率越少越好;

- 统一规范的设计逻辑,如复位。

S/R端口可配置为同步/异步置位或同步/异步复位,且高有效,因此可形成4种D触发器,如下表所示。

| 原语(Primitive) | 功能描述 | 原语(Primitive) | 功能描述 |

|---|---|---|---|

| FDCE | 同步使能,异步复位 | FDRE | 同步使能,同步复位 |

| FDPE | 同步使能,异步置位 | FDSE | 同步使能,同步置位 |

在我们的常规设计中,FDCE和FDPE占了绝大多数。

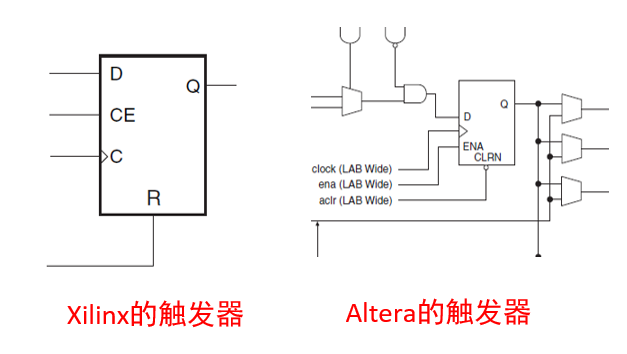

说到高有效,让我想起了一个大家习以为常,但很少深究的问题:为什么一开始接触FPGA的时候,都告诉我们低电平复位?后来查了一些资料,有说从功耗、噪声可靠性方面考虑等等,但是偶然看到Xilinx和Altera两家芯片的触发器不一样!如下图所示,Xilinx的触发器是高电平复位,而Altera的触发器时低电平复位。所以这也是需要考虑的一点吗?

参考文献:

- 《7 Series FPGAs Configurable Logic Block》(UG474)

- 《VIVADO从此开始》——高亚军著(强烈推荐此书!!!!本博客论述部分大多来自高老师的书)

FPGA基础学习(7) -- 内部结构之CLB的更多相关文章

- FPGA基础学习(8) --内部结构之存储单元

目录 1. 基本结构 2. BRAM与DRAM的比较 3. BRAM的特点 4. Block Memory的使用 4.1 配置为RAM或ROM 4.2. 配置为FIFO 参考文献: 上一篇中提到了SL ...

- FPGA基础学习(3) -- 跨时钟域处理方法

文章主要是基于学习后的总结. 1. 时钟域 假如设计中所有的触发器都使用一个全局网络,比如FPGA的主时钟输入,那么我们说这个设计只有一个时钟域.假如设计有两个输入时钟,如图1所示,一个时钟给接口1使 ...

- FPGA基础学习(9) -- 复位设计

目录 1. 常见问题 2. 常见的复位方式 3. 合理的复位设计 3.1 复位电平 3.2 异步复位同步化 3.3 恰到好处的复位 4. 补充 4.1 所谓的上电初始化 参考文献 一开始接触到FPGA ...

- FPGA基础学习(6) -- 原语

目录 1. IBUF和IBUFDS(IO) 2. IDDR(Input/Output Functions) 3. IBUFG和IBUFGDS(IO) 原语,即primitive.不同的厂商,原语不同: ...

- FPGA基础学习(5) -- 时序约束(实践篇)

目录 1. 理论回顾 2. 时间裕量 3. 最大延迟和最小延迟 4. 案例分析 参考文献: 距离上一篇有关时序的理论篇已经有一段时间了(可以参考博文FPGA时序约束--理论篇),实际上此段时间,甚至到 ...

- FPGA基础学习(4) -- 时序约束(理论篇)

在FPGA 设计中,很少进行细致全面的时序约束和分析,Fmax是最常见也往往是一个设计唯一的约束.这一方面是由FPGA的特殊结构决定的,另一方面也是由于缺乏好用的工具造成的.好的时序约束可以指导布局布 ...

- FPGA基础学习(1) -- FFT IP核(Quartus)

为了突出重点,仅对I/O数据流为steaming的情况作简要说明,以便快速上手,有关FFT ip核模型及每种设置详细介绍请参考官方手册FFT MegaCore Function User Guide. ...

- FPGA基础学习(2) -- FIFO IP核(Quartus)

ALTERA在LPM(library of parameterized mudules)库中提供了参数可配置的单时钟FIFO(SCFIFO)和双时钟FIFO(DCFIFO).FIFO主要应用在需要数据 ...

- FPGA基础知识了解

FPGA学习的一些误区 FPGA入门必看资源 FPGA百度百科 FPGA基础知识及其工作原理 高端设计工具为少有甚是没有硬件设计技术的工程师和科学家提供现场可编程门阵列(FPGA).无论你使用图形化设 ...

随机推荐

- IPP库下FFT的基本实现

首先感谢韩昊同学,他的傅里叶分析入门给我们对数学公式不熟悉的人了解傅里叶算法打开了一扇窗户,其原文发表于知乎:https://zhuanlan.zhihu.com/p/19763358 在了解其基本原 ...

- python用sqlite3模块操作sqlite数据库-乾颐堂

SQLite是一个包含在C库中的轻量级数据库.它并不需要独立的维护进程,并且允许使用非标准变体(nonstandard variant)的SQL查询语句来访问数据库. 一些应用可是使用SQLite保存 ...

- [Cookie] Clear Cookie

import com.eviware.soapui.impl.wsdl.support.http.HttpClientSupport def myCookies = testRunner.testCa ...

- LWIP内存管理

LWIP是一种TCP/IP协议栈,与嵌入式操作系统一样也提供了内存管理. 内存池里面有多个同样大小的内存,不同类型的内存池其里面的内存大小不一样.

- Spring Boot☞ 多数据源配置(二):Spring-data-jpa

效果图: 代码区: package com.wls.integrateplugs.datasource; import org.springframework.beans.factory.annota ...

- data-参数说明(模态弹出窗的使用)

除了通过data-toggle和data-target来控制模态弹出窗之外,Bootstrap框架针对模态弹出框还提供了其他自定义data-属性,来控制模态弹出窗.比如说:是否有灰色背景modal-b ...

- 改善C#公共程序类库质量的10种方法(转)

出处:http://www.cnblogs.com/JamesLi2015/p/3140897.html 最近重构一套代码,运用以下几种方法,供参考. 1 公共方法尽可能的使用缓存 public s ...

- [GO]结构体的比较和赋值

package main import "fmt" func main() { type student struct { id int name string sex byte ...

- ssh的配置[待写]

开机自启:/etc/rc.local /etc/init.d/ssh start 将 /etc/ssh/sshd_confg中PermitRootLogin no 改为yes,重新启动ssh服务.

- 编写高质量代码改善C#程序的157个建议——建议103:区分组合和继承的应用场合

建议103:区分组合和继承的应用场合 继承所带来的多态性虽然是面向对象的一个重要特性,但这种特性不能在所有的场合中滥用.继承应该被当做设计架构的有用补充,而不是全部. 组合不能用于多态,但组合使用的频 ...