verilog语法实例学习(9)

常用的时序电路介绍

寄存器

一个触发器可以存储一位数据,由n个触发器组成的电路可以存储n位数据,我们把这一组触发器叫做寄存器。寄存器中每个触发器共用同一个时钟。

下面是n位寄存器的代码,我们通过一个参数定义n,在实例化时传入参数n。

module regne (D, clk,Rst_n,E,Q);

parameter n=4;

input [n-1:0] D;

input clk;

input Rst_n; //复位信号

input E; //使能信号 output reg [n-1:0] Q; always @(posedge clk,negedge Rst_n)

if(Rst_n==0)

Q <= 0;

else if(E)

Q <= D; endmodule

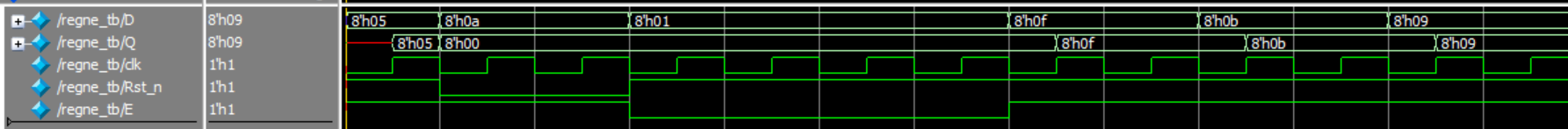

`timescale 1ns/1ns

`define clock_period 20 module regne_tb;

reg [7:0] D;

wire [7:0] Q;

reg clk;

reg Rst_n;

reg E; regne #(.n(8)) regne(.D(D),.clk(clk),.Rst_n(Rst_n),.E(E),.Q(Q));

always # (`clock_period/2) clk = ~clk; initial

begin

D = 4'b01010101;

clk = 1'b0;

Rst_n = 1'b1;

E = 1'b1;

#(`clock_period)

Rst_n = 1'b0;

D = 4'b10101010;

#(`clock_period*2)

E = 1'b0;

Rst_n = 1'b1;

D = 4'b00010001;

#(`clock_period*4)

E = 1'b1;

D = 4'b1111;

#(`clock_period*2)

D = 4'b10111011;

#(`clock_period*2)

D = 4'b10011001;

#(`clock_period*2)

$stop;

end endmodule

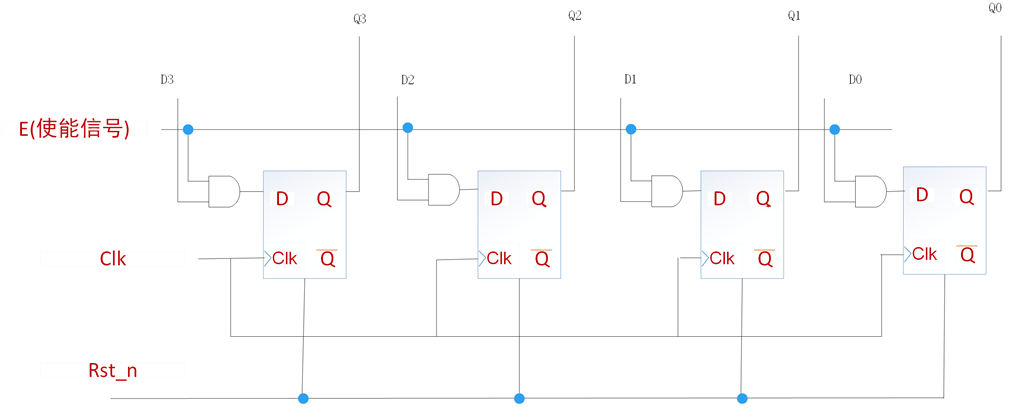

下面的电路能实现带使能和异步复位的n位寄存器(这儿假设是4位)。D3D2D1D0是寄存器输入值。Q3Q2Q1Q0是寄存器输出值。

移位寄存器

寄存器移位可以实现整数乘法和触发,左移一位且在末位补0,相当于乘以2,右移一位可以实现除2功能。有移位功能的寄存器称作移位寄存器。

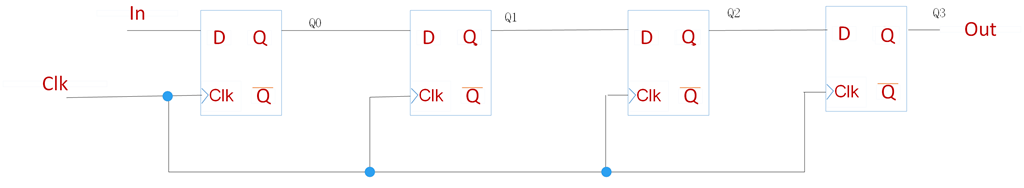

下面的电路可以实现把自身内容右移一位的4位移位寄存器:数据以串行的方式从输入端In移入移位寄存器,在时钟的上升沿每个触发器的内容传输到下一个触发器。假设初始状态为0,在连续的8个周期内输入信号In的值分别为: 1,0,1,1,1,0,0,0,则各个寄存器状态的变化如下表:

| In | Q0 | Q1 | Q2 | Q3(out) | |

| t0 | 1 | 0 | 0 | 0 | 0 |

| t1 | 0 | 1 | 0 | 0 | 0 |

| t2 | 1 | 0 | 1 | 0 | 0 |

| t3 | 1 | 1 | 0 | 1 | 0 |

| t4 | 1 | 1 | 1 | 0 | 1 |

| t5 | 0 | 1 | 1 | 1 | 0 |

| t6 | 0 | 0 | 1 | 1 | 1 |

| t7 | 0 | 0 | 0 | 1 | 1 |

下面的代码实现把串行的输入存储到一个寄存器,可以选择时机并行输出。电路还带有一个Load信号,如果Load=1,则移位寄存器装入初始值,否则执行移位操作。这种串行加载并行读取数据电路叫串-并转化器。

/*串行输入,并行输出寄存器

从高位输入,即从右向左输入*/

module shiftn(R,L,w,clk,Q);

parameter n=8;

input [n-1:0] R;//初始值

input L; //load信号

input w; //移入信号

input clk;//时钟信号

output reg [n-1:0] Q;

integer k; always @(posedge clk)

begin

if(L)

Q <=R;

else

begin

for(k=0; k<n-1; k=k+1)

Q[k] <= Q[k+1];

Q[n-1] <= w;

end end endmodule

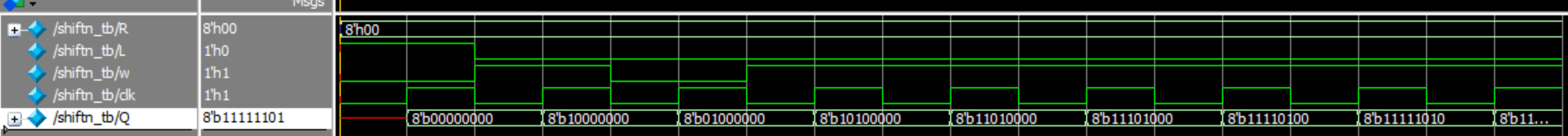

`timescale 1ns/1ns

`define clock_period 20 module shiftn_tb; reg [7:0] R;

reg L;

reg w;

reg clk;

wire [7:0] Q; shiftn #(.n(8)) shitn0(.R(R),.L(L),.w(w),.clk(clk),.Q(Q));

initial clk = 0;

always #(`clock_period/2) clk = ~clk; initial

begin

R = 8'b00000000;

L = 1'b1;

w = 1'b0;

#(`clock_period)

L = 1'b0;

w = 1'b1;

#(`clock_period)

w = 1'b0;

#(`clock_period)

w = 1'b1;

#(`clock_period)

w = 1'b1;

#(`clock_period)

w = 1'b1;

#(`clock_period)

w = 1'b1;

#(`clock_period)

w = 1'b1;

#(`clock_period)

w = 1'b1;

#(`clock_period)

$stop;

end endmodule

我们也可以使用拼接符操作代替for循环,实现同样的功能,而且语法更加简单。

/*串行输入,并行输出寄存器

从高位输入,即从右向左输入*/

module shiftn(R,L,w,clk,Q);

parameter n=8;

input [n-1:0] R;//初始值

input L; //load信号

input w; //移入信号

input clk;//时钟信号

output reg [n-1:0] Q; always @(posedge clk)

begin

if(L)

Q <=R;

else

begin Q = {w,Q[n-1:1]};

end end endmodule

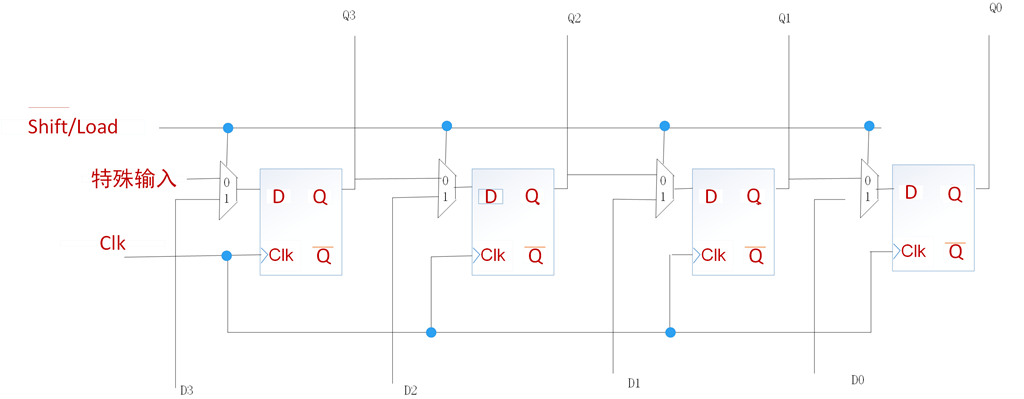

下面的电路可以实现串行输入,并行输出;并行输入,串行输出;

verilog语法实例学习(9)的更多相关文章

- verilog语法实例学习(4)

Verilog模块 Verilog中代码描述的电路叫模块,模块具有以下的结构: module module_name[ (portname {, portname})]; //端口列表 [parame ...

- verilog语法实例学习(1)

本文档中通过verilog实例来学习verilog语法.Verilog是一种硬件描述语言,它具有并发性和时序性.并发性是指不同硬件模块的同时操作,时序性是指信号的赋值或操作在时钟的边沿进行.由于作者本 ...

- verilog语法实例学习(12)

verilog中的综合和不可综合总结 Verilog中综合的概念 综合就是EDA工具或者说综合工具把我们编写的verilog代码转化成具体电路的过程.Verilog中有很多语法,结构,过程,语句,有些 ...

- verilog语法实例学习(6)

函数和任务 函数 https://wenku.baidu.com/view/d31d1ba8dd3383c4bb4cd283.html verilog中函数的目的是允许代码写成模块的方式而不是定义独立 ...

- verilog语法实例学习(5)

子电路模块 子电路模块的使用 一个verilog模块能够作为一个子电路包含在另一个模块中.采用这种方式,所有的模块都必须定义在一个文件中,那么verilog编译器就必须被告知每个模块的所属.模块例化的 ...

- verilog语法实例学习(2)

Verilog中的信号类型 线网类型 线网类型表示一个或多个门或者其它类型的信号源驱动的硬件连线.如果没有驱动源,则线网的默认值为z.verilog中定义的线网类型有以下几种: wire,tr ...

- verilog语法实例学习(13)

verilog代码编写指南 变量及信号命名规范 1. 系统级信号的命名. 系统级信号指复位信号,置位信号,时钟信号等需要输送到各个模块的全局信号:系统信号以字符串Sys开头. 2. 低电平有效的 ...

- verilog语法实例学习(11)

同步时序电路的一般形式 时序电路由组合逻辑以及一个或多个触发器实现.一般的架构如下图所示:W为输入,Z为输出,触发器中存储的状态为Q.在时钟信号的控制下,触发器通过加在其输入端的组合逻辑输入,使得电路 ...

- verilog语法实例学习(10)

常用的时序电路介绍 T触发器和JK触发器 在D触发器输入端添加一些简单的逻辑电路,可以生成另一种类型的存储元件.比如下图所示的T触发器.该电路有一个上升沿触发的触发器和两个与门,一个或门,以及一个反相 ...

随机推荐

- tornado登陆装饰器

tornado作为鼎鼎大名的web异步框架,用来作为高性能服务器以及web框架都是首选.自从python3.4加入了asyncio原生协程后,tornado的最新版本也开始使用了原生的协程.定义协程函 ...

- Android-Window(一)——初识Window

Android-Window(一)--初识Window 学习自 <Android开发艺术探索> https://blog.csdn.net/qian520ao/article/detail ...

- OSNIT信息收集分析框架OSRFramework

OSNIT信息收集分析框架OSRFramework OSNIT是一种从公开的信息资源搜集信息的有效方式.Kali Linux集成了一款专用分析工具集OSRFramework.该工具集包含多个常用工具 ...

- 线上zk节点报org.apache.zookeeper.server.NIOServerCnxnFactory.run(NIOServerCnxnFactory.java:187) at java.lang.Thread.run(libgcj.so.10)

线上zk做配置管理,最近突然发现两个节点一直在刷下边 java.nio.channels.CancelledKeyException at gnu.java.nio.SelectionKeyIm ...

- 【BZOJ 4059】 (分治暴力|扫描线+线段树)

4059: [Cerc2012]Non-boring sequences Time Limit: 10 Sec Memory Limit: 128 MBSubmit: 632 Solved: 22 ...

- 1722 最优乘车 1997年NOI全国竞赛

题目描述 Description H城是一个旅游胜地,每年都有成千上万的人前来观光.为方便游客,巴士公司在各个旅游景点及宾馆,饭店等地都设置了巴士站并开通了一些单程巴上线路.每条单程巴士线路从某个巴士 ...

- hdu 5774 Where Amazing Happens 水题

Where Amazing Happens 题目连接: http://acm.hdu.edu.cn/showproblem.php?pid=5774 Description As the premie ...

- centos 7.2 安装mysql 修改 初始密码

# /etc/init.d/mysqld stop # mysqld_safe --user=mysql --skip-grant-tables --skip-networking &# my ...

- mySql---数据库索引原理及优化

一.写在前面 本文以MySQL数据库为研究对象,讨论与数据库索引相关的一些话题.特别需要说明的是,MySQL支持诸多存储引擎,而各种存储引擎对索引的支持也各不相同,因此MySQL数据库支持多种索引类型 ...

- 刚刚看到 PNaCl, 这才是我一直期待的跨平台的好东西!

http://code.google.com/p/nativeclient/ https://developers.google.com/native-client/overview