Altera三速以太网IP核快速仿真与使用(上篇)

对于比较高级的ip核,altera一般都会提供仿真案例,网上有关于这个IP核的各种仿真方法,但都比较繁琐,前几日,朋友跟我分享了一个比较快速高效的仿真方法,这个方法也是他摸索折腾了一段时间才总结出来的,在此,也谢谢他这种毫无保留的分享奉献精神,估计此套方法可以针对Altera的大多数复杂ip核仿真。

新建工程,生成ip核的步骤我就省略了,直接进入ip核调用仿真部分。

在生成的工程里找到“testbench”文件夹,里面有一个README.txt,打开按照里面的步骤操作即可。

根据上面的步骤,首先是打开“testbench”文件夹里的"generate_sim.qpf"工程

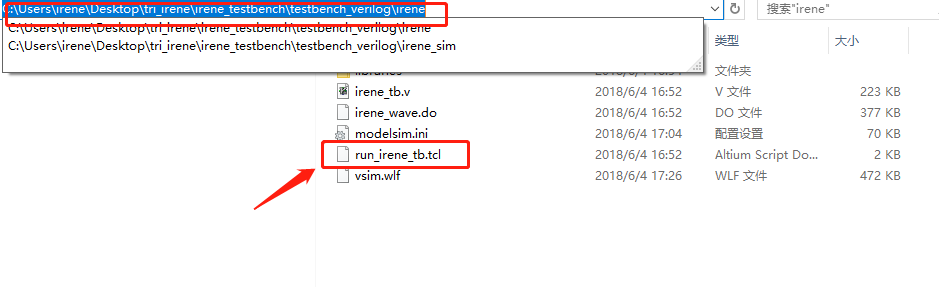

然后运行 “generate_sim_verilog.tcl”或者“generate_sim_vhdl.tcl”,到这里可以关闭quartus这个工程了,然后去打开modelsim,将路径“Change Directory”到“run_irene_tb.tcl”所在的路径

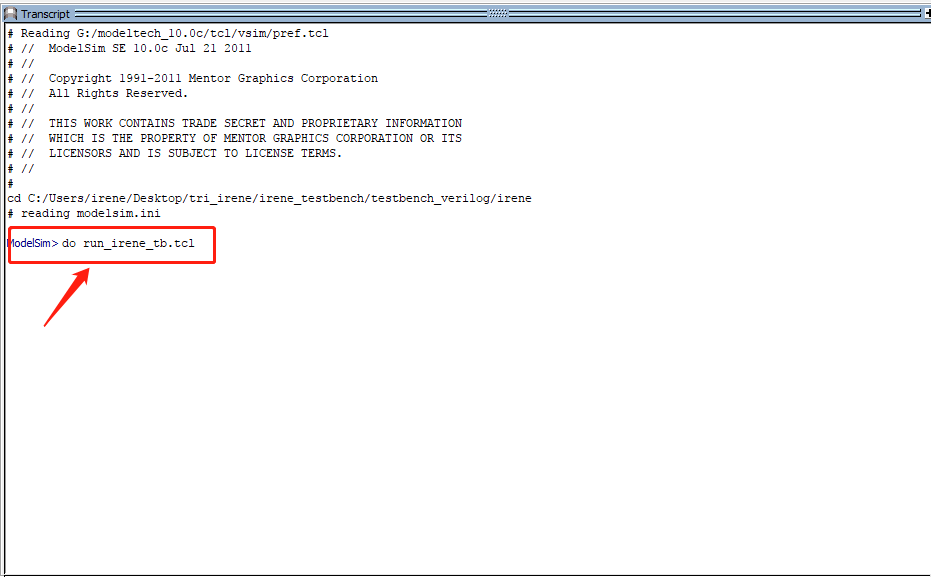

接着在modelsim运行命令框输入“do run_irene_tb.tcl”,按回车键

接下来就不用人为干预了,modelsim 会自动执行直到仿真波形自动输出

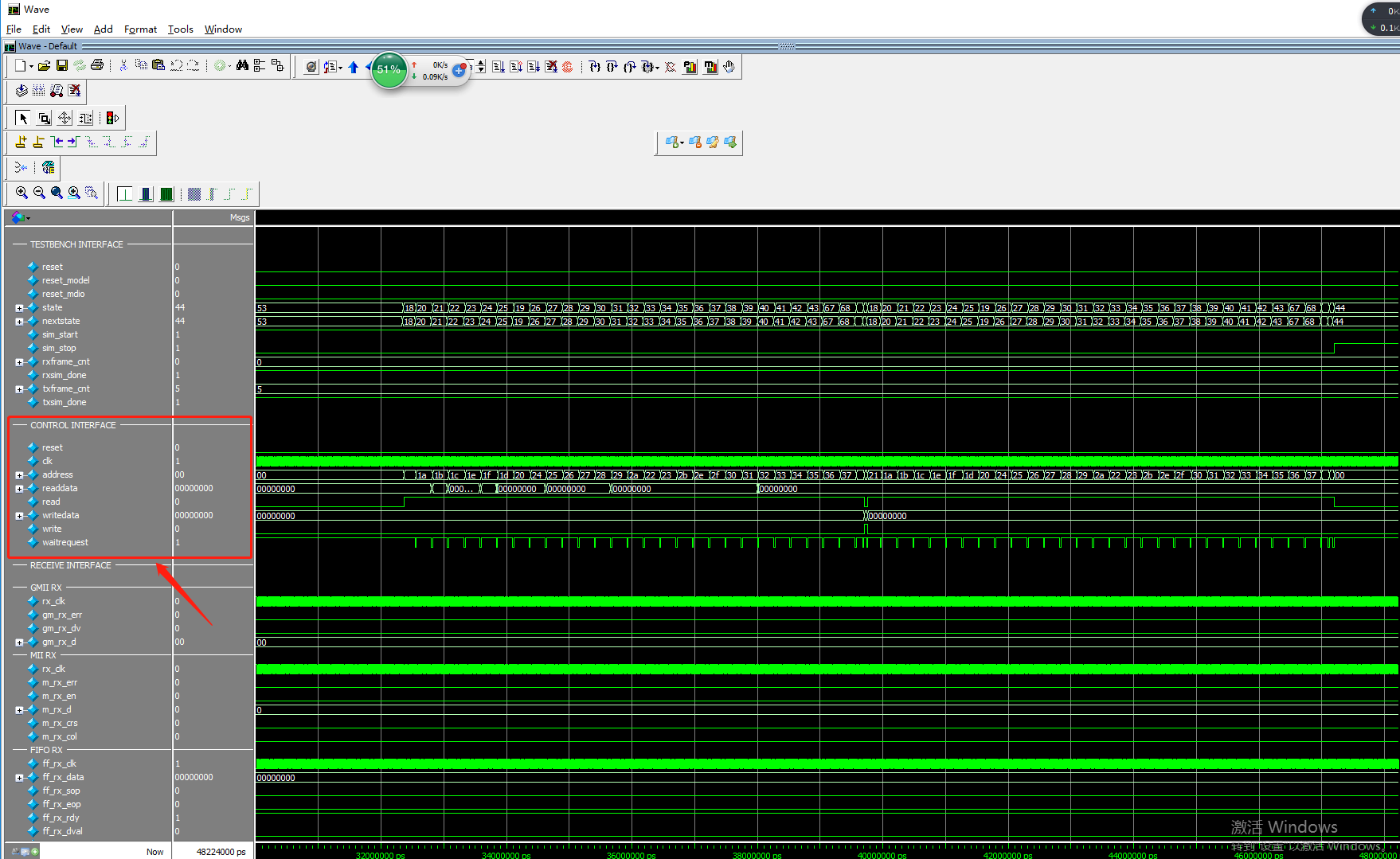

可以重点关注下它的“control interface”时序以及它的用户侧时钟,MAC IP的工作时钟。

至于control interface接口时序比较简单,通过仿真我们可以看到

在waitrequest拉低的时候可以进行读写操作。

接下来简单说一下它的工作时钟:

1)ff_tx_clk:用户侧发送端时钟,

2)ff_rx_clk:用户侧接收端时钟;

MAC IP核工作时钟是125M,接口是8 bit,但是由于IP核内部fifo的隔离,因此ff_tx_clk与ff_rx_clk无须配置为125M,只要满足125M X 8bit = 1G的速率即可。

3)rx_clk: MAC IP RX测时钟125M,是PHY芯片发给IP核的,PHY芯片跟据工作速率从网络中恢复成125M时钟,给IP核。

4)tx_clk: MAC IP TX测时钟125M, 这个时钟可以由PLL产生。

5)gtx_clk: 由pll产生的125M 时钟,送给MAC芯片。

假设时钟源clk是50M,可用一个pll产生两路时钟,一路100M给用户侧ff_tx_clk与ff_rx_clk,一路125M给 MAC IP核tx_clk,然后PHY芯片从网络中恢复成125M时钟给rx_clk。

至此,altera三速以太网IP核仿真结束,后续会陆续补充关于这个ip核的使用。

Altera三速以太网IP核快速仿真与使用(上篇)的更多相关文章

- Altera三速以太网IP核使用(下篇)--- 百兆网接口设计与使用

MAC IP核的主要作用是:实现数据链路层协议,分为TX方向与RX方向,TX方向实现的是在原包文的前面加上7个55和1个D5,RX方向则相反.在使用这个 MAC IP核之前,首先确认下自己使用的网卡是 ...

- 调用altera IP核的仿真流程—下

调用altera IP核的仿真流程—下 编译 在 WorkSpace 窗口的 counter_tst.v上点击右键,如果选择Compile selected 则编译选中的文件,Compile All是 ...

- 调用altera IP核的仿真流程—上

调用altera IP核的仿真流程—上 在学习本节内容之后,请详细阅读<基于modelsim-SE的简单仿真流程>,因为本节是基于<基于modelsim-SE的简单仿真流程>的 ...

- 用Modelsim SE 直接仿真 Altera(Intel PSG) IP核 需要注意的问题

如果我们直接用Modelsim SE仿真 Altera IP核,首先会进入Quartus II目录下找到IP核对应的仿真库源文件,然后在Modelsim SE中进行编译,添加到Modelsim SE的 ...

- altera DDR2 IP核之仿真

在生成的IP核文件夹下,有一个testbench文件夹,里面包含了一个example测试激励和DDR2仿真模型. 如下 20 -rw-r--r-- 1 Administrator 197121 171 ...

- modelsim 独立仿真vivado的IP核及仿真脚本

Modelsim独立仿真vivado的IP 最近一直在做local dimming项目的FPGA硬件实现,算法的其中一步就是直方图统计,即数字图像的某一灰度级的像素数,这个直方图的源码找了半天才搞到, ...

- 如何用ModelsimSE仿真IP核-以PLL为例

我们之前介绍了如何使用Modelsim SE进行仿真和利用do文件的仿真方法,但是其中待仿真的模块是我们自己编写的Verilog模块,但是在实际工作中,我们的设计中会经常用到FPGA厂商给我们提供的现 ...

- Lattice 的 DDR IP核使用调试笔记之DDR 的 仿真

—— 远航路上ing 整理于 博客园.转载请标明出处. 在上节建立完工程之后,要想明确DDR IP的使用细节,最好是做仿真.然后参考仿真来控制IP 核. 仿真的建立: 1.在IP核内的以下路径找到以下 ...

- 如何使用和了解ALTERA的IP核

可以通过直接对IP核进行仿真验证,通过波形来分析IP核的功能和工作方式,以及各个寄存器之间的工作关系. 也可以通过查看用户指导手册来学习IP核,如下图.

随机推荐

- Linux 系统安装[Redhat]

系统下载 Linux操作系统各版本ISO镜像下载 系统安装 1.1. 分区知识 1.2. 磁盘分区命名以及编号 IDE盘: hda 第一块盘 hda1/第一块盘的第一个分区 hdb 第二块盘 h ...

- awk 截取某段时间的日志

好久没有截取nginx/haproxy 中 的日志了,竟有点不熟悉了. 记录一下,以免以后忘记. NGINX 日志格式: 192.168.1.26 - - [14/Sep/2017:16:48:42 ...

- wind10优化

windows10启动优化 启动时: 1)关闭windows自动更新 2)关闭windows防火墙 3)关闭Windows Defender (1)使用快捷键(WIN+R)调出运行工具,然后再输入组策 ...

- JS数据模板分离(告别字符串拼接)-template

刚开始在写第一个动态网页的demo时,由于html不多,便使用字符串拼接的方法添加到dom来渲染,可是在后来写某外卖app时也需要如此添加,打开代码一看几千行,突然感觉累觉不爱 一行行的拼接有这功夫别 ...

- Python ,pickle

@Python pickle模块学习 pickle提供了一个简单的持久化功能.可以将对象以文件的形式存放在磁盘上. ---------------------------------------- ...

- 一分钟掌握Spring中bean的生命周期!

Spring 中bean 的生命周期短暂吗? 在spring中,从BeanFactory或ApplicationContext取得的实例为Singleton,也就是预设为每一个Bean 的别名只能维持 ...

- Microsoft visual c++ 14.0 is required问题

错误信息: error: Microsoft Visual C++ 14.0 is required. Get it with "Microsoft Visual C++ Build Too ...

- chromedriver linux windows各版本下载地址

taobao镜像:https://www.baidu.com/link?url=gV12RWo7v_F-BDncFNKv_Rk9jF2nMix3Z7yMd84c2QvIB0LqcwxMxTPMUyb0 ...

- Node.js 上传图片并保存

Node.js 上传图片并保存 依赖 package.json 文件 { "name": "demo", "version": " ...

- II、Python HelloWorld

大家都不是小孩子了,直接上 IDE 现在有个大问题!!没有解析器啊 这样 解析器地址比他多个 e OJBK