Verilog_Day2

Verilog_Day1 在CSDN博客上。http://blog.csdn.net/m0_38073085

第三章:

书上基本知识

- 每个Verilog程序包括4个主要部分:端口定义,I/O说明,内部信号声明和功能定义。

- input/output/inout都默认是wire型而不是reg型变量。

module block(a,b,c,d); // 端口定义

input a,b; // 输入口说明

output c,d; // 输出口说明 reg [:] e; // 内部信号说明 [2:0] 表示3位信号 assign c=a|b; // 功能定义 1.用assign申明语句

and # u1(e,c,d); // 2.用实例元件 #2表示延时2单位时间

always @(c or e)

begin end // 3.用always语句

endmodule在实例元件使用中,and #2 u1()可以看成是调用了一个名为u1的and内置模块。

- 采用“assign"语句是描述组合逻辑最常用的方法之一。而"always"块既可以用于描述组合逻辑,也可描述时序逻辑。

- 在"always"模块内,逻辑是按照指定的顺序执行的。 (?)

- 只有连续赋值语句(即用关键词assign引出的语句)和实例应用语句(即用已定义的模块名引出的语句),可以独立于过程块而存在于模块的功能定义部分。

问题1:begin - end 语句内是顺序执行还是并列执行,alwatys内部语句执行顺序是不是一定是顺序执行,而不是取决于if-else?

- 在数字电路中,x代表不定值,z代表高阻值。z还有一种表示方法是可以写作“?”。

- 高阻,数字电路里常见的术语,又叫高阻态,指的是电路的一种输出状态,既不是高电平也不是低电平。

高阻态是一个数字电路里常见的术语,指的是电路的一种输出状态,既不是高电平也不是低电平,如果高阻态再输入下一级电路的话,对下级电路无任何影响,和没接一样,如果用万用表测的话有可能是高电平也有可能是低电平,随它后面接的东西定。

高阻态的实质:

电路分析时高阻态可做开路理解。你可以把它看作输出(输入)电阻非常大。他的极限可以认为悬空。也就是说理论上高阻态不是悬空,它是对地或对电源电阻极大的状态。而实际应用上与引脚的悬空几乎是一样的。

高阻态的意义:

当门电路的输出上拉管导通而下拉管截止时,输出为高电平;反之就是低电平;如上拉管和下拉管都截止时,输出端就相当于浮空(没有电流流动),其电平随外部电平高低而定,即该门电路放弃对输出端电路的控制 。

单片机引脚复位后P口的所有引脚都是高阻输入什么是“高阻”?

高阻 简言之就是 输入输出电阻都相当大,相当于隔离状态。处在高阻态的三态门是与总线隔离开的,这样总线可以同时被其他电路占用。

高阻:从逻辑器件内部电路结构来说,就是其输出电阻很大,该状态即不是高电平,也不是低电平。当三态门处于高阻态时,无论该门的输入如何变化,都不会对其输出有贡献。

- 负数的表示方法: -8‘d5 只能放在最前面。

- 可以在长数字中使用下划线分隔开数以提高程序的可读性。

- 在verilog中用parameter来定义常量,即用parameter来定义一个标识符代表一个常量,称为符号常量。 eg: parameter byte=8,byte_msb=byte-1,delay=(byte+byte_msb)/2;

两种参数传递方法

下面是一个参数传递实例:

module Decode(s,A,F);

input s;

parameter Width=,Polarity=;

output A,F;

reg A,F;

always @(s)

if(! s) A=Width%;

else F=Polarity%;

endmodule module Top;

reg clock;

wire A4,A5,F16,F32;

initial

begin

clock=;

end

always # clock=~clock;

always @(posedge clock)

begin

end

Decode #(,) D1(clock,A4,F16);

Decode #() D2(clock,A5,F32);

endmodule

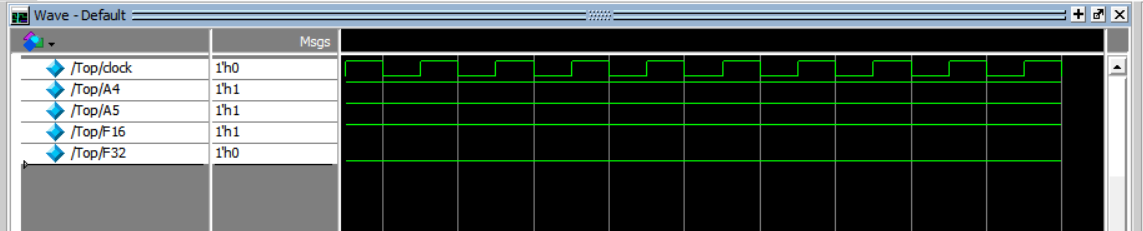

代码表示如果参数传递不成功,最后输出应该都为0,如果都传递成功,最后A4,F16,A5输出为1;F32输出为0.

最后结果输出如下图:

可以看出参数传递成功。

编程过程中的几个问题:

- 把always @(posedge clock) begin end 注释掉也没有问题;

- 本来想在Decode模块中通过reg [Width] A;将输出的A4,A5的数据长度也进行改变。但是最后没有成功。 不报错,但还是1位。

- 在Decode模块中要使用功能定义模块。不然输出全是不定态。

- 在wave窗口,使用 a 快捷键可以显示多个观察时间点。

- reg A,F; 不能省。不然会报错:Illegal reference to net "A". 因为 A 和 F 在always模块内被赋值。需要使用 reg 型数据。

另一种参数传递可以通过defparam命令来实现。

module Decode(s,A,F);

input s;

parameter Width=,Polarity=;

output A,F;

reg F;

reg [Width:] A;

always @(s)

if(! s) A=Width%;

else F=Polarity%;

endmodule module Top;

reg clock;

wire A4,A5,F16,F32;

initial

begin

clock=;

end

always # clock=~clock;

//always @(posedge clock)

//begin

//end

Decode #(,) D1(clock,A4,F16);

Decode D2(clock,A5,F32); // 这里直接产生Decode的D2。内部参数不变。

defparam // 用defparam来改变参数。

Top.D2.Width=; // 是Width, 不是A或者是A5。

endmodule

最后仿真结果不变。

总结:可以通过两种方法来改变module里面的参数型常量。 第一种是直接在生成一个实例时进行参数更改;第二种是用defparam在生成实例后再进行更改。

网络数据类型(wire,tri)与reg型的一般区别

- 网络数据类型表示结构实体例如门之间的物理连接。常用的网络数据类型包括wire型和tri型。网络数据类型的变量不能储存值,而且必须受到驱动器(例如门和连续赋值语句,assign)的驱动。

- wire型变量通常是用来表示单个门驱动或连续赋值语句驱动的网络数据类型,tri 型变量则用来表示多驱动器驱动的网络数据。

- 如果没有驱动器连接到网络类型(wire,tri)的变量,则该变量就是高阻(z)。 reg 型的变量默认为不定值x

- 在”always"模块内被赋值的每一个信号都必须是reg型。

- 注意:reg 型只表示被定义的信号将用在”always“模块内。

reg型数据与memory型数据的相似与区别

- verilog通过对 reg 型变量建立数组来对存储器建模,可以描述RAM型存储器,ROM存储器和reg文件。 在verilog 中没有多维数组存在。数组的维数不能大于2。

- memory 型数据是通过扩展 reg 型数据的地址范围来生成的。 eg: reg [7:0] mema[255:0] 定义了一个名为mema的存储器,包含有256个8位存储器。 注意:第二个括号的表达式必须是是常数表达式。

- reg [n-1:0] rega; //一个n为存储器。 可以使用 rega=0; 进行赋值

- reg mema [n-1,0]; // 一个由n个1位存储器构成的存储器组。 不能用 mema=0; 进行赋值。 类似于C中的数组。

- 读多位的memory型,可以用 reg[7:0] mema[255:0]; mema[56][2]; 。 先找到56号8位存储器,再读该8位存储器的第二位。

- 注意存储器属于寄存器数组类型。线网数据类型没有相应的存储器类型。

.运算符、表达式

- 进行取模运算时,结果值的符号为采用模运算式里第一个操作数的符号位。 eg: -10%3 = -1 ; 11%-3 = 2;

位运算符:

- ~ // 取反

- & // 按位与

- | // 按位或

- ^ // 按位异或

- ^~ // 按位同或

Verilog_Day2的更多相关文章

随机推荐

- Windows7设置锁屏密码

1.设置开机密码 2.设置屏幕保护程序 注意,不要选择无,选择其他的都可以,比如:气泡.彩带.空白

- 八、Web移动端Fixed布局的解决方案

移动端业务开发,iOS 下经常会有 fixed 元素和输入框(input 元素)同时存在的情况. 但是 fixed 元素在有软键盘唤起的情况下,会出现许多莫名其妙的问题. 这篇文章里就提供一个简单的有 ...

- linux安装memcached

一:为什么要使用memcached 瓶颈:互联网发展,特别在web2.0兴起之后,传统数据库开始出现瓶颈 1:对数据库的高并发读写 2:对海量数据库的处理(海量数据查找)memcache 是高性能的分 ...

- jQuery1.7版本之后的on方法

之前就一直受这个问题的困扰,在jQuery1.7版本之后添加了on方法,之前就了解过,其优越性高于 live(),bind(),delegate()等方法,在此之前项目中想用这个来测试结果发现,居然动 ...

- IHttpActionResult不识别解决办法

使用ASP.NET Web API构造基于restful风格web services,IHttpActionResult是一个很好的http结果返回接口.然而发现在vs2012开发环境中,System ...

- MySQL · 数据恢复 · undrop-for-innodb

Ref:https://www.aliyun.com/jiaocheng/1109809.html 摘要: 简介 undrop-for-innodb 是针对 innodb 的一套数据恢复工具,可以从 ...

- django 板块动态切换

需求:在同一页面的不同板块上可以实现动态切换,使用一个view实现,具体如下图所示,点击phy显示物理机列表,点击vm显示虚机列表,phy.vm对应的url均是动态生成: ...

- 解决由于显卡驱动BUG导致桌面右键卡顿的问题:bat文件源码

@ ECHO OFF%1 mshta vbscript:CreateObject("Shell.Application").ShellExecute("cmd.exe&q ...

- 铁乐学python_Day42_线程-信号量事件条件

铁乐学python_Day42_线程-信号量事件条件 线程中的信号量 同进程的一样,Semaphore管理一个内置的计数器, 每当调用acquire()时内置计数器-1:调用release() 时内置 ...

- 多路I/O复用(select、poll、epoll)的比较学习:

elect.poll.epoll之间的区别总结[整理] 转自:http://www.cnblogs.com/Anker/p/3265058.html select,poll,epoll都是IO多 ...