利用ZYNQ SOC快速打开算法验证通路(5)——system generator算法IP导入IP integrator

一、前言

利用FPGA设计算法一直以来都是热点,同样也是难点。将复杂的数学公式 模型通过硬件系统来搭建,在低延时 高并行性等优势背后极大提高了设计难度和开发周期。Xilinx公司的sysGen(system generator)工具扩展了MATLAB的simulink,提供很多IP Catalog中没有的基础模块和针对DSP应用的硬件模型。工程师利用丰富的模块和MATLAB强大的数据处理及可视化能力能够更快速完成设计与仿真验证工作。

二、sysGen算法系统设计

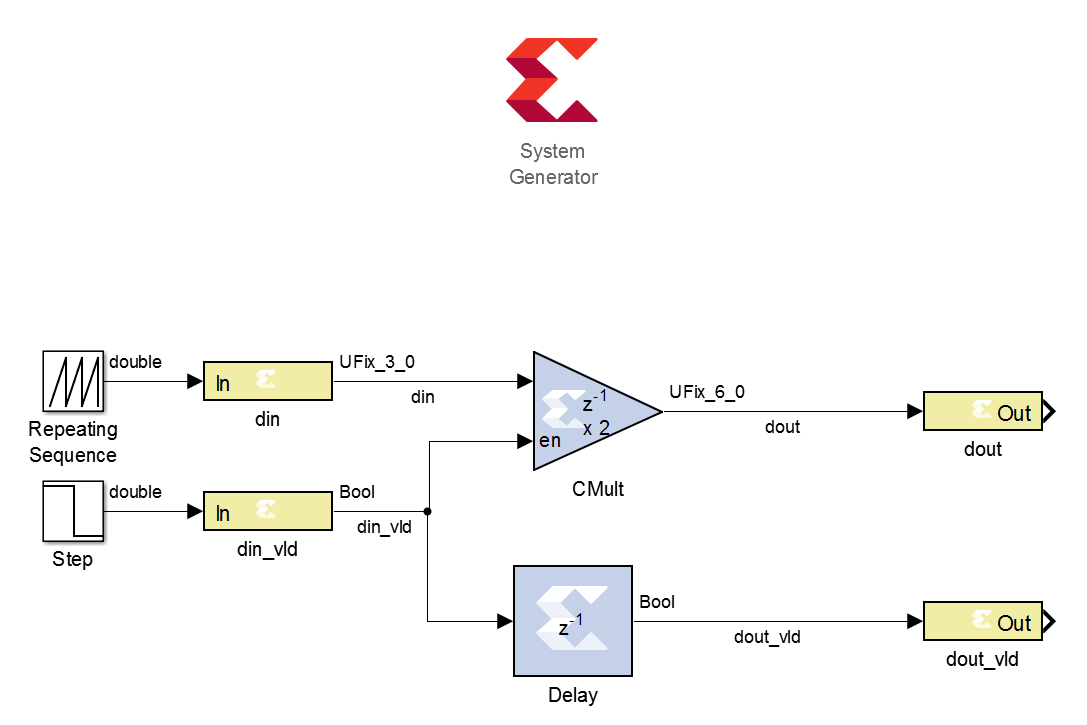

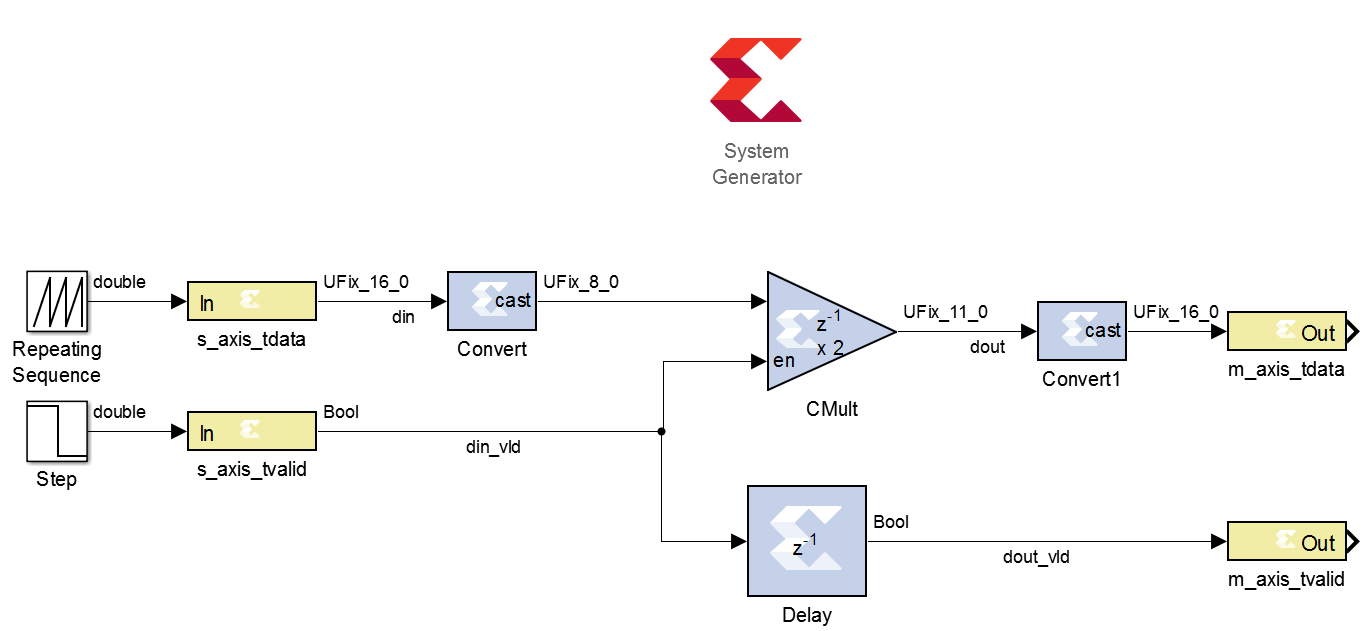

本文以个最简单的例子讲述利用sysGen搭建算法IP核,并集成到IP Integrator中作为ZYNQ PS端CPU的“定制外设”。仅用于测试目的。设计需求:在sysGen中搭建系统,将输入定点整数数据*2后输出,输入位宽为8bit。

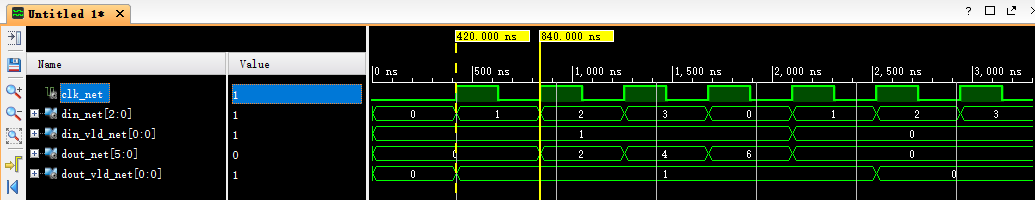

在System Generator token中设定仿真步长为1sec。点击需要观测的信号连线,右击选择Xilinx add to viewer。启动仿真并启动Xilinx waveform viewer:

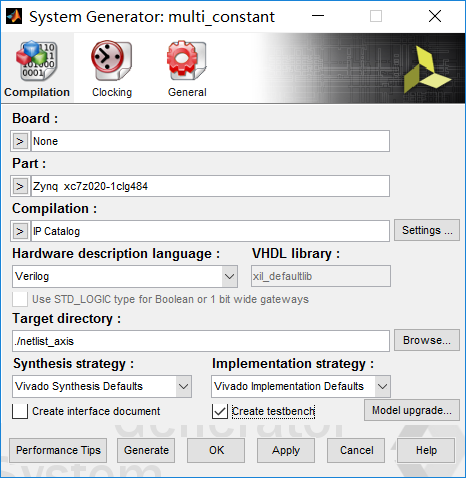

本质上就是调用Vivado的XSim工具进行行为仿真。仿真结果可见完成预期目标,现双击System Generator token ,选择Compiliation类型为IP Catalog并勾选Create testbench,按下Generate生成IP核。

三、仿真测试

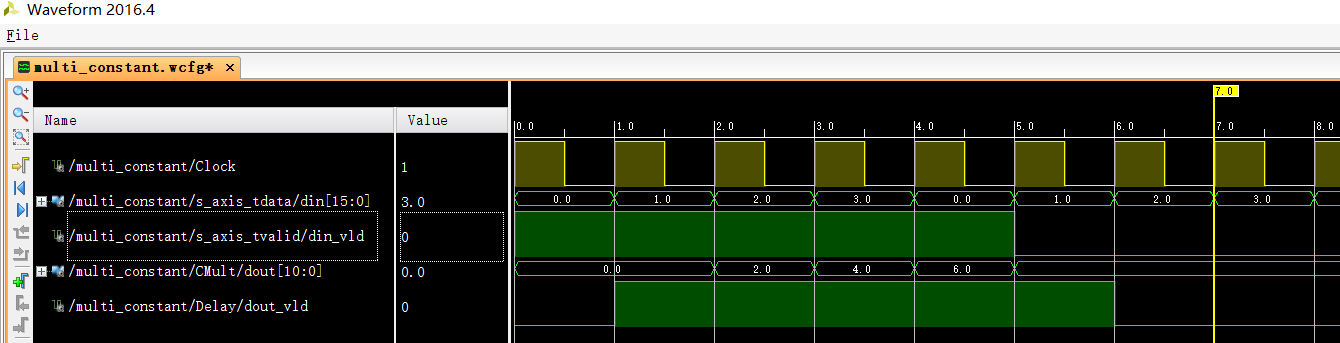

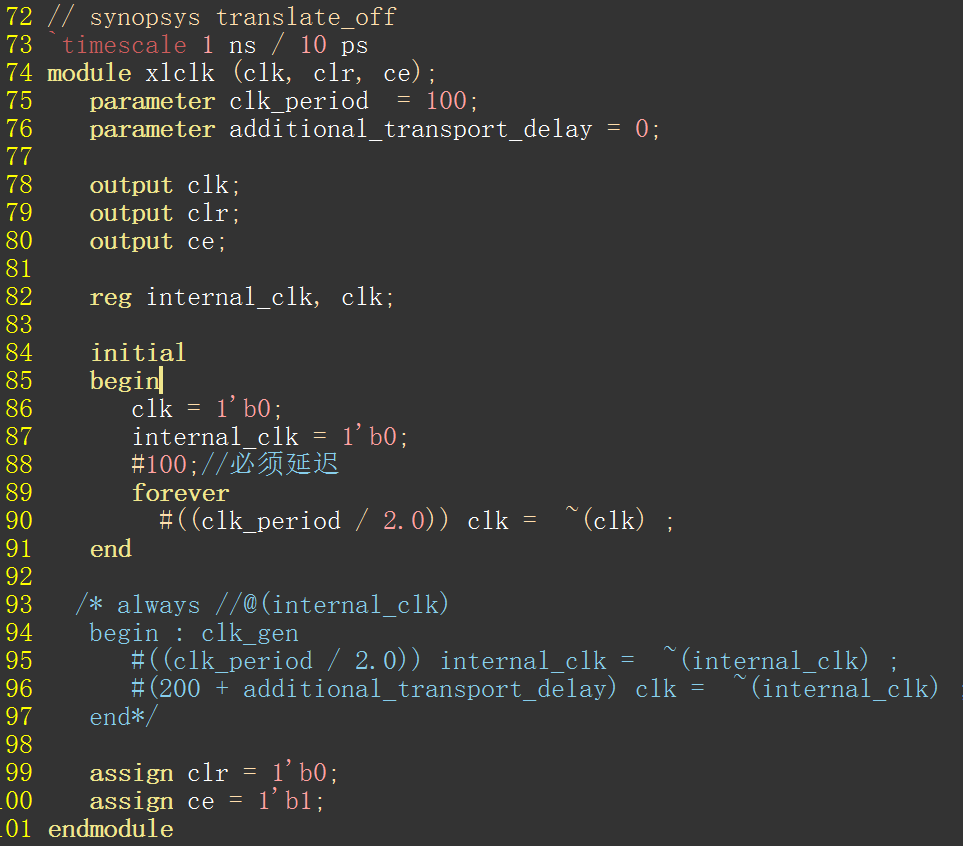

根据User Guide介绍sysGen是“周期和比特精准的”,我们还是在Vivado环境下再次验证下。netlist文件夹内子文件夹ip_catalog中为IP核示例工程,由于自动生成了testbench,打开后直接进行行为仿真。sysGen在创建testbench时会将经过gatein和gateout的数据储存到文件中,testbench进行的工作为:将gatein数据作为测试激励送入到相应设计输入端口,之后把设计输出得到结果与gateout文件数据进行逐一比较从而验证设计是否与sysGen环境下仿真结果一致。

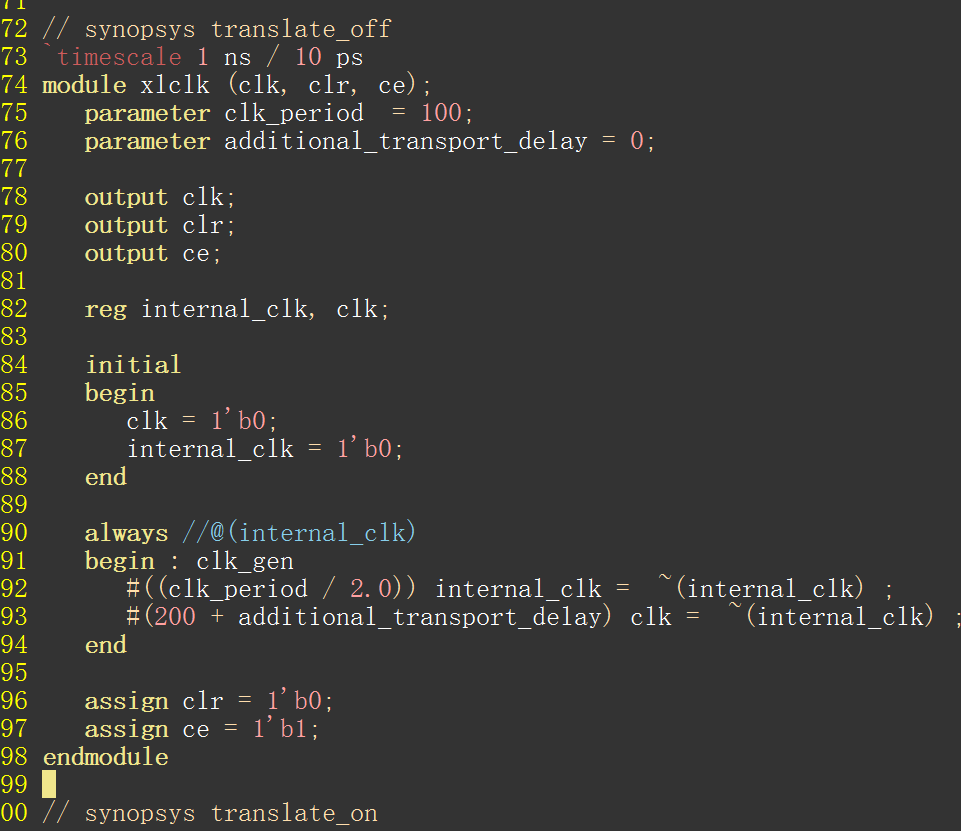

发现个比较有意思的现象,自动生成的testbench中clock生成并约束的50MHz,而是认为进行了拓展。

仿真波形如图:

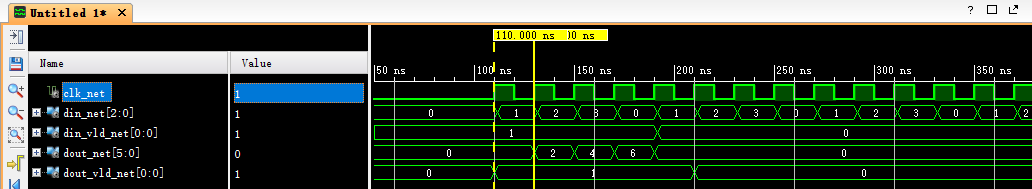

将clock处改动为50MHz后,经过测试发现如果系统一开始就输入数据,前几个数据没有被真正处理,输出错误。可能是软件BUG吧,不过这种情况也非常少见,实际系统中输入数据大多情况会启动一段时间后才输入。这里等待100ns后再启动clock翻转:

改动后仿真波形:

四、AXI-Stream总线形式IP

到此算法IP的设计与验证结束。如果想将这个IP核导入到IP Integrator中作为CPU的外设,其接口必须满足AXI总线标准,因此回到sysGen中更改端口名称和位宽。端口要符合AXI-Stream标准信号名称,位宽为8bit整数倍。

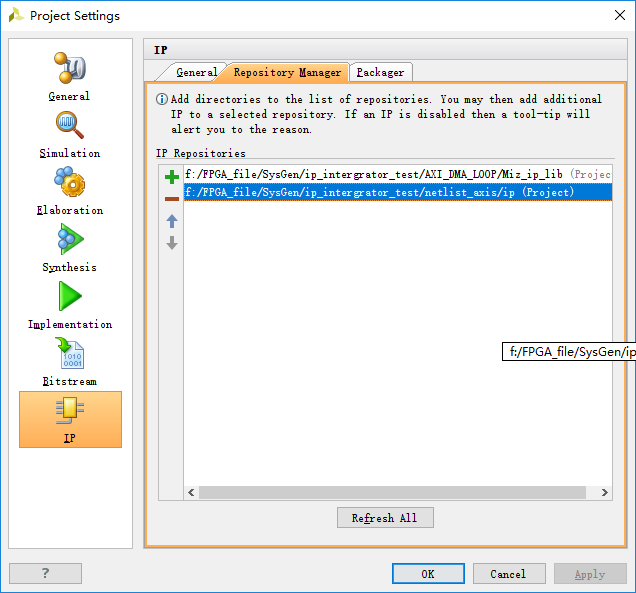

生成IP核后,打开新的工程,导入该IP核到repository。

五、Block Design系统搭建

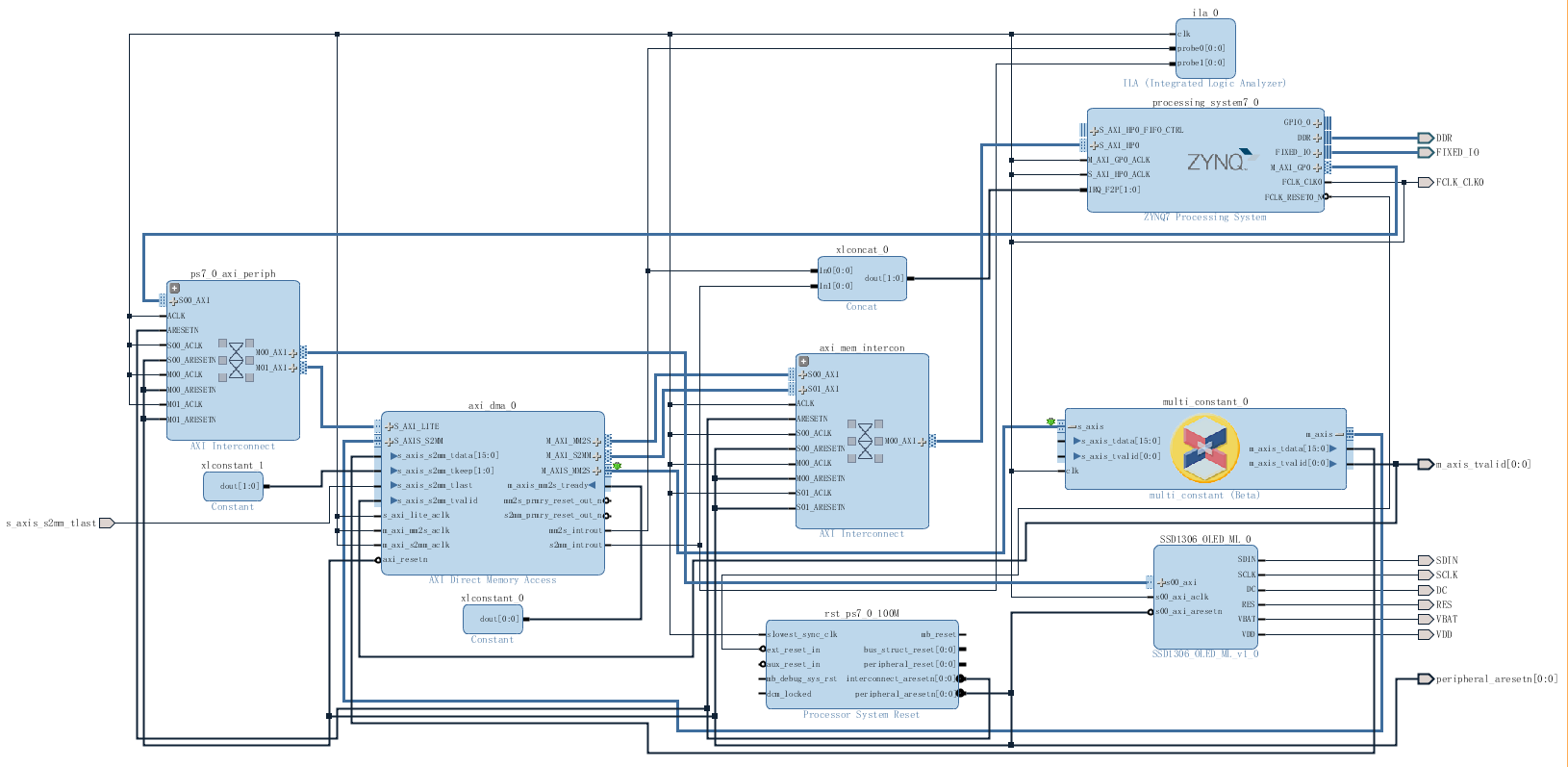

系统结构与上一篇该系列博文类似,均是以AXI DMA为核心的Loop系统,只是将AXI-Stream Data FIFO改成了自定义IP核。由于IP核slave和master接口只包含tdata和tvalid信号,因此需要添加接口衔接的一些简单逻辑。tready信号和tkeep信号直接连接constant使用常数驱动,DMA的s_axis_s2mm接口的tlast由wrapper内计数器逻辑驱动,将system中FCLK_CLK0 peripheral_aresetn m_axis_tvalid和s_axis_s2mm_tlast信号引出到wrapper中。

有一点比较坑:自定义IP通过AXI总线与DMA互联时,总线下相应的接口不一定会正确对应,所以需要分别将两端的每个接口相连。可以通过打开综合后的设计来确认连线无误。

自动生成wrapper后改动添加代码如下:

`timescale ps / ps module user_wrapper

(DC,

DDR_addr,

DDR_ba,

DDR_cas_n,

DDR_ck_n,

DDR_ck_p,

DDR_cke,

DDR_cs_n,

DDR_dm,

DDR_dq,

DDR_dqs_n,

DDR_dqs_p,

DDR_odt,

DDR_ras_n,

DDR_reset_n,

DDR_we_n,

//FCLK_CLK0,

FIXED_IO_ddr_vrn,

FIXED_IO_ddr_vrp,

FIXED_IO_mio,

FIXED_IO_ps_clk,

FIXED_IO_ps_porb,

FIXED_IO_ps_srstb,

RES,

SCLK,

SDIN,

VBAT,

VDD

//m_axis_tvalid,

//peripheral_aresetn,

//s_axis_s2mm_tlast

);

output DC;

inout [:]DDR_addr;

inout [:]DDR_ba;

inout DDR_cas_n;

inout DDR_ck_n;

inout DDR_ck_p;

inout DDR_cke;

inout DDR_cs_n;

inout [:]DDR_dm;

inout [:]DDR_dq;

inout [:]DDR_dqs_n;

inout [:]DDR_dqs_p;

inout DDR_odt;

inout DDR_ras_n;

inout DDR_reset_n;

inout DDR_we_n;

//output FCLK_CLK0;

inout FIXED_IO_ddr_vrn;

inout FIXED_IO_ddr_vrp;

inout [:]FIXED_IO_mio;

inout FIXED_IO_ps_clk;

inout FIXED_IO_ps_porb;

inout FIXED_IO_ps_srstb;

output RES;

output SCLK;

output SDIN;

output VBAT;

output VDD;

//output [0:0]m_axis_tvalid;

//output [0:0]peripheral_aresetn;

//input s_axis_s2mm_tlast; localparam DATA_NUM = ; wire DC;

wire [:]DDR_addr;

wire [:]DDR_ba;

wire DDR_cas_n;

wire DDR_ck_n;

wire DDR_ck_p;

wire DDR_cke;

wire DDR_cs_n;

wire [:]DDR_dm;

wire [:]DDR_dq;

wire [:]DDR_dqs_n;

wire [:]DDR_dqs_p;

wire DDR_odt;

wire DDR_ras_n;

wire DDR_reset_n;

wire DDR_we_n;

wire FCLK_CLK0;

wire FIXED_IO_ddr_vrn;

wire FIXED_IO_ddr_vrp;

wire [:]FIXED_IO_mio;

wire FIXED_IO_ps_clk;

wire FIXED_IO_ps_porb;

wire FIXED_IO_ps_srstb;

wire RES;

wire SCLK;

wire SDIN;

wire VBAT;

wire VDD;

wire [:]m_axis_tvalid;

wire [:]peripheral_aresetn;

wire s_axis_s2mm_tlast; reg [-:] cnt;

wire add_cnt;

wire end_cnt; system system_i

(.DC(DC),

.DDR_addr(DDR_addr),

.DDR_ba(DDR_ba),

.DDR_cas_n(DDR_cas_n),

.DDR_ck_n(DDR_ck_n),

.DDR_ck_p(DDR_ck_p),

.DDR_cke(DDR_cke),

.DDR_cs_n(DDR_cs_n),

.DDR_dm(DDR_dm),

.DDR_dq(DDR_dq),

.DDR_dqs_n(DDR_dqs_n),

.DDR_dqs_p(DDR_dqs_p),

.DDR_odt(DDR_odt),

.DDR_ras_n(DDR_ras_n),

.DDR_reset_n(DDR_reset_n),

.DDR_we_n(DDR_we_n),

.FCLK_CLK0(FCLK_CLK0),

.FIXED_IO_ddr_vrn(FIXED_IO_ddr_vrn),

.FIXED_IO_ddr_vrp(FIXED_IO_ddr_vrp),

.FIXED_IO_mio(FIXED_IO_mio),

.FIXED_IO_ps_clk(FIXED_IO_ps_clk),

.FIXED_IO_ps_porb(FIXED_IO_ps_porb),

.FIXED_IO_ps_srstb(FIXED_IO_ps_srstb),

.RES(RES),

.SCLK(SCLK),

.SDIN(SDIN),

.VBAT(VBAT),

.VDD(VDD),

.m_axis_tvalid(m_axis_tvalid),

.peripheral_aresetn(peripheral_aresetn),

.s_axis_s2mm_tlast(s_axis_s2mm_tlast)); always @(posedge FCLK_CLK0)begin

if(!peripheral_aresetn)begin

cnt <= ;

end

else if(add_cnt)begin

if(end_cnt)

cnt <= ;

else

cnt <= cnt + ;

end

end assign add_cnt = m_axis_tvalid;

assign end_cnt = add_cnt && cnt== DATA_NUM-; assign s_axis_s2mm_tlast = end_cnt; endmodule

user_wrapper

当自定义IP核输出256个数据时,拉高tlast信号结束传输。打开综合后的设计,添加调试探针,抓取DMA与自定义IP之间的接口信号,set up debug后完成接下来的流程。

六、软硬件联调

在硬件系统中定义数据帧长度为256个,数据位宽为16bit,因此C代码中DMA启动传输函数中数据长度参数为512byte。测试数据生成与检测代码非常简单:

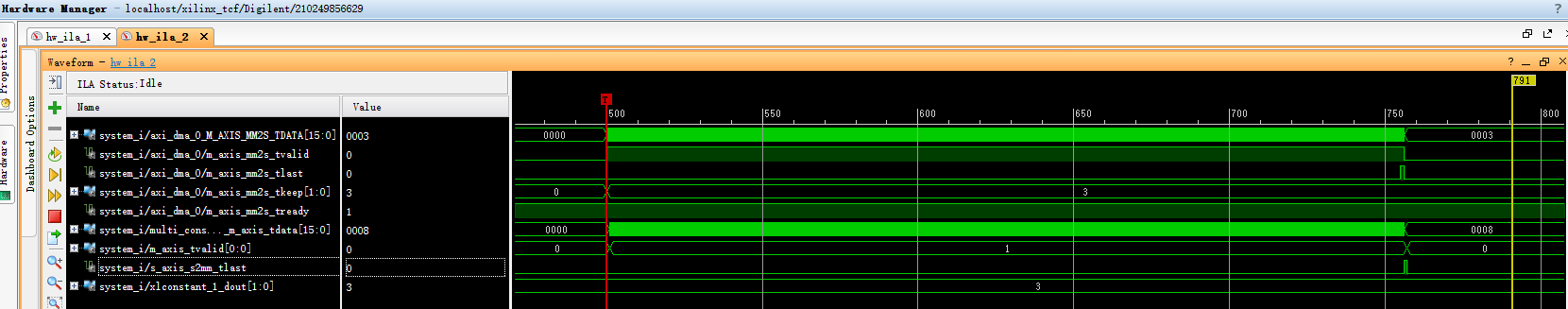

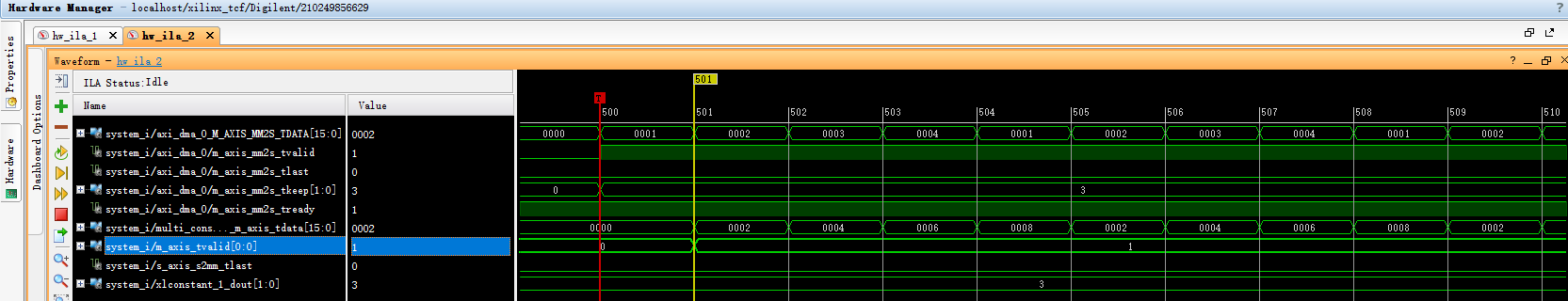

我们直接查看ILA抓取AXI S总线波形:

看到CPU产生数据从1到4重复递增,IP核输出结果从2到8重复递增,输出为输入的2倍。

传输完成后进入DMA发送和接收中断,软件检测结果正确。在Memory窗口能够直接查看内存绝对地址里的数据,选定DDR接收缓存区起始地址,其中的数据与AXI总线传回数据一致,证明系统联调成功。之后任意算法模块均可采用本文方式进行设计和集成,可以说一劳永逸!

利用ZYNQ SOC快速打开算法验证通路(5)——system generator算法IP导入IP integrator的更多相关文章

- 利用ZYNQ SOC快速打开算法验证通路(1)——MATLAB浮点数与定点二进制补码互转

最近本人一直在学习ZYNQ SOC的使用,目的是应对科研需要,做出通用的算法验证平台.大概思想是:ZYNQ PS端负责与MATLAB等上位机数据分析与可视化软件交互:既可传输数据,也能通过上位机配置更 ...

- 利用ZYNQ SOC快速打开算法验证通路(6)——利用AXI总线实时配置sysGen子系统

利用ZYNQ验证算法的一大优势在于,可以在上位机发送指令借助CPU的控制能力和C语言易开发特点,实时配置算法模块的工作模式.参数等对来对其算法模块性能进行全面的评估.最重要的是无需重新综合硬件模块. ...

- 利用ZYNQ SOC快速打开算法验证通路(4)——AXI DMA使用解析及环路测试

一.AXI DMA介绍 本篇博文讲述AXI DMA的一些使用总结,硬件IP子系统搭建与SDK C代码封装参考米联客ZYNQ教程.若想让ZYNQ的PS与PL两部分高速数据传输,需要利用PS的HP(高性能 ...

- 利用ZYNQ SOC快速打开算法验证通路(2)——数据传输最简方案:网络调试助手+W5500协议栈芯片

在上一篇该系列博文中讲解了MATLAB待处理数据写入.bin二进制数据文件的过程,接下来需要将数据通过以太网发送到ZYNQ验证平台.之前了解过Xilinx公司面向DSP开发的System Genera ...

- 利用ZYNQ SOC快速打开算法验证通路(6)——LWIP实现千兆TCP/IP网络传输

一.前言 之前ZYNQ与PC之间的网络连接依赖于外接硬件协议栈芯片,虽然C驱动非常简单,但网络带宽受限.现采用LWIP+PS端MAC控制器+PHY芯片的通用架构.关于LWIP库,已经有很多现成的资料和 ...

- 利用ZYNQ SOC快速打开算法验证通路(3)——PS端DMA缓存数据到PS端DDR

上篇该系列博文中讲述W5500接收到上位机传输的数据,此后需要将数据缓存起来.当数据量较大或者其他数据带宽较高的情况下,片上缓存(OCM)已无法满足需求,这时需要将大量数据保存在外挂的DDR SDRA ...

- 利用Zynq Soc创建一个嵌入式工程

英文题目:Using the Zynq SoC Processing System,参考自ADI的ug1165文档. 利用Zynq Soc创建一个嵌入式工程,该工程总体上包括五个步骤: 步骤一.新建空 ...

- 基于Python的函数回归算法验证

看机器学习看到了回归函数,看了一半看不下去了,看到能用方差进行函数回归,又手痒痒了,自己推公式写代码验证: 常见的最小二乘法是一阶函数回归回归方法就是寻找方差的最小值y = kx + bxi, yiy ...

- 支持向量机(SVM)利用网格搜索和交叉验证进行参数选择

上一回有个读者问我:回归模型与分类模型的区别在哪?有什么不同,我在这里给他回答一下 : : : : 回归问题通常是用来预测一个值,如预测房价.未来的天气情况等等,例如一个产品的实际价格为500元,通过 ...

随机推荐

- 优化之Normalizer组件

Normalizer会产生记录,尽可能的将Normalizer组件靠近Target ---------------------------------------------------------- ...

- 第一次写html网页

步骤一:(在notpad中写) <html> <head> <title>登录页面</title> </head> <body> ...

- IO复用(较详细)

进程与线程的描述 一个进程至少会创建一个线程,多个线程共享一个程序进程的内存.程序的运行最终是靠线程来完成操作的.线程的数量跟CPU核数有关,一个核最多能发出两个线程.线程的操作主要分为:一:给CPU ...

- js获取input上传文件名和后缀

var file = $("#filedata").val(); var pos = file.lastIndexOf("\\"); var filename ...

- 微信小程序使用nginx方向代理实现内嵌非业务域名

通过上一篇文章简单介绍了一下微信小程序的新组件<web-view>,实现了在小程序中内嵌业务域名的功能.但是boss要的小程序中不仅想内嵌业务域名,还想要打开一些非业务域名(无法操作web ...

- CompletableFuture基本用法

异步计算 所谓异步调用其实就是实现一个可无需等待被调用函数的返回值而让操作继续运行的方法.在 Java 语言中,简单的讲就是另启一个线程来完成调用中的部分计算,使调用继续运行或返回,而不需要等待计算结 ...

- TypeError: unorderable types: str() >= int()

1.问题描述 age=input('please enter your age') if age >=18: print('your age is',age) print('adult') el ...

- 15分钟在阿里云Kubernetes服务上快速建立Jenkins X Platform并运用GitOps管理应用发布

本文主要介绍如何在阿里云容器服务Kubernetes上快速安装部署Jenkins X Platform并结合demo实践演示GitOps的操作流程. 注意:本文中使用的jx工具.cloud-envir ...

- 手把手教您将 libreoffice 移植到函数计算平台

LibreOffice 是由文档基金会开发的自由及开放源代码的办公室套件.LibreOffice 套件包含文字处理器.电子表格.演示文稿程序.矢量图形编辑器和图表工具.数据库管理程序及创建和编辑数学公 ...

- php ip2long负数的问题

大家可能都知道php提供了ip2long与long2ip方法对ip地址处理.抛砖引玉,说点概念性滴: 1.ip2long — 将一个IPV4的字符串互联网协议转换成数字格式 int ip2long ( ...