FPGA DDR3调试

FPGA DDR3调试

Spartan6 FPGA芯片中集成了MCB硬核,它可以支持到DDR3。在Xilinx的开发工具Xilinx ISE中提供了MIG IP核,设计者可以用它来直接生成 DDR3 控制器设计模块,并通过 MIG 的 GUI 图形界面完成相关配置。

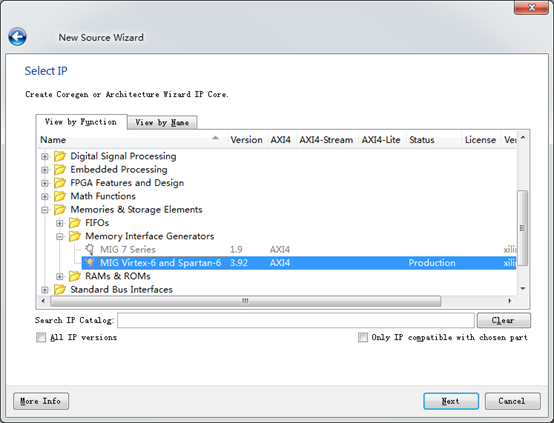

首先,建立ISE工程,并添加MIG IP核,

接下来进行MIG IP核配置,这里列出主要的部分,

这里选择DDR的类型,并选择使用Spartan6的哪一个bank,一般选择左边的bank,

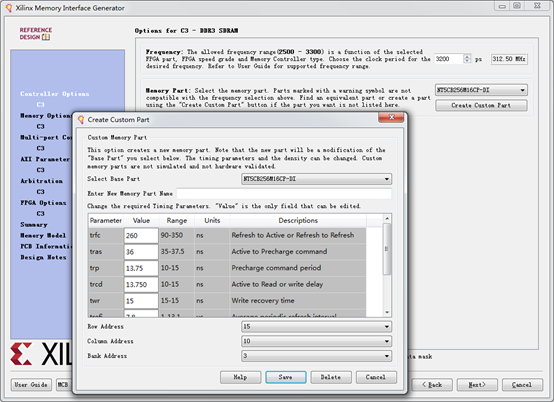

这里设置DDR3的时钟频率以及DDR3的设备型号,Xilinx列举了部分DDR3型号,如果没有,则需要点击“create custom part”自定义型号,这里注意在自定义型号的时候最好选择一个模板与自己的DDR3型号数据位宽一样的,因为自定义选项中无法修改数据位宽(当然也可以在生成的代码中修改位宽),在自定义界面中,主要设置与DDR3有关的几个时间参数以及地址线宽度,这些信息都可以在芯片的Datasheet上找到,

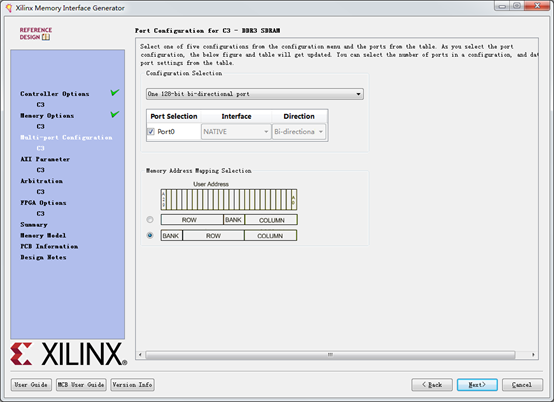

这里选择不同的端口方式,可以选择一个端口,也可以选择不同位宽的多个端口,选择多个端口时,可以对不同的端口进行读写控制,这在乒乓模式操作DDR3时有用(如利用P0端口对地址1进行写操作,同时利用P1端口对地址2进行读操作;完成一次读写时,P0端口对地址2进行写操作,同时利用P1端口对地址1进行读操作),以及地址映射关系(可以查看:Spartan-6 FPGA Memory Interface Solutions 和 Spartan-6 FPGA Memory Controller),

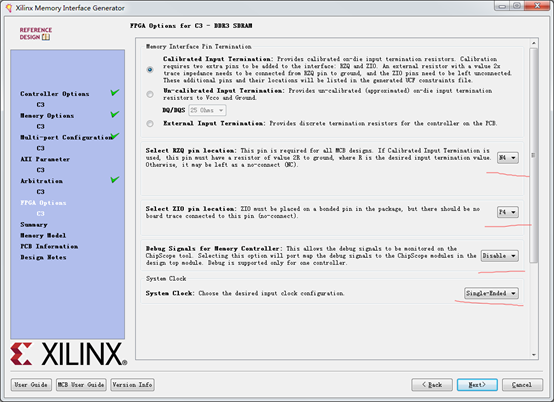

这里设置RZQ和ZIO的引脚,需要根据硬件电路来进行选择,同时可以选择是否使用chipscope调试,如果自己添加chipscope的话就不需要。

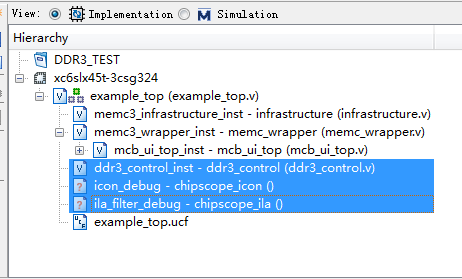

生成MIG IP核以后,可以新建工程,在user_design文件下拷贝以下文件(选中部分为自己添加),然后进行代码修改。

首先,完成约束文件的修改,使之与自己的硬件设备一致,一般有以下几点:

1、 VCCAUX 电压修改

CONFIG VCCAUX=3.3; # Valid values are 2.5 and 3.3

2、 系统时钟输入的周期,需要跟PCB板上的晶振频率一样。

NET "memc3_infrastructure_inst/sys_clk_ibufg" TNM_NET = "SYS_CLK3";

TIMESPEC "TS_SYS_CLK3" = PERIOD "SYS_CLK3" 20 ns HIGH 50 %;

3、 修改部分管脚电压和位置,如时钟、复位管脚等

接下来完成顶层文件的设置,一般有以下几点:

1、 复位极性与PCB板一致

2、 根据板子上的时钟修改DDR3时钟配置部分,我使用的时钟输入为50Mhz,由于在MIG中设置了 DDR3 的频率为312.5MHz,且DDR3是上下沿采样,所以FPGA内部 DDR3控制器的时钟需要625MHz,所以这里先把时钟频率倍频25, 再分频2,得625Mh的CLKOUT0和CLKOUT1, 再分频 8分别得到 user interface 的时钟和 calibration 的时钟 78.125Mhz。

3、 删除mcb_traffic_gen相关例化代码,编写自己的DDR3测试代码,并例化

4、 编写DDR3测试代码,需参考Spartan-6 FPGA Memory Controller中的读写时序,主要参考,主要包含命令、数据、地址,本测试中,由于采用了128bit的单端口,所以每写一个数据,地址线需要加8,若涉及到突发读写,则地址线也要相应按8的倍数增加。

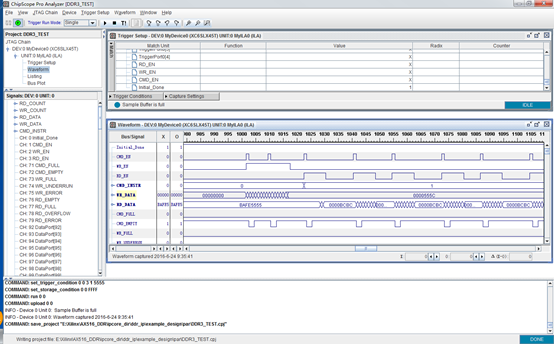

5、最后添加chipscope,完成测试

FPGA DDR3调试的更多相关文章

- DDR3调试总结

DDR3调试总结 本文为原创,转载请注明作者与出处 http://blog.csdn.net/hanfei_1/article/details/70546010 以前同是DDR3的无知少年,由于项目需 ...

- Lattice FPGA 板子 调试笔记

最近在调试LATTICE FPGA 做的视频板子,颇不顺利,所以记录下来作为以后的参考: 1.FPGA的IO口不是所有的都是双向的,有些有特殊作用的是单向的. 在查阅 LatticeECP3-17E ...

- DDR3调试记录

FPGA采集视频数据并写到DDR3,然后从DDR3读出并送给显示终端显示.不能稳定显示.但用FPGA内部逻辑产生color bar写到DDR3后读出来显示正常.因此DDR3部分逻辑没有问题 ...

- ddr3调试经验分享(一)——modelsim实现对vivado中的MIG ddr3的仿真

Vivado中的MIG已经集成了modelsim仿真环境,是不是所有IP 都有这个福利呢,不知道哦,没空去验证. 第一步:使用vivado中的MIG IP生成一堆东西 ,这个过程自己百度.或者是ug5 ...

- vivado2016.2下系统自带DDR3 ip例程仿真运行

背景:从ISE14.7迁移到vivado2016.2. xilinx的软件改的真是不一般的大.两个软件操作差距真是让人想骂人.由于项目需要,准备调试DDR3.对于新手来说,例化一个DDR3 ip.如果 ...

- 给FPGA初学者的建议——不要浮躁(转)

原作者:http://hi.baidu.com/zhoubin7020 作为FPGA新人常常在论坛上问,用什么语言啊,用什么软件啊,用那个公司的芯片等问题.我个人认为学习FPGA和学习单片机有相同的道 ...

- FPGA设计思想与技巧(转载)

题记:这个笔记不是特权同学自己整理的,特权同学只是对这个笔记做了一下完善,也忘了是从那DOWNLOAD来的,首先对整理者表示感谢.这些知识点确实都很实用,这些设计思想或者也可以说是经验吧,是很值得每一 ...

- 用FPGA对ASIC进行原型验证的过程(转)

用FPGA对ASIC进行原型验证的过程 reference:http://xilinx.eetrend.com/d6-xilinx/article/2018-10/13736.html 鉴 ...

- SoC FPGA JTAG电路设计 要点

JTAG协议制定了一种边界扫描的规范,边界扫描架构提供了有效的测试布局紧凑的PCB板上元件的能力.边界扫描可以在不使用物理测试探针的情况下测试引脚连接,并在器件正常工作的过程中捕获运行数据. SoC ...

随机推荐

- OpenWRT 添加应用程序开机启动方法

方法一:在/etc/inid.d/目录下新建启动脚本. 方法二:直接在/etc/rc.local 中添加启动命令,如:./usr/bin/relay &

- OpenWRT 恢复出厂设置命令

如果通过无线或者有线口无法连接到router,可以用恢复某些设置重新设置路由器. 1. 开机,等着一个工作灯亮的时候立即按下rest键2秒,然后就开始拼命闪烁,很好现在进入failsafe模式了. 2 ...

- Java方法使用的有点总结

方法使用的优点: 1-将解决问题的方法与主函数代码分开,逻辑更清晰,代码可读性更强. 2-若方法出错,则程序可以缩小为只在该方法中查找错误,使代码更容易调试. 3-方法是解决一类问题的抽象,一旦写成功 ...

- 基于FFMpeg的C#录屏全攻略

最近负责一个录屏的小项目,需要录制Windows窗口内容并压缩保存到指定文件夹,本想使用已有的录屏软件,但是本着学习的态度去探索了FFMpeg,本文主要介绍基于FFMpeg开源项目的C#录屏软件开发. ...

- Iozone

参考地址:iozone使用技巧.iozone和Fio安装测试说明 iozone介绍 iozone(www.iozone.org)是一个文件系统的benchmark工具,可以测试不同的操作系统中文件系统 ...

- 【转】S3C2440与SDRAM NorFlash NandFlash连线分析

一.SDRAM(HY57V561620F)连线分析 1. S3C2440 有27根地址线ADDR[26:0],8根片选信号ngcs0-ngcs7,对应bank0-bank7,当访问bankx 的地址 ...

- IO 调优

磁盘优化 1.增加缓存 2.优化磁盘的管理系统 3.设计合理的磁盘存储数据块 4.应用合理的RAID策略 TCP网络参数调优 网络IO优化 1.减少网络交互次数 2.减少网络传输数据量的大小 3.尽量 ...

- mysql必知必会系列(一)

mysql必知必会系列是本人在读<mysql必知必会>中的笔记,方便自己以后查看. MySQL. Oracle以及Microsoft SQL Server等数据库是基于客户机-服务器的数据 ...

- 在C#中winform程序中应用nlog日志工具

在C#中winform程序中应用nlog日志工具,配置文件简单应用. 文件名 nlog.config,请注意修改属性为"始终复制",发布时候容易遇到不存在文件的错误提示. 通过Nu ...

- session失效问题

具体设置很简单,方法有三种: ()在主页面或者公共页面中加入:session.setMaxInactiveInterval();参数600单位是秒,即在没有10分钟活动后,session将失效. 这里 ...