FIFO IP核仿真

FIFO IP核仿真

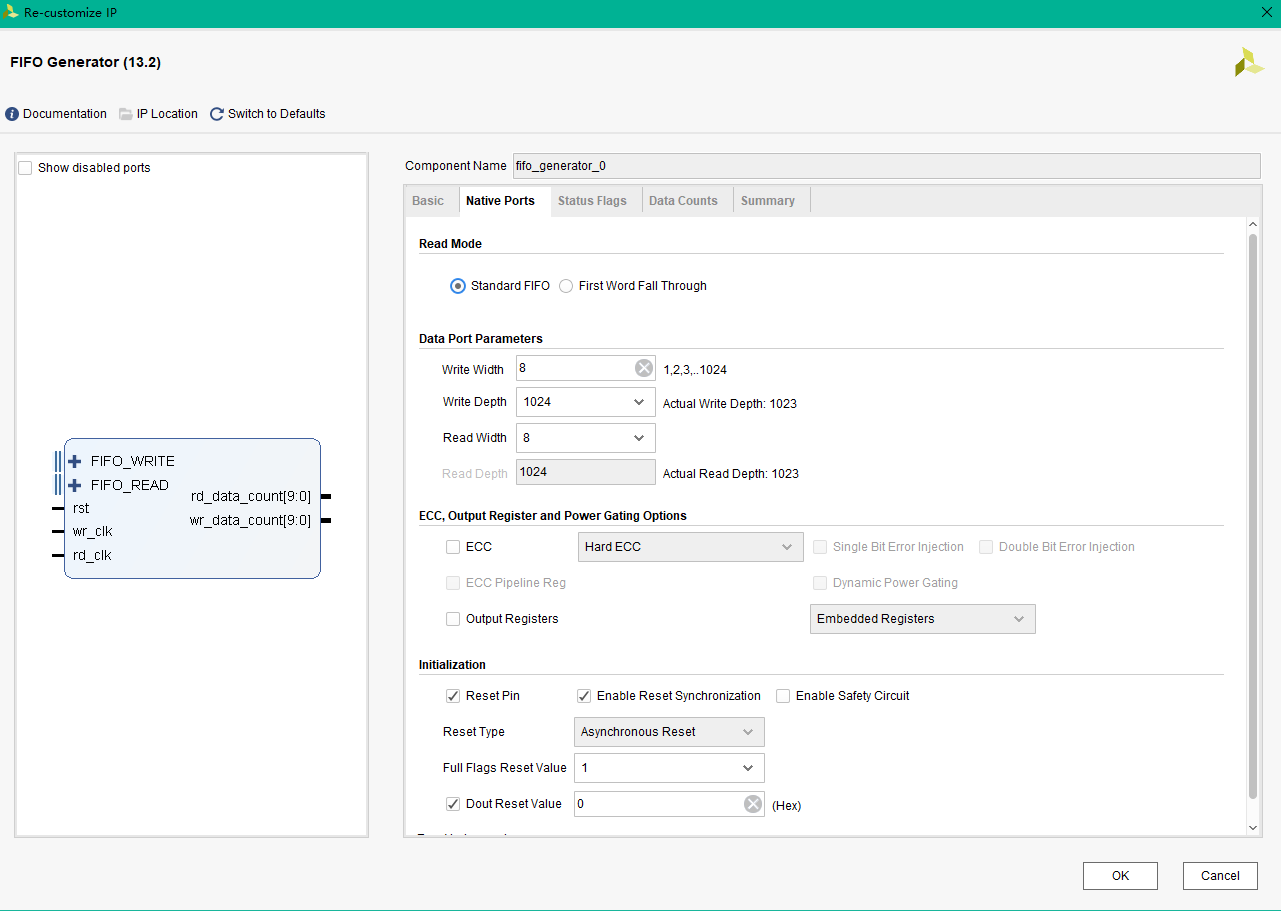

1.FIFO IP核配置

2.FIFO测试逻辑代码

首先往FIFO里面写入512个数据(FIFO深度的一半),然后再开始同时往FIFO里面写入,读出数据。FIFO读和写的时钟域不同,对于不同时钟域的信号应该进行区分,状态机也应该分开来写。

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: chensimin

//

// Create Date: 2017/10/23 16:11:32

// Design Name:

// Module Name: top

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////// module top(

rst,

wr_clk,

rd_clk,

dout,

full,

empty,

rd_data_count,

wr_data_count

); //input

input rst;

input wr_clk;

input rd_clk; //output

output [:]dout;

output full;

output empty;

output [:]rd_data_count;

output [:]wr_data_count; //write state

reg [:]i;

reg read_start;

reg [:]din_r;

reg clear_fifo_full;

reg wr_en_r;

wire wr_en;

wire [:]din;

wire [:]wr_data_count;

wire full;

always@(posedge wr_clk)

begin

if(rst)

begin

wr_en_r <= 'b0;

i <= 'd0;

read_start <= 'b0;

clear_fifo_full <= 'b0;

din_r <= 'd0;

end

else

begin

case(i)

:

begin

if(!full) begin wr_en_r <= 'b1; i<=i+1'b1; end

else wr_en_r <= 'b0;

end

:

begin

if(wr_data_count =='d512) begin read_start <=1'b1; din_r <= din_r +'b1; i<=i+1'b1; end

else din_r <= din_r +'b1;

end

:

begin

if(full) begin clear_fifo_full <= 'b1; wr_en_r <= 1'b0; i<='d0; end

else din_r <= din_r +'b1;

end

endcase

end

end assign wr_en = wr_en_r;

assign din = din_r; //read state

reg rd_en_r;

reg [:]j;

reg clear_fifo_empty;

wire rd_en;

always@(posedge rd_clk)

begin

if(rst)

begin

rd_en_r <= 'b0;

j <= 'd0;

clear_fifo_empty <= 'b0;

end

else

begin

case(j)

:

begin

if(read_start & !empty) begin rd_en_r <= 'b1; j<=j+1'b1; end

else rd_en_r <= 'b0;

end

:

begin

if(empty) begin clear_fifo_empty <= 'b1; rd_en_r <= 1'b0; j<='d0; end

else rd_en_r <= 'b1;

end

endcase

end

end assign rd_en = rd_en_r; fifo_generator_0 U1 (

.rst(rst), // input wire rst

.wr_clk(wr_clk), // input wire wr_clk

.rd_clk(rd_clk), // input wire rd_clk

.din(din), // input wire [7 : 0] din

.wr_en(wr_en), // input wire wr_en

.rd_en(rd_en), // input wire rd_en

.dout(dout), // output wire [7 : 0] dout

.full(full), // output wire full

.empty(empty), // output wire empty

.rd_data_count(rd_data_count), // output wire [9 : 0] rd_data_count

.wr_data_count(wr_data_count) // output wire [9 : 0] wr_data_count

); endmodule

3.测试脚本

add_force {/top/rst} -radix hex { 0ns} { 150000ps}

add_force {/top/wr_clk} -radix hex { 0ns} { 50000ps} -repeat_every 100000ps

add_force {/top/rd_clk} -radix hex { 0ns} { 49500ps} -repeat_every 99000ps

4.仿真波形分析

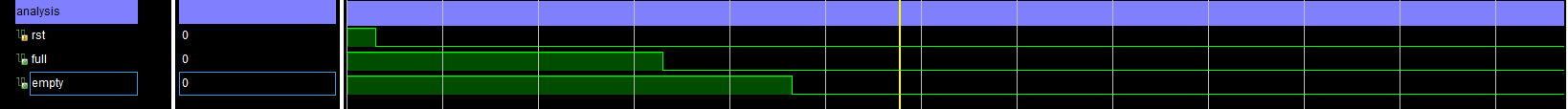

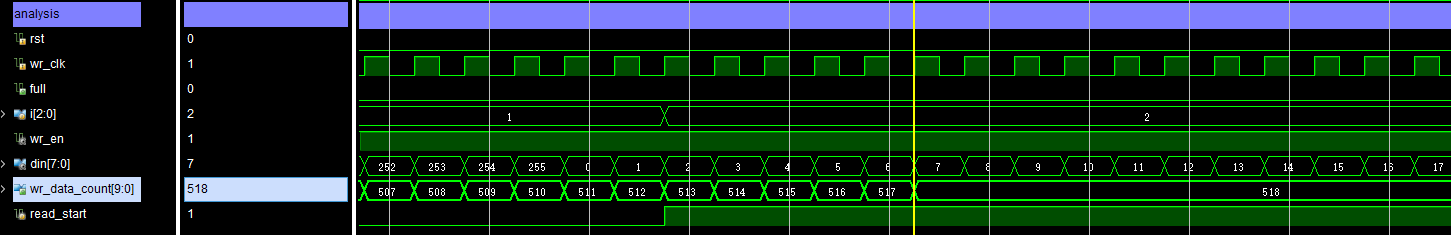

仿真波形图

对FIFO进行复位操作,开始full,empty都会拉高一段时间,然后才会恢复正常。

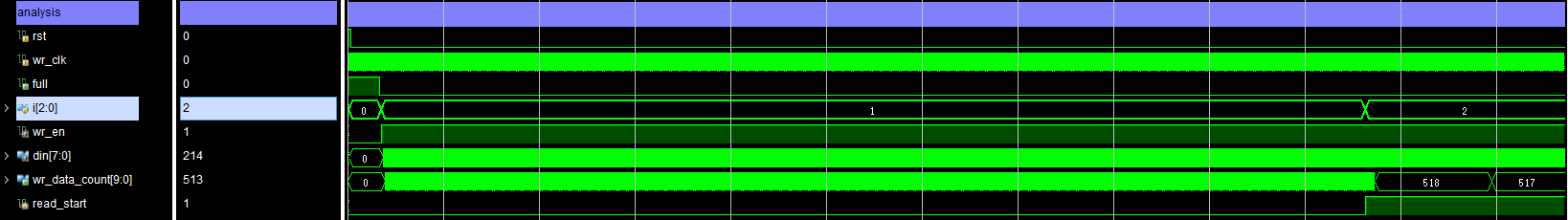

与写状态有关的信号分析

当full恢复正常后,写使能,同时状态机跳转。

当写入512个数据后(wr_data_count == 512),read_start信号开始拉高,FIFO开始读出数据,同时状态机也在此刻跳转,下一个状态再写数据的同时,也在监测FIFO是否已经被写满。

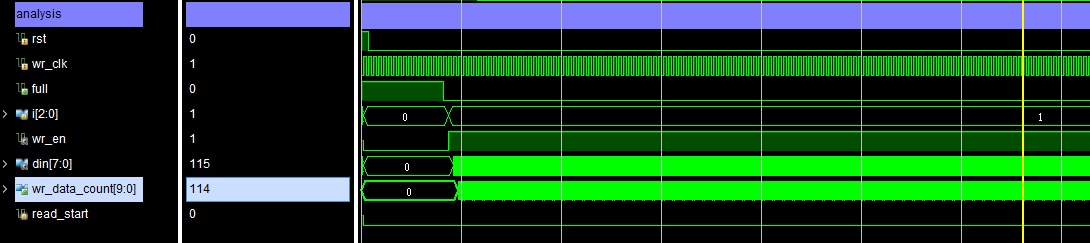

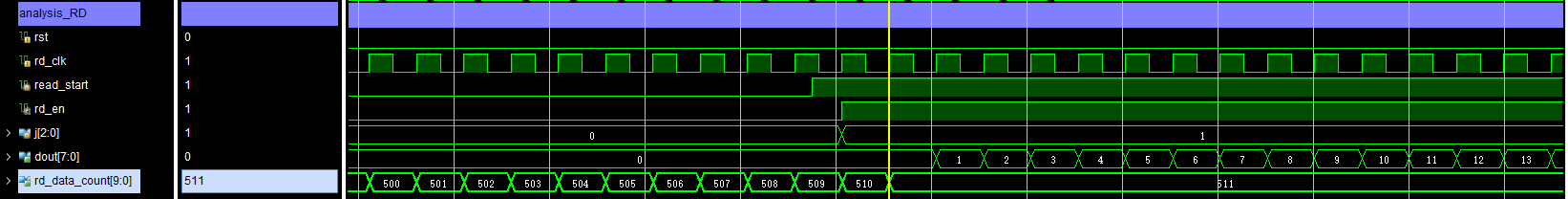

下面来看FIFO读数据端的仿真波形

当read_start信号拉高时,re_en信号开始拉高,FIFO才开始从dout端口读出数据,可以看到,刚开读出的数据为FIFO din端口最先写入的数据。从rd_data_count端口可以看到,此时FIFO里面已经有500多个数据可以读。

结论:仿真结果与预期相符。

FIFO IP核仿真的更多相关文章

- FIFO IP核

转载: 说白了,IP核就是别人做好了的硬件模块,提供完整的用户接口和说明文档,更复杂的还有示例工程,你只要能用好这个IP核,设计已经完成一半了.说起来容易,从冗长的英文文档和网上各个非标准教程中汲取所 ...

- Altera FIFO IP核时序说明

ALTERA在LPM(library of parameterized mudules)库中提供了参数可配置的单时钟FIFO(SCFIFO)和双时钟FIFO(DCFIFO).FIFO主要应用在需要数据 ...

- FPGA基础学习(2) -- FIFO IP核(Quartus)

ALTERA在LPM(library of parameterized mudules)库中提供了参数可配置的单时钟FIFO(SCFIFO)和双时钟FIFO(DCFIFO).FIFO主要应用在需要数据 ...

- modelsim-altera IP核仿真

modelsim 仿真fifo时出现 Instantiation of 'scfifo' failed. The design unit was not found. 2012-07-21 13:27 ...

- IP核之初——FIFO添加以太网MAC头部

本文设计思路源自明德扬至简设计法.在之前的几篇博文中,由于设计比较简单,所有的功能都是用verilogHDL代码编写实现的.我们要学会站在巨人的肩膀上,这时候就该IP核登场了! 说白了,IP核就是别人 ...

- Altera三速以太网IP核快速仿真与使用(上篇)

对于比较高级的ip核,altera一般都会提供仿真案例,网上有关于这个IP核的各种仿真方法,但都比较繁琐,前几日,朋友跟我分享了一个比较快速高效的仿真方法,这个方法也是他摸索折腾了一段时间才总结出来的 ...

- 用Modelsim SE 直接仿真 Altera(Intel PSG) IP核 需要注意的问题

如果我们直接用Modelsim SE仿真 Altera IP核,首先会进入Quartus II目录下找到IP核对应的仿真库源文件,然后在Modelsim SE中进行编译,添加到Modelsim SE的 ...

- IP核——FIFO

一.Quartus 1.打开Quartus ii,点击Tools---MegaWizard Plug-In Manager 2.弹出创建页面,选择Creat a new custom megafunc ...

- 调用altera IP核的仿真流程—下

调用altera IP核的仿真流程—下 编译 在 WorkSpace 窗口的 counter_tst.v上点击右键,如果选择Compile selected 则编译选中的文件,Compile All是 ...

随机推荐

- Python 生成器函数

def func(): print("我叫周润发") return "林志玲" # return在函数中表示返回的意思 ret = func() print(& ...

- IDEA_debug窗口问题,debugger窗口消失,窗口漂浮等

- HDU 6095 17多校5 Rikka with Competition(思维简单题)

Problem Description As we know, Rikka is poor at math. Yuta is worrying about this situation, so he ...

- Spring 消息

RMI.Hessian/Burlap的远程调用机制是同步的.当客户端调用远程方法时,客户端必须等到远程方法完成之后,才能继续执行.即使远程方法不向客户端返回任何消息,客户端也要被阻塞知道服务完成. 消 ...

- jdk安装和环境配置

public class test{ public static void main(String[] args){ System.out.println("hello world" ...

- Android驱动中的remap_pfn_range()校验漏洞(CVE-2013-2596)

简单介绍 当然类似函数还有io_remap_pfn_range(). remap_pfn_range() 为用户态提供了一种手段访问内核地址空间.它通过新页表,将一块内核物理内存映射到用户态进程空间. ...

- [LeetCode&Python] Problem 1: Two Sum

Problem Description: Given an array of integers, return indices of the two numbers such that they ad ...

- 20155219 2016-2017-2 《Java程序设计》第7周学习总结

20155219 2016-2017-2 <Java程序设计>第7周学习总结 教材学习内容总结 认识时间与日期 时间的度量 1.格林威治时间(GMT):通过观察太阳而得,因为地球公转轨道为 ...

- hdoj-4417(做法二 树状数组离线解法,对所有的查询先保存进行排序后有序的查询) 好腻害!

#include<cstdio> #include<cstring> #include<algorithm> using namespace std;; ; str ...

- chmod、chown、umask、lsattr/chattr

1.chmod 命令 改变文件权限 文件对于使用者来说,有 读 .写 .执行 (当然,还有删除),而这里主要说的是,读写执行(rwx) r w x 对应的是 读写执行,也对应 : 4 ...