对FPGA的时钟资源理解(更新中)

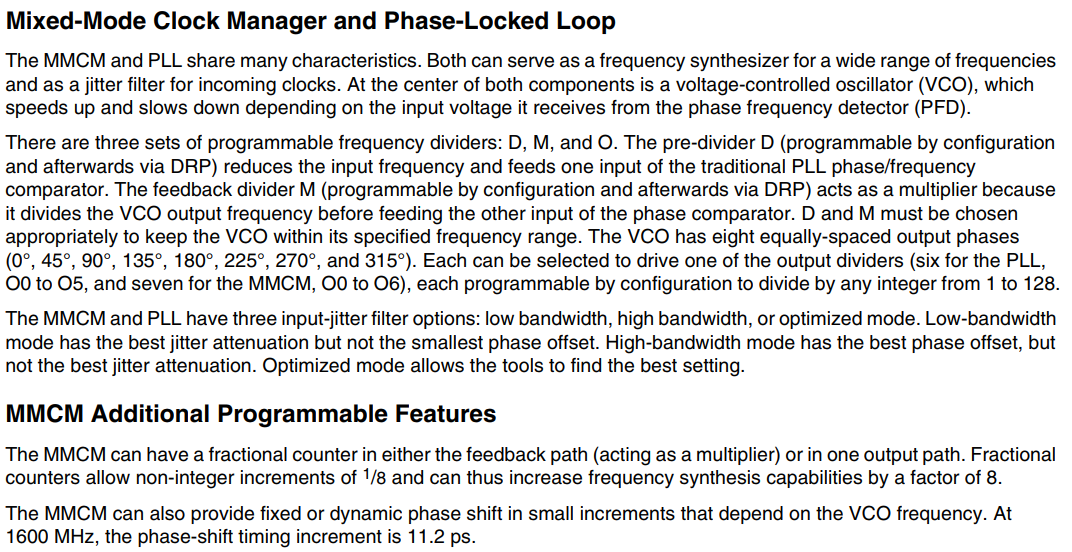

7系列FPGA中包含了多达24个CMT(时钟管理单元)(实际上V7常见只有20个),MMCM和PLL均为时钟综合器,对外部输入时钟、内部时钟进行处理,生成需要的低抖动时钟。PLL是MMCM的功能子集,也是基于MMCM的。其中MMCM包含的额外特性有:

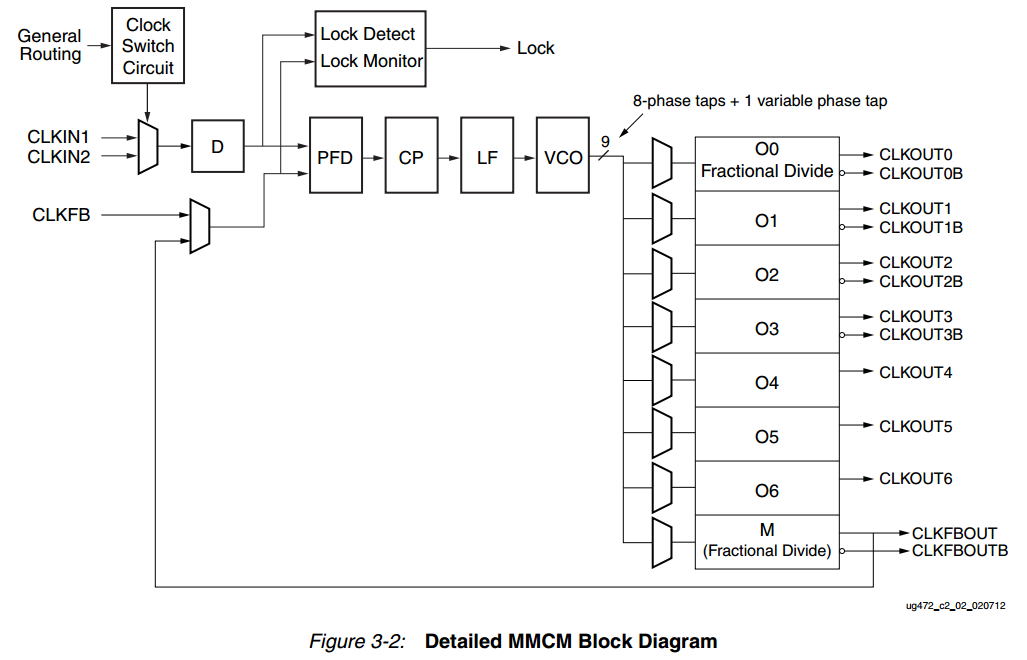

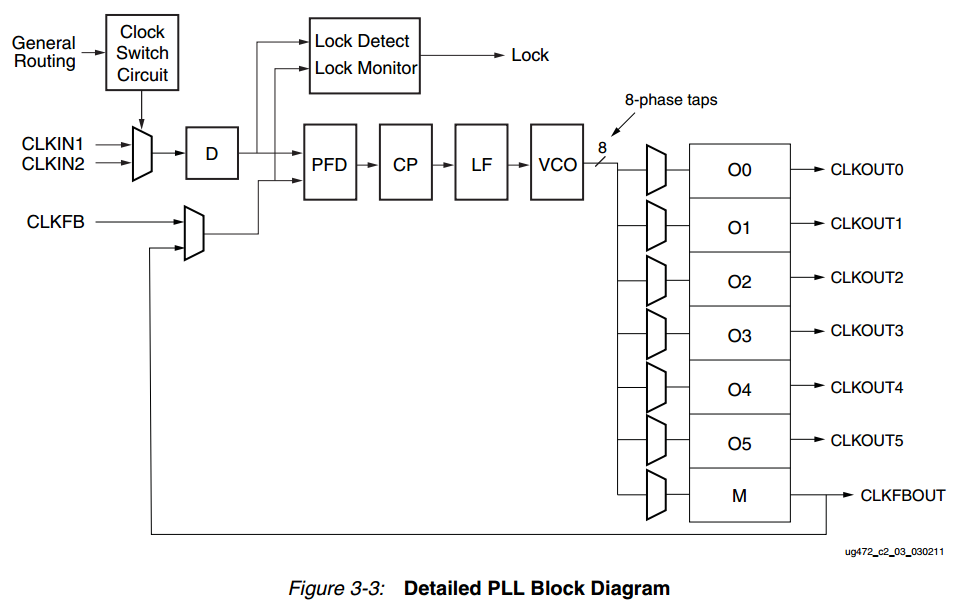

输入多路复用器从IBUFG,BUFG,BUFR,BUFH,GTs(CLKIN only)或互连(不推荐)中选择其一 作为参考和反馈时钟,每个时钟输入都经过一个可编程的计数器(D)。相位频率检测器(PFD)比较输入(参考)时钟和反馈时钟的上升边缘的相位和频率。如果最小的高/低脉冲是可保持的,则任务周期是辅助的。PFD用于生成与两个时钟之间的相位和频率成比例的信号。这个信号用于驱动增压泵(CP)和循环过滤器(LF)来为VCO生成一个参考电压。PFD会产生一个向上或向下的信号给充电泵和环形滤波器,以确定VCO是否应该以更高或更低的频率运行。当VCO以过高的频率运行时,PFD会激活一个向下的信号,导致控制电压降低,降低VCO的工作频率。当VCO以极低的频率运行时,向上的信号会增加电压。VCO生产八个输出阶段和一个可变阶段,用于精细阶段的转换。每个输出阶段都可以被选择作为输出计数器的参考时钟(图3-2和图3-3)。每个计数器可以独立地为给定的客户设计进行编程。还提供了一个特殊的计数器M。这个计数器控制MMCM和PLL的反馈时钟,允许合成宽范围的频率。除了整数除法输出计数器之外,MMCMs还为CLKOUT0和CLKBOUT0添加了一个分数计数器。

source: 可以选择单端输入、差分输入、全局buffer、no buffer四种;

Clock Management

Some of the key highlights of the clock management architecture include:

• High-speed buffers and routing for low-skew clock distribution

• Frequency synthesis and phase shifting

• Low-jitter clock generation and jitter filtering

Each 7 series FPGA has up to 24 clock management tiles (CMTs), each consisting of one mixed-mode clock manager (MMCM) and one phase-locked loop (PLL).

参考:

UG472-7 Series FPGAs Clocking Resources.pdf

DS180-7 Series FPGAs Data Sheet: Overview.pdf

对FPGA的时钟资源理解(更新中)的更多相关文章

- FPGA开发时钟资源评估需要考虑的问题

在第一个独立开发的FPGA项目中,使用了Altera平台的三速以太网IP,工作在100M模式下,外部输入的PHY时钟频率为25MHz. 由于在前期没有注意这个外部输入的时钟,导致最后不得不在板子上飞线 ...

- xilinx FPGA全局时钟资源的使用

1.什么是xilinx fpga全局时钟资源 时钟对于一个系统的作用不言而喻,就像人体的心脏一样,如果系统时钟的抖动.延迟.偏移过大,会导致系统的工作频率降低,严重时甚至会导致系统的时序错乱,实现不了 ...

- 7系列FPGA的时钟资源——UG472

时钟架构总览 7系的FPGA使用了专用的全局(Global)和区域(Regional)IO和时钟资源来管理设计中各种的时钟需求.Clock Management Tiles(CMT)提供了时钟合成(C ...

- C#图书资源【更新中...】喜欢的就转存吧

百度分享暂时取消了,需要的朋友可以直接关注我,我发给你. 重点篇 1.C#与.NET3.5高级程序设计 2.C#与.NET3.5高级程序设计.rar 3.Effective_C#_中文版_改善C#程序 ...

- Xilinx FPGA全局时钟和全局时钟资源的使用方法

对FPGA的全局时钟了解不多,遂转载一篇文档: http://xilinx.eetop.cn/?action-viewnews-itemid-42 目前,大型设计一般推荐使用同步时序电路.同步时序电路 ...

- Spartan6系列之Spartan6系列之芯片时钟资源深入详解

1. 时钟资源概述 时钟设施提供了一系列的低电容.低抖动的互联线,这些互联线非常适合于传输高频信号.最大量减小时钟抖动.这些连线资源可以和DCM.PLL等实现连接. 每一种Spartan-6芯片提 ...

- 三叔学FPGA系列之一:Cyclone V中的时钟资源

之前的项目中更多的是有师兄提供经验和帮助,追求的是快速上手,所以不管对于硬件电路设计,还是verilog电路编程,甚至是FPGA内部的资源,都没来得及系统地学习,最近在做算法到电路的实现,正好系统学习 ...

- FPGA系列之一:Cyclone V中的时钟资源

之前的项目中更多的是有师兄提供经验和帮助,追求的是快速上手,所以不管对于硬件电路设计,还是verilog电路编程,甚至是FPGA内部的资源,都没来得及系统地学习,最近在做算法到电路的实现,正好系统学习 ...

- FPGA异步时钟设计中的同步策略

1 引言 基于FPGA的数字系统设计中大都推荐采用同步时序的设计,也就是单时钟系统.但是实际的工程中,纯粹单时钟系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免. ...

随机推荐

- 数据结构(C语言版)-第1章 绪论

- 【转】 聚类算法-Kmeans算法的简单实现

1. 聚类与分类的区别: 首先要来了解的一个概念就是聚类,简单地说就是把相似的东西分到一组,同 Classification (分类)不同,对于一个 classifier ,通常需要你告诉它“这个东西 ...

- linux下编译C/C++ 程序

C/C++的速度是Python和perl所无法比拟的,尤其对于处理超大的生物信息学文件来说. 最近在写一个最简单的fastq cut工具,Python简直慢到不能忍,8G的fastq.gz文件的cut ...

- every day a practice —— morning(6)

"Nearly one in five job ads for China's 2018 national civil service called for 'men only' or 'm ...

- CentOS优化

一.CentOS6.x优化 #.更改yum源 mv /etc/yum.repos.d/CentOS-Base.repo /etc/yum.repos.d/CentOS-Base.repo.backup ...

- Vmware安装Kali

下载软件 破解版的Vmware14 kali(我的是kali-linux-2018.2-amd64) 配置虚拟机 新建虚拟机,选择自定义 虚拟机硬件兼容性 选择虚拟机硬件兼容性为Workstation ...

- lanmp中环境变量的更改方法

1.vim /etc/profile 改成: export PATH=$PATH:/www/wdlinux/phps/71/bin/ 然后运行: source /etc/profile

- [pat]数素数

时间限制:1000 ms 内存限制 32768 KB 代码长度限制 100 KB 判断程序 Standard (来自 小小) 题目描述 令Pi表示第i个素数.现任给两个正整数M <= N < ...

- 5月21 回话控制SESSION COOKIE

百科 HTTP普及(无状态性) 超文本传输协议(HTTP,HyperText Transfer Protocol)是互联网上应用最为广泛的一种网络协议.所有的WWW文件都必须遵守这个标准.设计HTTP ...

- ATOM常用插件推荐

转载:http://blog.csdn.net/qq_30100043/article/details/53558381 ATOM常用插件推荐 simplified-chinese-menu ATOM ...