对FPGA的时钟资源理解(更新中)

7系列FPGA中包含了多达24个CMT(时钟管理单元)(实际上V7常见只有20个),MMCM和PLL均为时钟综合器,对外部输入时钟、内部时钟进行处理,生成需要的低抖动时钟。PLL是MMCM的功能子集,也是基于MMCM的。其中MMCM包含的额外特性有:

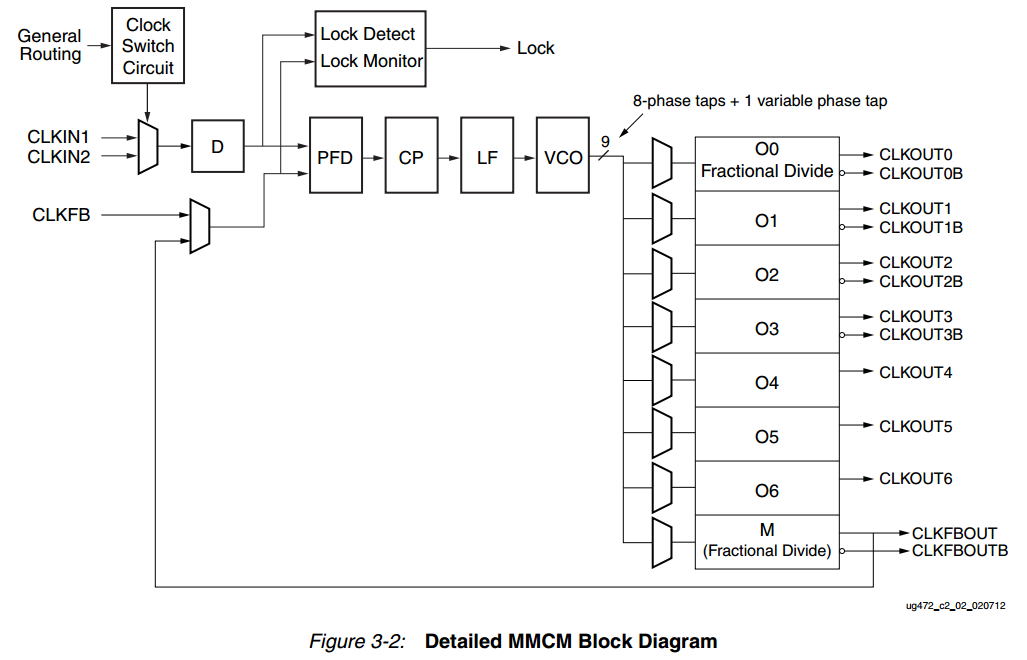

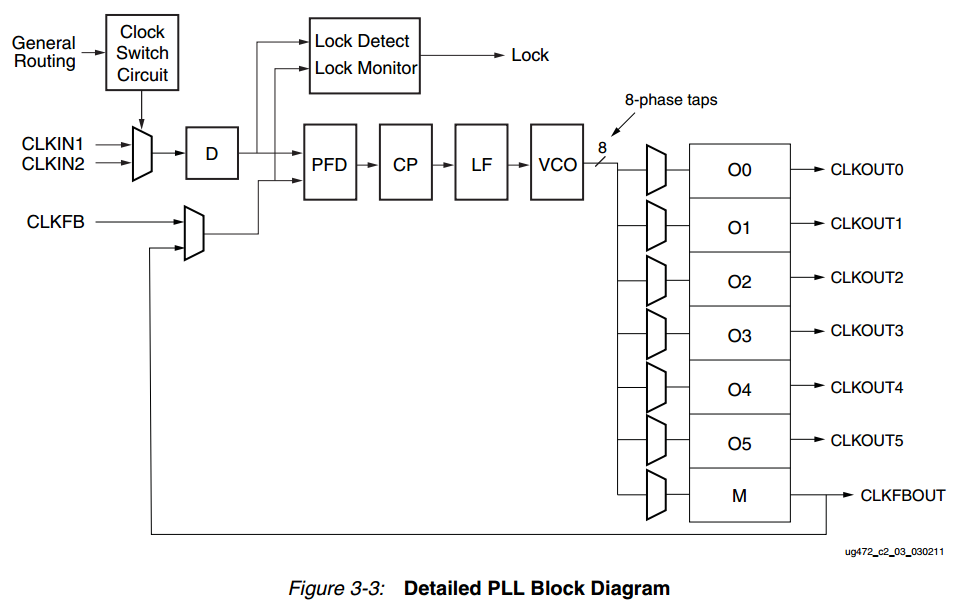

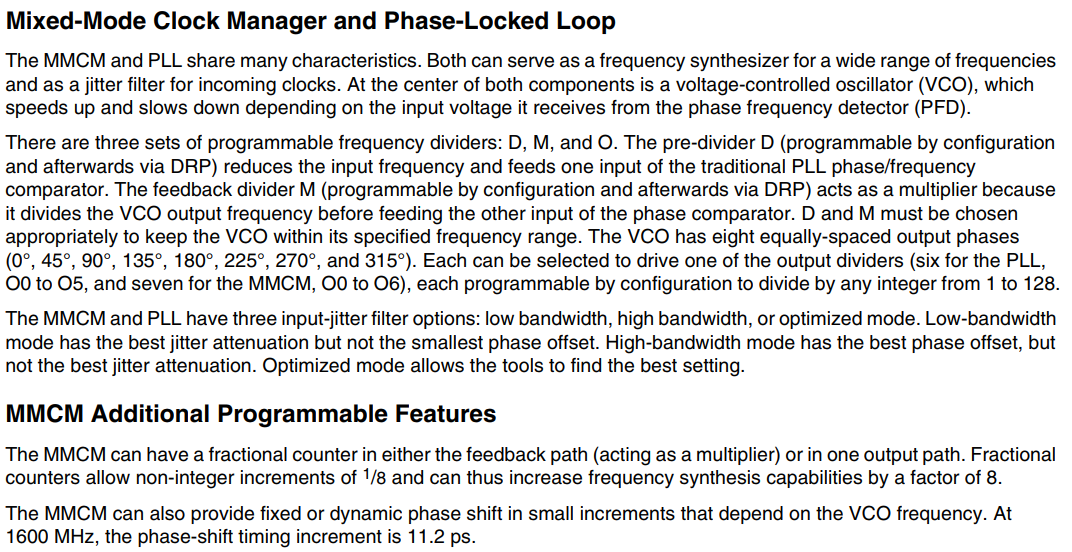

输入多路复用器从IBUFG,BUFG,BUFR,BUFH,GTs(CLKIN only)或互连(不推荐)中选择其一 作为参考和反馈时钟,每个时钟输入都经过一个可编程的计数器(D)。相位频率检测器(PFD)比较输入(参考)时钟和反馈时钟的上升边缘的相位和频率。如果最小的高/低脉冲是可保持的,则任务周期是辅助的。PFD用于生成与两个时钟之间的相位和频率成比例的信号。这个信号用于驱动增压泵(CP)和循环过滤器(LF)来为VCO生成一个参考电压。PFD会产生一个向上或向下的信号给充电泵和环形滤波器,以确定VCO是否应该以更高或更低的频率运行。当VCO以过高的频率运行时,PFD会激活一个向下的信号,导致控制电压降低,降低VCO的工作频率。当VCO以极低的频率运行时,向上的信号会增加电压。VCO生产八个输出阶段和一个可变阶段,用于精细阶段的转换。每个输出阶段都可以被选择作为输出计数器的参考时钟(图3-2和图3-3)。每个计数器可以独立地为给定的客户设计进行编程。还提供了一个特殊的计数器M。这个计数器控制MMCM和PLL的反馈时钟,允许合成宽范围的频率。除了整数除法输出计数器之外,MMCMs还为CLKOUT0和CLKBOUT0添加了一个分数计数器。

source: 可以选择单端输入、差分输入、全局buffer、no buffer四种;

Clock Management

Some of the key highlights of the clock management architecture include:

• High-speed buffers and routing for low-skew clock distribution

• Frequency synthesis and phase shifting

• Low-jitter clock generation and jitter filtering

Each 7 series FPGA has up to 24 clock management tiles (CMTs), each consisting of one mixed-mode clock manager (MMCM) and one phase-locked loop (PLL).

参考:

UG472-7 Series FPGAs Clocking Resources.pdf

DS180-7 Series FPGAs Data Sheet: Overview.pdf

对FPGA的时钟资源理解(更新中)的更多相关文章

- FPGA开发时钟资源评估需要考虑的问题

在第一个独立开发的FPGA项目中,使用了Altera平台的三速以太网IP,工作在100M模式下,外部输入的PHY时钟频率为25MHz. 由于在前期没有注意这个外部输入的时钟,导致最后不得不在板子上飞线 ...

- xilinx FPGA全局时钟资源的使用

1.什么是xilinx fpga全局时钟资源 时钟对于一个系统的作用不言而喻,就像人体的心脏一样,如果系统时钟的抖动.延迟.偏移过大,会导致系统的工作频率降低,严重时甚至会导致系统的时序错乱,实现不了 ...

- 7系列FPGA的时钟资源——UG472

时钟架构总览 7系的FPGA使用了专用的全局(Global)和区域(Regional)IO和时钟资源来管理设计中各种的时钟需求.Clock Management Tiles(CMT)提供了时钟合成(C ...

- C#图书资源【更新中...】喜欢的就转存吧

百度分享暂时取消了,需要的朋友可以直接关注我,我发给你. 重点篇 1.C#与.NET3.5高级程序设计 2.C#与.NET3.5高级程序设计.rar 3.Effective_C#_中文版_改善C#程序 ...

- Xilinx FPGA全局时钟和全局时钟资源的使用方法

对FPGA的全局时钟了解不多,遂转载一篇文档: http://xilinx.eetop.cn/?action-viewnews-itemid-42 目前,大型设计一般推荐使用同步时序电路.同步时序电路 ...

- Spartan6系列之Spartan6系列之芯片时钟资源深入详解

1. 时钟资源概述 时钟设施提供了一系列的低电容.低抖动的互联线,这些互联线非常适合于传输高频信号.最大量减小时钟抖动.这些连线资源可以和DCM.PLL等实现连接. 每一种Spartan-6芯片提 ...

- 三叔学FPGA系列之一:Cyclone V中的时钟资源

之前的项目中更多的是有师兄提供经验和帮助,追求的是快速上手,所以不管对于硬件电路设计,还是verilog电路编程,甚至是FPGA内部的资源,都没来得及系统地学习,最近在做算法到电路的实现,正好系统学习 ...

- FPGA系列之一:Cyclone V中的时钟资源

之前的项目中更多的是有师兄提供经验和帮助,追求的是快速上手,所以不管对于硬件电路设计,还是verilog电路编程,甚至是FPGA内部的资源,都没来得及系统地学习,最近在做算法到电路的实现,正好系统学习 ...

- FPGA异步时钟设计中的同步策略

1 引言 基于FPGA的数字系统设计中大都推荐采用同步时序的设计,也就是单时钟系统.但是实际的工程中,纯粹单时钟系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免. ...

随机推荐

- 数据结构(C语言版)-第6章 图

6.1 图的定义和基本术语 图:Graph=(V,E) V:顶点(数据元素)的有穷非空集合: E:边的有穷集合. 无向图:每条边都是无方向的 有向图:每条边都是有方向的 完全图:任意两个点都有一条 ...

- C语言流控制命令的总结

C语言流控制命令的总结 基本概念: C语言中,自顶向下的的代码的流程叫做程序流. 能够改变程序流顺序的语句叫做流控制命令. 我为什么要写这篇文章 在学习C语言的过程中,经常会用到条件语句和循环语句这些 ...

- 皮尔逊残差 | Pearson residual

参考:Pearson Residuals 这些概念到底是写什么?怎么产生的? 统计学功力太弱了!

- Shell脚本管理

sh test.sh../test.sh与source test.sh.. test.sh执行命令的区别:sh是启用子shell执行而source或点是在当前窗口执行export A=123:定义全局 ...

- How-to: Use HBase Bulk Loading, and Why

How-to: Use HBase Bulk Loading, and Why http://blog.cloudera.com/blog/2013/09/how-to-use-hbase-bulk- ...

- 2.1 uml序言

UML Unified Modeling Language 统一建模语言 模型的定义 建模 modeling 重要的研发成果常常产自类比(analogy): 把不太理解的东西和一些已经较为理解.且十分 ...

- python-前20天的着重知识点

1.CPU存在两种工作状态:一种是内核态,操作系统在运行--可以操作硬件: 另一种是用户态,是应用软件在运行--不可以操作硬件. 应用软件要控制硬件,就要从用户态切换成内核态 2.多道技术:(多道指的 ...

- Oracle11g温习-第十六章:用户管理

2013年4月27日 星期六 10:50 1.概念 (1)schema : user.object 就是用户创建的对象 (2)用户认证方式: ...

- WDA基础五:ALV组件的使用

说明,因为ALV的功能比TABLE强大,所以在很多时候都习惯性的选择ALV显示. ALV是WDA的组件,封装好的,和SELECT OPTION一样.所以使用的方法一般就是:引入组件,初始化组件,数据绑 ...

- 集成学习二: Boosting

目录 集成学习二: Boosting 引言 Adaboost Adaboost 算法 前向分步算法 前向分步算法 Boosting Tree 回归树 提升回归树 Gradient Boosting 参 ...