ADC采样信号RMS测量值的Verilog实现

术语“RMS”代表“Root-Mean-Squared”。大多数书籍将此定义为“产生与等效直流电源相同的加热效果的交流电量”,或者沿着这些线路类似的东西,但RMS值不仅仅是这个。 RMS值是瞬时值的平方函数的平均值(平均值)的平方根。

笔者的印象中第一次接触到交流电是初中,具体是初二还是初三就不太清楚了。交流电动势的表达式为e=E(m)sinωt,其中E(m)为交流电动势的最大值,那么交流电动势的有效值为 E=E(m)/√2

同理得交流电压的有效值和交流电流的有效值分别为:

U = U(m)/√2

I = I(m)/√2

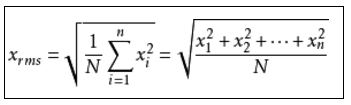

以上的方法是以前中学课本里头理想情况下计算正弦余弦的有效值方法。而在实际的ADC采样中,采集到的信号可能并不是标准的正弦余弦信号,甚至可能是些杂乱的噪声信号。根据有效值的基本定义:周期量在一个周期内的均方根值。可以用以下的公式表示:

根据该公式可以把ADC采集到的信号直接用代码计算出来

1 //**************************************************************************

2 // *** file name : RMS_measure.v

3 // *** version : 1.0

4 // *** Description : ADC RMS measure

5 // *** Blogs : https://www.cnblogs.com/WenGalois123/

6 // *** Author : Galois_V

7 // *** Date : 2022.10.26

8 // *** Changes : Initial

9 //**************************************************************************

10 `timescale 1ns/1ps

11 module RMS_measure

12 #(

13 parameter DWIDTH = 18

14 )

15 (

16 input i_sys_clk ,

17 input i_sys_rstn ,

18 input [DWIDTH-1:0] i_adc_data ,

19 input i_adc_valid ,

20 input i_measure_enable ,

21 output reg [31:0] o_adc_data_cnt ,

22 output reg [63:0] o_adc_square_sum ,

23 output reg [47:0] o_adc_sum ,

24 output reg o_adc_sum_valid

25 );

26 wire [DWIDTH+1:0] w_adc_data ;

27 wire [2*(DWIDTH+1)+1:0] w_mult_data ;

28 wire w_adc_add_en ;

29 wire w_adc_notend ;

30 wire w_square_overflow ;

31

32 reg signed [DWIDTH+1:0] r_adc_data ;

33 reg signed [2*(DWIDTH+1)+1:0] r_mult_data ;

34 reg [5:0] r_adc_end_detection ;

35

36 assign w_adc_data = (i_adc_valid & i_measure_enable) ? {{2{i_adc_data[DWIDTH-1]}},i_adc_data} : 'd0;

37 assign w_square_overflow = &o_adc_square_sum[63:54];

38 assign w_adc_notend = i_measure_enable && w_square_overflow;

39 assign w_adc_add_en = i_adc_valid && w_adc_notend;

40 /******************************************************************************\

41 Calculate sum of squares

42 \******************************************************************************/

43 always@(posedge i_sys_clk)

44 begin

45 if(~i_sys_rstn)

46 begin

47 r_adc_data <= 'd0;

48 r_mult_data <= 'd0;

49 end

50 else

51 begin

52 r_adc_data <= w_adc_data;

53 r_mult_data <= r_adc_data * r_adc_data;

54 end

55 end

56

57 assign w_mult_data = r_mult_data;

58

59 always@(posedge i_sys_clk)

60 begin

61 if(~i_sys_rstn)

62 begin

63 o_adc_square_sum <= 'd0;

64 end

65 else

66 begin

67 o_adc_square_sum <= o_adc_square_sum + w_mult_data;

68 end

69 end

70 /******************************************************************************\

71 Count ADC points

72 \******************************************************************************/

73 always@(posedge i_sys_clk)

74 begin

75 if(~i_sys_rstn)

76 begin

77 o_adc_data_cnt <= 'd0;

78 end

79 else if(w_adc_add_en)

80 begin

81 o_adc_data_cnt <= o_adc_data_cnt + 1'b1;

82 end

83 end

84 /******************************************************************************\

85 Statistical ADC accumulation sum

86 \******************************************************************************/

87 always@(posedge i_sys_clk)

88 begin

89 if(~i_sys_rstn)

90 begin

91 o_adc_sum <= 'd0;

92 end

93 else if(w_adc_add_en)

94 begin

95 o_adc_sum <= o_adc_sum + {{(47-DWIDTH-1){w_adc_data[DWIDTH+1]}},w_adc_data};

96 end

97 end

98 /******************************************************************************\

99 Output the effective signal of the result to ensure the stability of the result

100 \******************************************************************************/

101 always@(posedge i_sys_clk)

102 begin

103 if(~i_sys_rstn)

104 begin

105 r_adc_end_detection <= 'd0;

106 end

107 else

108 begin

109 r_adc_end_detection <= {r_adc_end_detection[4:0],w_adc_notend};

110 end

111 end

112

113 always@(posedge i_sys_clk)

114 begin

115 if(~i_sys_rstn)

116 begin

117 o_adc_sum_valid <= 'd0;

118 end

119 else if(~r_adc_end_detection[4] && r_adc_end_detection[5])

120 begin

121 o_adc_sum_valid <= 1'b1;

122 end

123 else

124 begin

125 o_adc_sum_valid <= 'd0;

126 end

127 end

128

129 endmodule

以上代码分别算出有效时间内(i_measure_enable为时间阈值设置信号)ADC信号的点数,平方和以及ADC的累加值。计算出的这些值可以通过axi4_lite总线的传给soc,对数据根据公式进行浮点型计算得出信号的平均值,有效值。

ADC采样信号RMS测量值的Verilog实现的更多相关文章

- STM32中基于DMA的ADC采样实例之MQ-2烟雾传感器

最近学习了一下STM32中的ADC采样,由于手头正好有一个MQ-2的烟雾传感器,所以正好可以测试一把.体验ADC采样的过程.下面介绍一下这个MQ-2烟雾传感器. 1.MQ-2烟雾传感器简介 MQ-2气 ...

- 使用STM8SF103 ADC采样电压(转)

源:使用STM8SF103 ADC采样电压 硬件环境: STM8SF103 TSSOP20封装 因为项目需要用到AD采样电池电压,于是便开始了使用STM8S ADC进行采样,也就有了下文. 手册上对S ...

- ADC采样对MIC的干扰

使用EFM8SB的MCU做ADC采样,检测MIC Bias的电源,解码android耳机的线控.初始时, ADC的采样频率2KHz, 在录音时后播放,能固定的听到接近2K的一个噪声.示波器探测不到明显 ...

- 【转载】使用STM8SF103 ADC采样电压

源:使用STM8SF103 ADC采样电压 硬件环境: STM8SF103 TSSOP20封装 因为项目需要用到AD采样电池电压,于是便开始了使用STM8S ADC进行采样,也就有了下文. 手册上对S ...

- STM32 多通道ADC采样,采用Timer1进行采样率控制,利用DMA进行传输

http://blog.csdn.net/varding/article/details/17559399 http://www.51hei.com/stm32/3842.html https://w ...

- DSP基础学习-ADC采样

DSP基础学习-ADC采样 彭会锋 2015-04-27 22:30:03 在查看ADC采样例程的时候我发现了下面的代码挺有意思的 EALLOW; GpioCtrlRegs.GPAMUX2.bit.G ...

- 利用基准电压效正Vcc做参考电压的ADC采样计算方法

利用基准电压效正Vcc做参考电压的ADC采样计算方法

- STM32的ADC采样时间

STM32的ADC采样时间与其ADC的时钟频率密不可分. 例:STM32F103系列的ADC的时钟是在APB2(最大72MHZ)上.我们可以对其分频: RCC_PCLK2_Div2: ADC cloc ...

- 定时器同步+触发三ADC采样+输出6路PWM波

为了熟悉定时器定时器和ADC 用STM32F407DIS做了一个简单的工程: 通过高级定时器TIM1溢出更新时间作为触发输出信号(TRGO),触发TIM8开始计数: 同时TIM1的通道1.2.3以及分 ...

- [ADC]TI am4378 ADC采样设置问题(am335x类似)

这段时间在调试AM4378的ADC问题,发现采样到的数据和真实输入波形有所出入,比如输入是1ms的周期,50%占空比的信号,但是采样的数据描点总是偏差较大,数据如下 iio device number ...

随机推荐

- JavaScript 如何验证 URL

前言 当开发者需要为不同目的以不同形式处理URL时,比如说浏览器历史导航,锚点目标,查询参数等等,我们经常会借助于JavaScript.然而,它的频繁使用促使攻击者利用其漏洞.这种被利用的风险是我们必 ...

- 【ACR2015】依那西普按需维持治疗策略有效抑制RA骨破坏进展

标签: 类风湿关节炎; 依那西普; 药物减停; 复发重治 对RA疾病复发患者, 依那西普按需治疗与持续足剂量治疗是否存在疗效差异? Inui K, et al. ACR 2015. Presentat ...

- Kotlin学习-基础知识点

一:基础要点 //常量定义 valval arg_a1: Int = 1 //变量定义varvar arg_a2 = 5 // 系统自动推断变量类型为Int备注:kotlin 定义变量必须给定初始 ...

- TP-Link路由器后台密码爆破

title: TP-Link路由器后台密码爆破 author: 杨晓东 permalink: TP-Link路由器后台密码爆破 date: 2021-10-02 11:27:04 categories ...

- 使用伪元素 before 叹号

.tip { width: 400px; line-height: 150%; border-left-color: #f66; color: #666; padding: 12px 24px 12p ...

- zabbix-agent2安装问题汇总

1.yum源报错 # 具体报错信息 failure: repodata/4bb73bd0742c638c3cd1e73a5f3dc8838c7b0d693c9f50b7ed8266c3e83308d3 ...

- '大龄‘后端程序员,快速捡起ECMAScript6

1.Promise 2.迭代器 3.async 4.module 5. this的理解

- 解决windows下使用vscode没有函数提示的问题

vscode支持非常多的扩展,包括支持protobuf语法,非常方便. 笔者近期在使用vscode打开工程(文件夹)情况下,困扰于没有函数提示,例如不同路径的头文件中的函数不提示,库函数不提示,试尽各 ...

- python虚拟环境解决不能执行脚本的问题

1 安装虚拟环境 pip install virtualenv 2 创建虚拟文件夹 mkdir .venvs 3.设置虚拟目录 virtualenv --system-site-packages .v ...

- 四大组件之广播接收者BroadcastReceiver

参考:Android开发基础之广播接收者BroadcastReceiver 什么是广播接收者? 我们小时候都知道,听广播,收听广播!什么是收听广播呢?打开收音机,调频就可以收到对应的广播节目了.其实我 ...