S02_CH01_Hello World实验

S02_CH01_Hello World实验

ZYNQ是一款SOC芯片,在前面第一季的学习当中,我们只是粗略的学习了ZYNQ的PL部分,对于ZYNQ最突出的功能,其内部的双核Cortex-A9内核并未使用到。从本章开始,我们就将开始学习ZYNQ的SOC学习。

本章将带领大家搭建一个最小系统,在此基础上,对我们的板子上的一些硬件进行测试,通过本章,你将掌握如何创建一个SOC工程与SDK软件的基本使用。

1.1最小系统分析

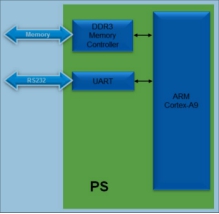

这张图展示了我们需要构建的最小系统。并且下面的嵌入式实验会基于这个最小系统进行添加外设。

本实验中将会只使用到PS 部分资源包括了ARM Cortex-A9、DDR3内存、一个UART串口。这就是我们的最小系统。首先我们程序会加载到DDR内存中,然后CPU一条一条执行,那么执行的情况我们可以通过串口打印观察。

1.2 硬件电路分析

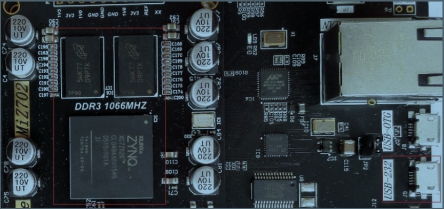

红色线框内就是本次实验需要用到的资源,分别为CPU XC7Z020、2 片512MB 内存、一个Micro 接口的USB 转UART。

1.3创建一个VIVADO工程

Step1:在打开的VIVADO软件界面,单击Create New Project。

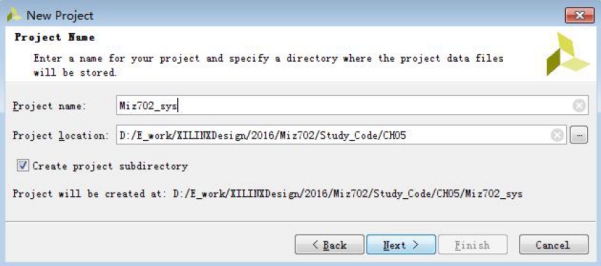

Step2:单击NEXT,在弹出的窗口中输入工程名和选择保存路径,然后单击Next。

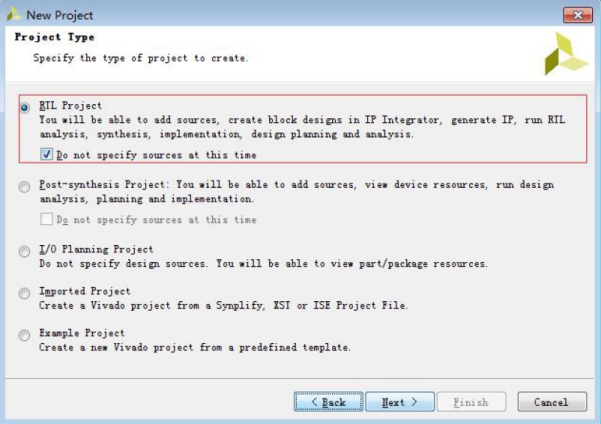

Step3:

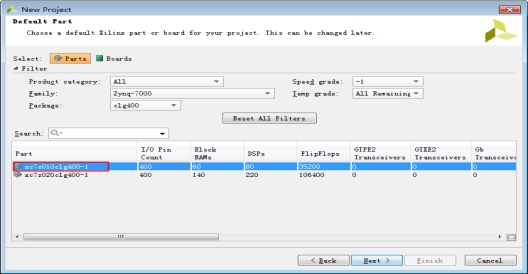

Step4:选择芯片类型。(请大家根据自己实际的类型选择)

Miz702与Miz702N用户如下设置:

Miz701N与Miz701用户如下设置:

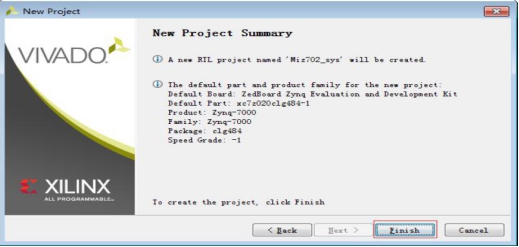

Step5:

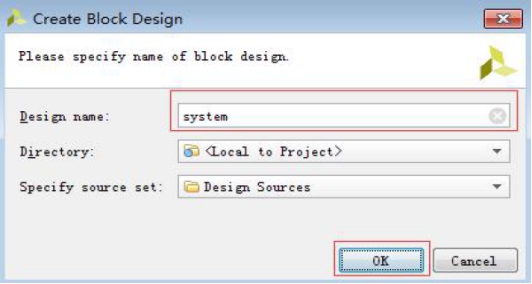

Step6:单击Create Block Design,输入System。

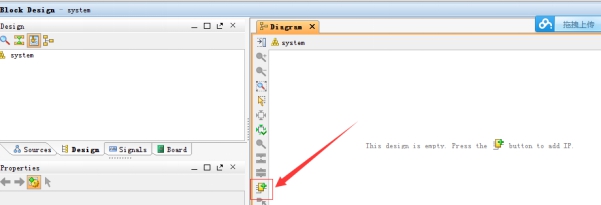

Step7: 单击下图中 添加IP按钮

添加IP按钮

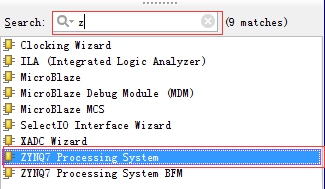

Step8:搜素单词z选择ZYNQ7 Processing System,然后双击

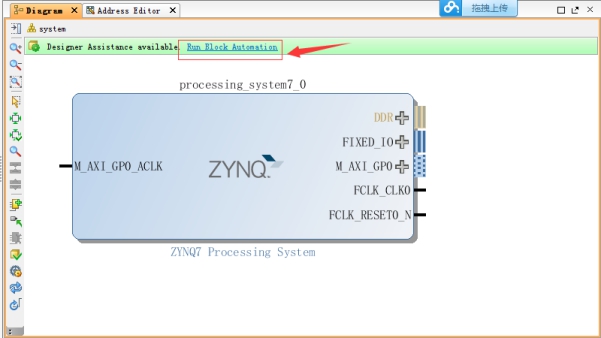

Step9:添加进来了ZYNQ CPU IP,然后单击Run Block Automation ,直接单击OK。

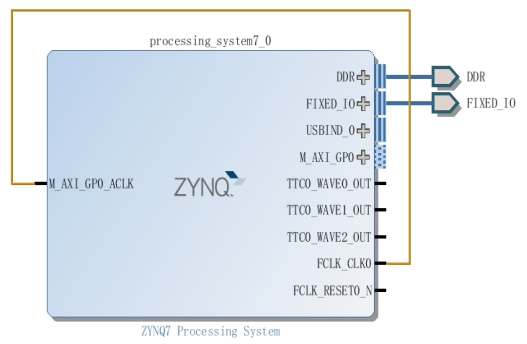

Step10:在Block文件中,我们进行连线,将鼠标放在引脚处,鼠标变成铅笔后迚行拖拽,连线如下图所示。连线的作用就是把PS的时钟可以接入PL部分,当然这里我们暂时用不到PL部分的资源。

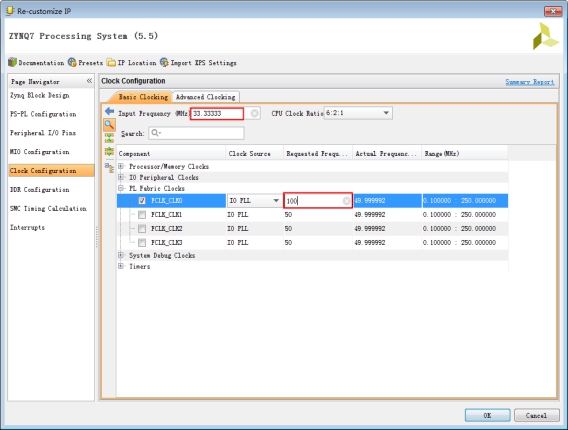

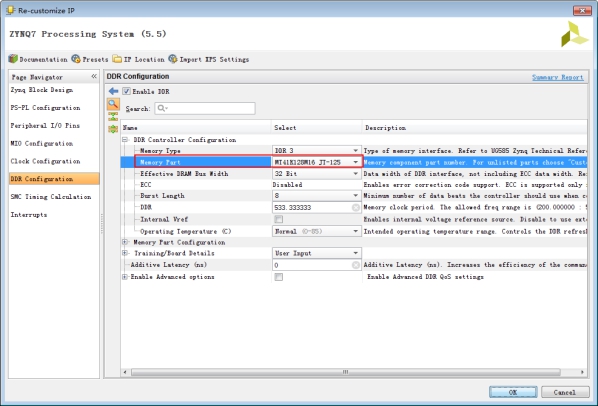

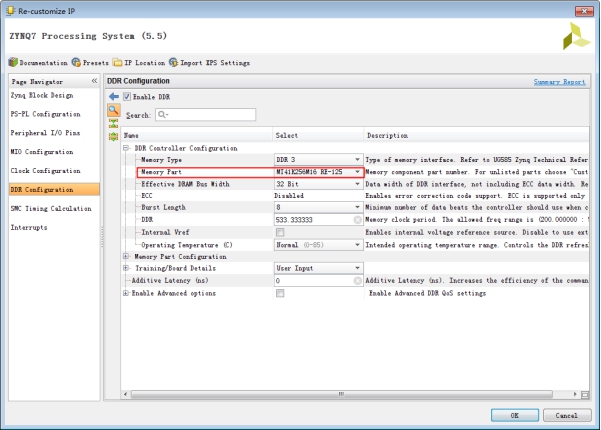

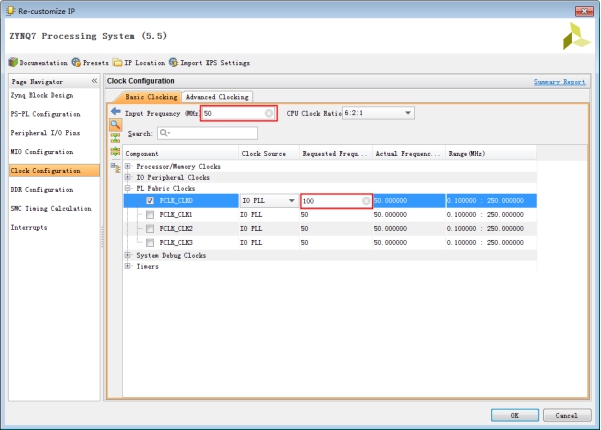

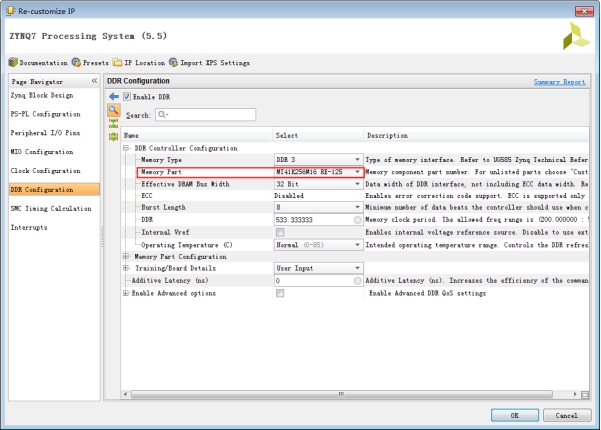

Step11:双击ZYNQ CPU IP,对其进行设置,使其对应我们的硬件设置。在此部分,我们需要做的就是修改时钟频率,内存类型和接口输出。需要注意的是,如果时钟频率与内存类型与我们的硬件不一致时,SDK中的程序会崩溃,运行不过来。这在后续的调试中,是一个小技巧。正确的配置是成功的必要条件。

Miz702时钟及内存型号配置如下:

Miz702N时钟及内存型号配置如下:

Miz701与Miz701N时钟及内存型号配置如下:

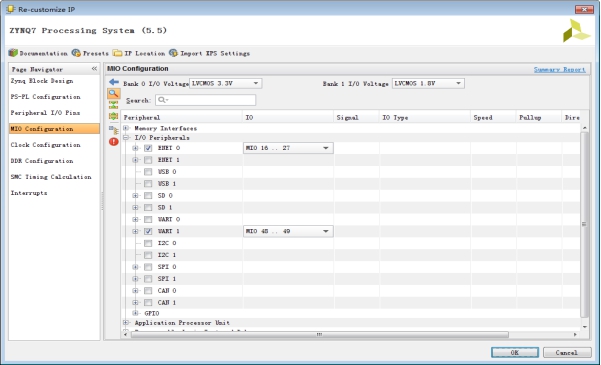

Step12:设置外扩接口,之后点击OK。

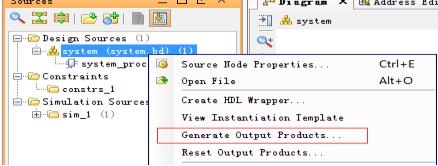

Step13:右击 system.bd, 单击Generate Output Products。

Step14:支部操作会产生执行、仿真、综合的文件,可以看出来最后的硬件设计步骤还是回到了我们前面的FPGA开发上来了。

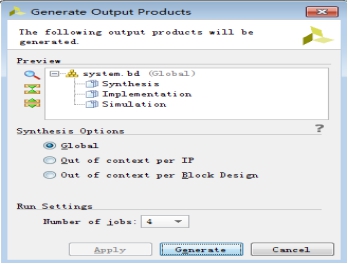

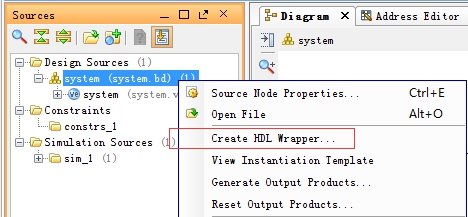

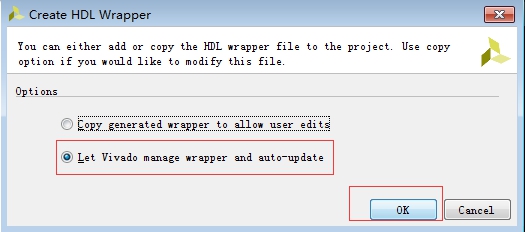

Step15:右击system.bd 选择 Create HDL Wrapper 这步的作用是产生顶层的HDL文件

Step16:选择Leave Let Vivado manager wrapper and auto-update 然后单击OK

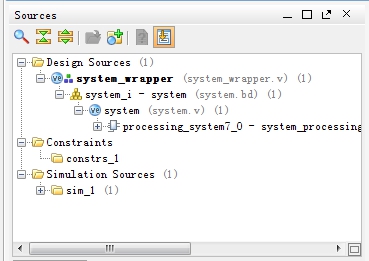

Step17:之后我看下源码的层次结构,可以看到system_wrapper.v就是顶层文件,调用了CPU.

Step18:查看system_wrapper.v源码

|

//Copyright 1986-2015 Xilinx, Inc. All Rights Reserved. //-------------------------------------------------------------------------------- //Tool Version: Vivado v.2015.4 (win64) Build 1412921 Wed Nov 18 09:43:45 MST 2015 //Date : Thu Mar 24 22:07:47 2016 //Host : PC201603040001 running 64-bit Service Pack 1 (build 7601) //Command : generate_target system_wrapper.bd //Design : system_wrapper //Purpose : IP block netlist //-------------------------------------------------------------------------------- `timescale 1 ps / 1 ps module system_wrapper (DDR_addr, DDR_ba, DDR_cas_n, DDR_ck_n, DDR_ck_p, DDR_cke, DDR_cs_n, DDR_dm, DDR_dq, DDR_dqs_n, DDR_dqs_p, DDR_odt, DDR_ras_n, DDR_reset_n, DDR_we_n, FIXED_IO_ddr_vrn, FIXED_IO_ddr_vrp, FIXED_IO_mio, FIXED_IO_ps_clk, FIXED_IO_ps_porb, FIXED_IO_ps_srstb); inout [14:0]DDR_addr; inout [2:0]DDR_ba; inout DDR_cas_n; inout DDR_ck_n; inout DDR_ck_p; inout DDR_cke; inout DDR_cs_n; inout [3:0]DDR_dm; inout [31:0]DDR_dq; inout [3:0]DDR_dqs_n; inout [3:0]DDR_dqs_p; inout DDR_odt; inout DDR_ras_n; inout DDR_reset_n; inout DDR_we_n; inout FIXED_IO_ddr_vrn; inout FIXED_IO_ddr_vrp; inout [53:0]FIXED_IO_mio; inout FIXED_IO_ps_clk; inout FIXED_IO_ps_porb; inout FIXED_IO_ps_srstb; wire [14:0]DDR_addr; wire [2:0]DDR_ba; wire DDR_cas_n; wire DDR_ck_n; wire DDR_ck_p; wire DDR_cke; wire DDR_cs_n; wire [3:0]DDR_dm; wire [31:0]DDR_dq; wire [3:0]DDR_dqs_n; wire [3:0]DDR_dqs_p; wire DDR_odt; wire DDR_ras_n; wire DDR_reset_n; wire DDR_we_n; wire FIXED_IO_ddr_vrn; wire FIXED_IO_ddr_vrp; wire [53:0]FIXED_IO_mio; wire FIXED_IO_ps_clk; wire FIXED_IO_ps_porb; wire FIXED_IO_ps_srstb; system system_i (.DDR_addr(DDR_addr), .DDR_ba(DDR_ba), .DDR_cas_n(DDR_cas_n), .DDR_ck_n(DDR_ck_n), .DDR_ck_p(DDR_ck_p), .DDR_cke(DDR_cke), .DDR_cs_n(DDR_cs_n), .DDR_dm(DDR_dm), .DDR_dq(DDR_dq), .DDR_dqs_n(DDR_dqs_n), .DDR_dqs_p(DDR_dqs_p), .DDR_odt(DDR_odt), .DDR_ras_n(DDR_ras_n), .DDR_reset_n(DDR_reset_n), .DDR_we_n(DDR_we_n), .FIXED_IO_ddr_vrn(FIXED_IO_ddr_vrn), .FIXED_IO_ddr_vrp(FIXED_IO_ddr_vrp), .FIXED_IO_mio(FIXED_IO_mio), .FIXED_IO_ps_clk(FIXED_IO_ps_clk), .FIXED_IO_ps_porb(FIXED_IO_ps_porb), .FIXED_IO_ps_srstb(FIXED_IO_ps_srstb)); endmodule |

可以看到顶层文件的源码调用了CPU接口,所有外设的接口也都是通过顶层文件引出来的。

Step19:执行->产生bit文件。

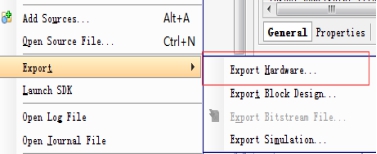

1.4 导出SOC硬件到SDK

Step1: File->Export->Export Hardware

Step2:勾选Include bitstream 直接单击OK

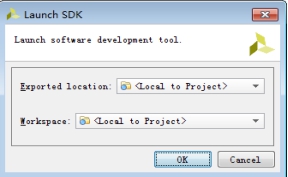

Step3:File->Launch SDK加载到SDK

Step4:单击OK

1.5 Hello World实验

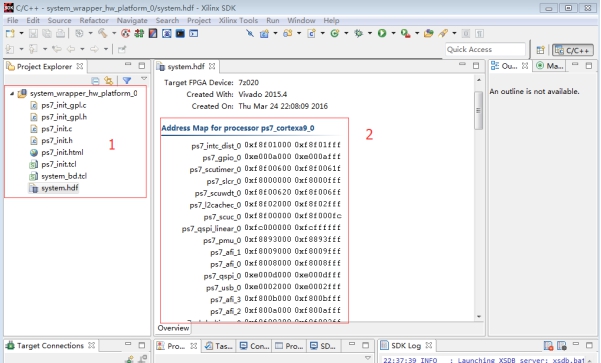

Step1:导出完成后如下图

1、硬件部分,这部分就是从VIVADO定制好的SOC硬件

2、这部分是硬件的地址空间分配

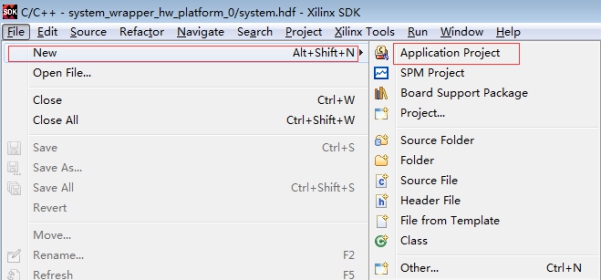

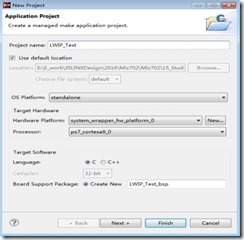

Step2:选择File->New->Application Project

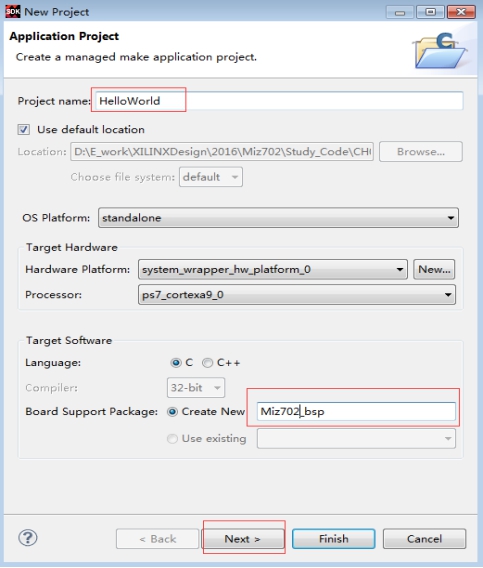

Step3:工程命名为HelloWorld,创建的bsp包取名为Miz702_bsp,然后单击NEXT

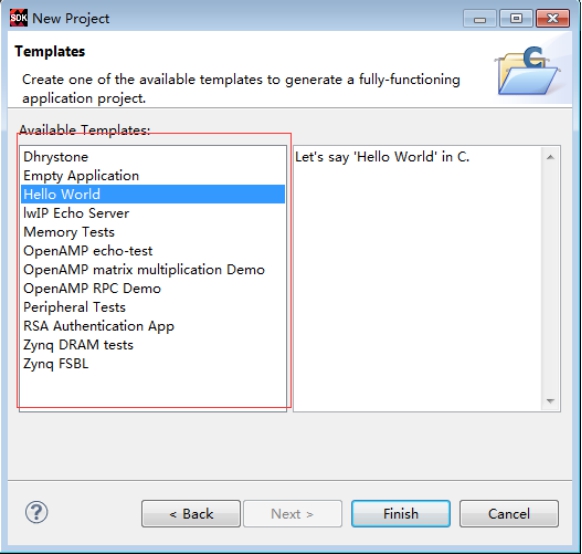

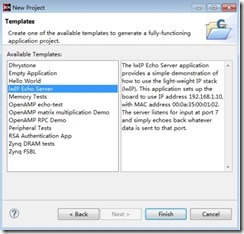

Step4:系统里面有很多自带的测试程序,本次就用自带的Helloworld程序做测试,单击Finish

Step5:完成后

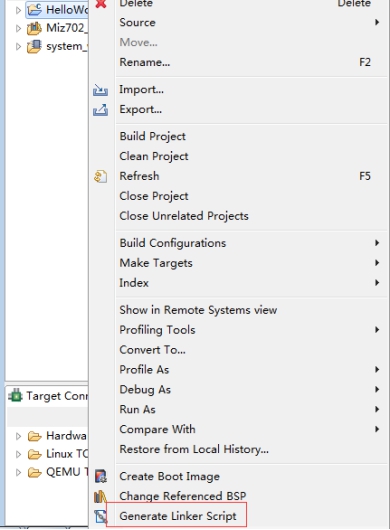

Step6:右击HelloWorld->Generate linker Script

Step7:可以看到所有可用内存的情况,代码、数据、堆栈运行所在内存的情况。不做人为改动,关闭。

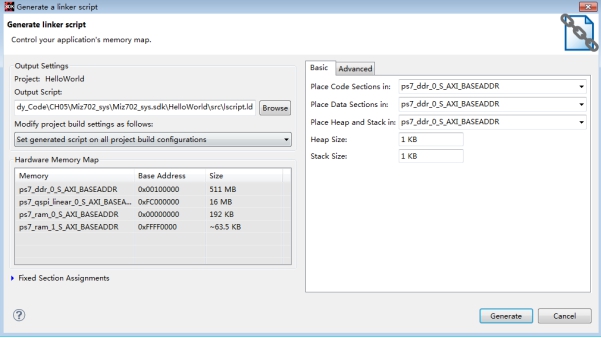

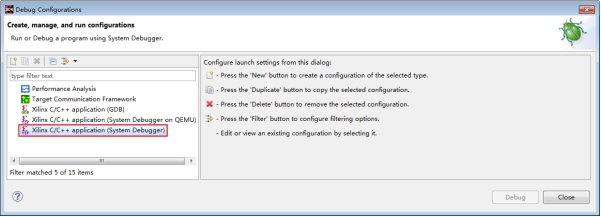

Step8:右击HelloWorld->

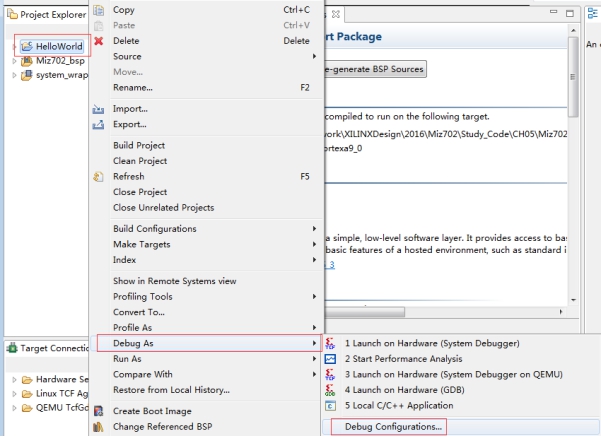

Step9:双击这个位置新建

Step10:然后进行如下设置

Step11:进入SDK调试界面

1、启动2、暂停3、停止4、代码5、信息控制台6、调试变量

Step12:启用系统自带的串口调试助手,进行相关的设置。

Step13:单击运行输出结果

1.6 MemTest内存测试程序

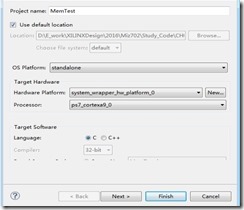

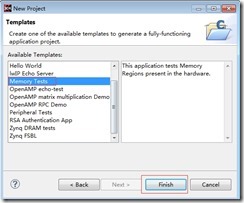

Step1:新建一个名为MemTest的工程

Step2:任然采用自带的测试函数测试

Step3:测试结果

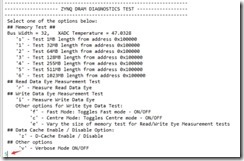

1.7 DRAMTest内存测试程序

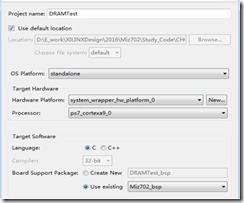

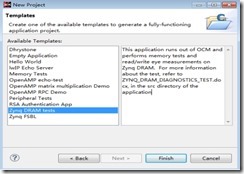

Step1:新建一个名为MemTest的工程

Step3:新建一个名为MemTest的工程

Step4:测试结果

根据提示可以在控制台中输入相关序号按回车进行(r,i测试会有一部分错误,还以和程序空间有关系)

1.8 LWIP协议对千兆网口测试

Step1:新建一个名为LWIP_Test的工程

Step2:选择LWIP Echo Server 之后单击Finish

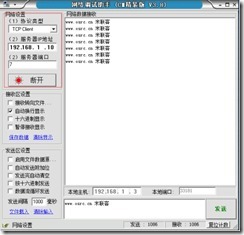

Step3:运行之后的串口打印信息

Step4:用网络助手实现回传测试

1.9使用快捷按钮调试

使用这两个图标,一个是debug一个是运行模式可以方便调试。

1.10 本章小结

本章详细讲解了定制一个SOC最小系统,并且运行了自带的HelloWorld工程、MemTest内存测试工程、DRAMTest内存测试工程、LWIP网络协议工程对千兆网口测试。本章让初学者可以搭建一个最小的SOC系统,并且教会读者利用软件自动的工程对SOC的基本外设进行测试。希望大家多多操作,熟练掌握如何创建VIVADO工程,懂得如何根据自己的硬件平台配置ZYNQ CPU IP,下章我们将不在对这些进行详细的讲解。

工程配套源码:

【MIZ701N-7010】:http://pan.baidu.com/s/1o8fklYU 密码:z6ve

【MIZ701N-7020】:http://pan.baidu.com/s/1sl6Ox45 密码:t1fs

【MIZ702-7020 】:http://pan.baidu.com/s/1i51FaAD 密码:epy4

【MIZ702N-7020】:http://pan.baidu.com/s/1nvsdzZV 密码:1beo

S02_CH01_Hello World实验的更多相关文章

- [原] 利用 OVS 建立 VxLAN 虚拟网络实验

OVS 配置 VxLAN HOST A ------------------------------------------ | zh-veth0(10.1.1.1) VM A | | ---|--- ...

- Android中Activity的四大启动模式实验简述

作为Android四大组件之一,Activity可以说是最基本也是最常见的组件,它提供了一个显示界面,从而实现与用户的交互,作为初学者,必须熟练掌握.今天我们就来通过实验演示,来帮助大家理解Activ ...

- SEED实验系列文章目录

美国雪城大学SEEDLabs实验列表 SEEDLabs是一套完整的信息安全实验,涵盖本科信息安全教学中的大部分基本原理.项目组2002年由杜文亮教授创建,目前开发了30个实验,几百所大学已采用.实验楼 ...

- 物联网实验4 alljoyn物联网实验之手机局域网控制设备

AllJoyn开源物联网协议框架,官方描述是一个能够使连接设备之间进行互操作的通用软件框架和系统服务核心集,也是一个跨制造商来创建动态近端网络的软件应用.高通已经将该项目捐赠给了一个名为“AllSee ...

- (转)linux下和云端通讯的例程, ubuntu和openwrt实验成功(一)

一. HTTP请求的数据流总结#上传数据, yeelink的数据流如下POST /v1.0/device/4420/sensor/9089/datapoints HTTP/1.1Host: api. ...

- (原创) alljoyn物联网实验之手机局域网控制设备

AllJoyn开源物联网协议框架,官方描述是一个能够使连接设备之间进行互操作的通用软件框架和系统服务核心集,也是一个跨制造商来创建动态近端网络的软件应用.高通已经将该项目捐赠给了一个名为“AllSee ...

- 实验:Oracle直接拷贝物理存储文件迁移

实验目的:Oracle直接拷贝物理文件迁移,生产库有类似施工需求,故在实验环境简单验证一下. 实验环境: A主机:192.168.1.200 Solaris10 + Oracle 11.2.0.1 B ...

- Oracle RAC 更换存储实验

实验环境准备: RHEL 6.5 + Oracle 11.2.0.4 RAC (2nodes) OCR和Voting Disk使用的是OCR1磁盘组,底层对应3个1G大小的共享LUN,一般冗余: DA ...

- Vertica集群扩容实验过程记录

需求: 将3个节点的Vertica集群扩容,额外增加3个节点,即扩展到6个节点的Vertica集群. 实验环境: RHEL 6.5 + Vertica 7.2.2-2 步骤: 1.三节点Vertica ...

随机推荐

- 一、docker安装CentOS7

一.安装步骤 前提条件 Docker运行在CentOS7上,要求系统64位.系统内核版本为3.10以上. Docker是一个进程,一启动就两个进程,一个服务,一个守护进程.占用资源就非常少,启动速度非 ...

- ie中打印的问题

一般正常的情况下使用window.print();各个浏览器都可以调用出打印功能来但是ie有个坑就是如果页面在iframe里的话打印出来就是错的页面所以在这里要这样写: var agent = nav ...

- 数据库隔离级别,每个级别会引发什么问题,mysql默认是哪个级别

1.脏读 脏读是指在一个事务处理过程里读取了另一个未提交的事务中的数据. 当一个事务正在多次修改某个数据,而在这个事务中这多次的修改都还未提交,这时一个并发的事务来访问该数据,就会造成两个事务得到的 ...

- php中_initialize()函数与 __construct()函数的区别说明

_initialize()方法是在任何方法执行之前,都要执行的,当然也包括 __construct构造函数. 也就是说如果存在_initialize()函数,调用对象的任何方法都会导致_initial ...

- 50行代码写的一个插件,破解一个H5小游戏

小游戏链接:测测你的眼睛对色差的辨识度http://www.webhek.com/post/color-test.html?from=timeline 废话不多说,先放代码: window.onloa ...

- C++内容记录

仅个人记录 https://ke.qq.com/course/336509 M了个J - 博客园 https://www.cnblogs.com/mjios/

- android Vitamio Live 实时视频 记录

Vitamio 下载地址: https://github.com/yixia/VitamioBundle/releases https://github.com/yixia/VitamioBundle ...

- 008-网络抓包工具-wireshark

一.概述 二.安装 三.使用 3.1.基础设置 语言:WireShark→首选项→语言 3.2.使用过程 打开软件,选择对应的网卡, Filter:设置对应的关键词后,点击回车或者右侧箭头 如,协议: ...

- java+断点续传

在Web应用系统开发中,文件上传和下载功能是非常常用的功能,今天来讲一下JavaWeb中的文件上传和下载功能的实现. 先说下要求: PC端全平台支持,要求支持Windows,Mac,Linux 支持所 ...

- intel 酷睿core系列cpu的类型:U M H HQ MQ

相对于笔记本来说.一般我们说的intel系列cpu是指应用于desktop桌面版,embedded嵌入式版, mobile移动版 桌面版和移动版cpu对比 http://tieba.baidu.com ...