RF layout check list

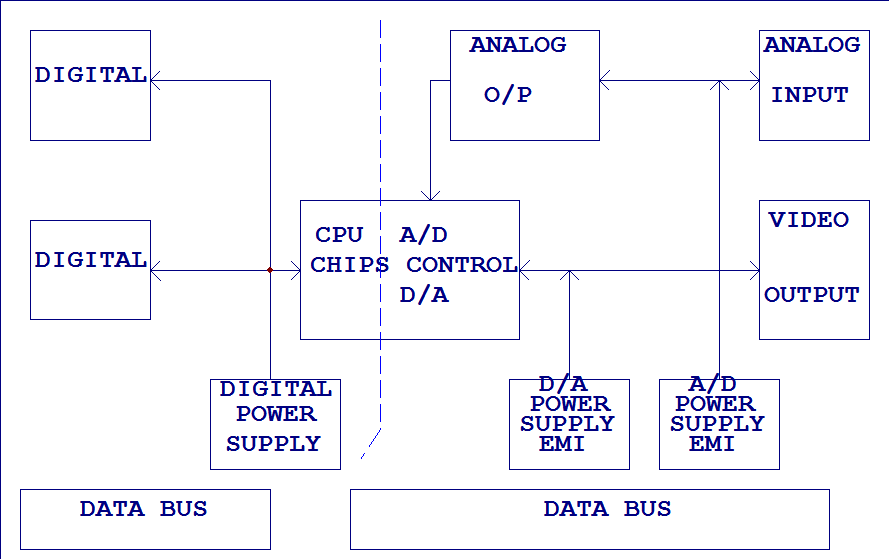

Analog-digital circuit

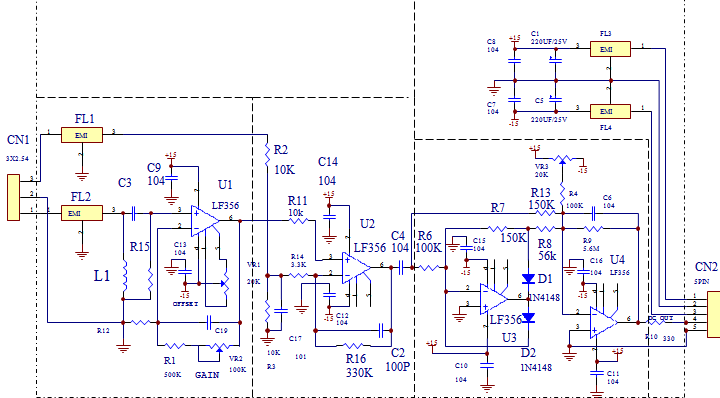

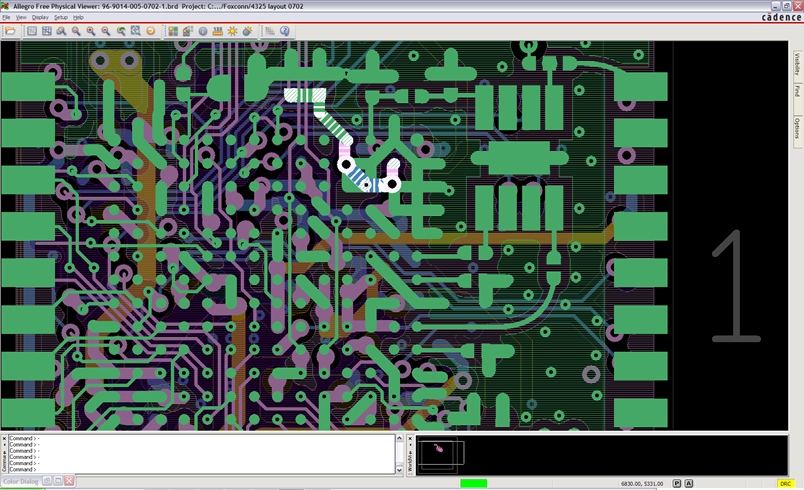

1. Insure C36 and C33 placed next to each other to avoid open stubs

2. Keep UART lines away from 26 MHz traces

3. Keep 26 MHZ traces away from all noisy signals including UART and PCM as well as FM VDD and FM RF PORT

4. Keep 32 KHz trace away from all noisy signals

5. The routing and placement of C39 & C45 are very critical to the PA performance:

PAA needs 0.1uF, and PAG needs 1uF.

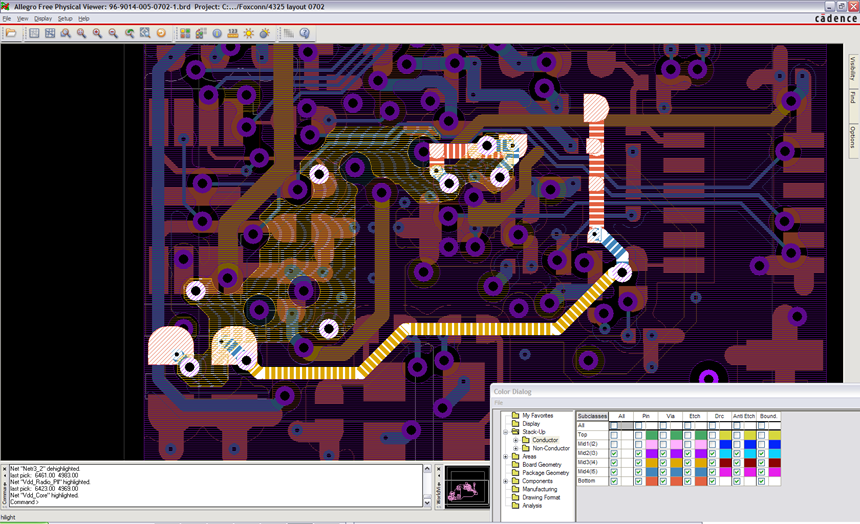

In terms of layout, PAA and PAG branches stay separate on all layers. Keep branches separate as long as possible all the way back to the main 3.3V Boost supply.

Keep the PAG trace as wide as possible, with a minimum of 2 via for any layer changes.

6. place 8.2pF capacitor close to BT_VDDTF pin C42 to L14

7. place a .1uF bypass capacitor on BT_VDDO pins C29 to G8&N2

8. Place a 1000pF capacitor near BT_VDDPLL pin C69 to P14

9. Isolate BT_VDDC from the VDDC rail with a 600 OHM FB do not pace any bypass caps on these pins

10. It is VDD_2P5 in this schematic Also place this capacitor close to the chip and keep away from all noisy components keep the trace to FM VDD as short as possible

11. As on the previous review, please keep the VPP of 32KHz clock < 1.8V from FM RF perspective. VDDIO is rated from 1.8V to 3.3V as addressed on the datasheet. Check with this LPO vender for the spec.

12. Place .01uF bypass cap near FM_VDD VCO C11 to M10

13. Thanks for the change. Again, the routing and placement of C39 & C45 are very critical to the PA performance: C39 to PAG C45 to PAA

PAA needs 0.1uF, and PAG needs 1uF.

In terms of layout, PAA and PAG branches stay separate on all layers. Keep branches separate as long as possible all the way back to the main 3.3V main supply.

Keep the PAG trace as wide as possible, with a minimum of 2 via for any layer changes.

14. L10 should be placed close to the chip output A3 &A1. C22 could be placed close to A3 &A1 or L10.

15.Move C35 close to chip input pins in the layout.

16. VDDIO_RF needs to isolate from VDDIO_SD and VDDIO. Need to use VDD3_3 for VDDIO_RF, and use regulated vdd3_3_ext to power VDDIO_SD and VDDIO.

17. Move C35 close to chip input pins in the layout.

18.Remove C19 & C53. They won't be needed for most of the cases.

RF layout check list的更多相关文章

- Linux初接触设置笔记01

没事装Linux尝试一下,来来回回装无数次,把刚开始需要设置的东西自己收藏一下,针对Centos7 装完Centos默认会覆盖windows引导,所以首先要做的是恢复windows的引导,如果不恢复, ...

- java项目测试log4j

.literal { background-color: #f2f2f2; border: 1px solid #cccccc; padding: 1px 3px 0; white-space: no ...

- MTD中的nand驱动初步分析---面向u-boot

之前提到nand驱动的初始化分析,有一个结构体 struct mtd_info始终贯穿这些代码 再来分析一下这个结构体的基本功能,如何初始化,如何使用 一.分析过程 看看结构体的出现和使用方式 第一次 ...

- 自制ZigBee协议分析仪

关键词 ZigBee Sniffer 协议 分析仪 自制 CC2530 CC2531 在开发ZigBee / Bluetooth的过程,难免会要用到Sniffer工具,Packet Sni ...

- puppeteer(五)chrome启动参数列表API

List of Chromium Command Line Switches https://peter.sh/experiments/chromium-command-line-switches/ ...

- CEF 支持的命令行参数

参考:https://peter.sh/experiments/chromium-command-line-switches/ List of Chromium Command Line Switch ...

- 【转】非常实用的高频PCB电路设计70问

1.如何选择PCB 板材? 选择PCB 板材必须在满足设计需求和可量产性及成本中间取得平衡点.设计需求包含电气和机构这两部分.通常在设计非常高速的 PCB 板子(大于 GHz 的频率)时这材质问题会比 ...

- Kivy折腾笔记

最近想用Python开发APP,选择kivy,记录过程 首先是源码安装,各种蛋疼的报错放弃了.cython高版本有问题. python3 -m pip install cython==0.23 pyt ...

- 2019.3.22 Week 11 : ZigBee power test and field test

Test require Zigbee sample:EFR32MG13 (RF layout has ) Gateway N4010A : 2.5Ghz 1Power test 2Field te ...

随机推荐

- 全面理解虚拟DOM,实现虚拟DOM

1.为什么需要虚拟DOM DOM是很慢的,其元素非常庞大,页面的性能问题鲜有由JS引起的,大部分都是由DOM操作引起的.如果对前端工作进行抽象的话,主要就是维护状态和更新视图:而更新视图和维护状态都需 ...

- 论文笔记——Deep Model Compression Distilling Knowledge from Noisy Teachers

论文地址:https://arxiv.org/abs/1610.09650 主要思想 这篇文章就是用teacher-student模型,用一个teacher模型来训练一个student模型,同时对te ...

- Ubuntu 14.04 下 安装Protocol Buffers

参考: Protocol Buffers - Google's data interchange format Ubuntu 14.04 下 安装Protocol Buffers 环境 Ubuntu ...

- mysql 对比两个表的一致性

-- A和B两个表 数据是否一致select 自定义 from A left join B on A.id = B.id where B.id is null 注释:这样查询的结果是A表中有而B表中没 ...

- AtCoder square869120 Contest #3 F sushi

本文版权归ljh2000和博客园共有,欢迎转载,但须保留此声明,并给出原文链接,谢谢合作. 本文作者:ljh2000 作者博客:http://www.cnblogs.com/ljh2000-jump/ ...

- Qt5_自定义处理Windows消息函数

ZC:(1).“#include <QAbstractNativeEventFilter>”,(2).貌似 返回True(意思是 处理过了) 返回False(意思是还需要继续处理) 1.参 ...

- Fragment之间的交互

通常,一个活动可能包含一个或多个协同工作的Fragment以向用户展现一致的UI.在这种情况下,Fragment之间就需要彼此通信并交换数据,这是非常重要的.例如,一个Fragment可能包含了一个条 ...

- Tomcat启动之异常java.lang.IllegalStateException

严重: Exception sending context destroyed event to listener instance of class org.springframework.web. ...

- 2018年全国多校算法寒假训练营练习比赛(第一场)D N阶汉诺塔变形

https://www.nowcoder.com/acm/contest/67/D 思路: 先手动模拟一下过程,以下是模拟过程,按顺序表示第几步需要移动的盘标号 1 1 2 1 1 2 1 1 3 1 ...

- angular5 ng-content使用方法

先自定义一个组件import { Component } from '@angular/core'; @Component({ selector: 'exe-greet', template: ` & ...