FPGA小白学习之路(4)PLL中的locked信号解析(转)

ALTPLL中的areset,locked的使用

转自:http://www.360doc.com/content/13/0509/20/9072830_284220258.shtml

今天对PLL中areset和locked详细查了下资料,发现网上这方面的资料很少,所以自己认真读了下Documentation---ug_altpll.pdf,现在我将我学到的内容总结如下:

areset简而言之就是高电平有效,对pll进行复位。

下面我们主要来认识一下locked信号:

Locked这个输出到底是干嘛用的呢,pdf中这样写道:

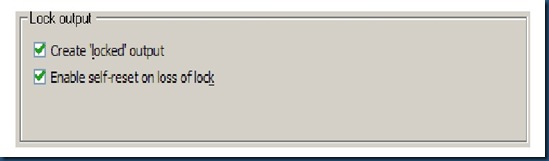

The ALTPLL megafunction allows you to monitor the PLL locking process using a lock signal named locked and also allows you to set the PLL to self-reset on loss of lock.

原来这Locked信号是用来观察pll输出时钟是否和输入时钟锁定。当锁定时,这个Locked信号就变为高电平。

但pdf中又这么写道:

The locked signal might toggle as the PLL begins tracking the reference clock. To avoid such a false lock indication, use a gated lock signal.

当这个pll刚开始跟踪输入时钟时这个Locked信号又可能会发生跳转,为了避免这种错误的指示,我们就使用gated lock信号。这个gated lock信号其实和locked信号是同一个,locked信号多了个计数功能后就叫做gated lock了。

You must specify the number of PLL input clock cycles to hold the locked signal low after the PLL is initialized

就是在pll被初始化之后,让gated lock依旧保持低电平多少个周期,以此来解决下面图片中的问题:

这图片中locked在pll开始跟踪输入时钟的时候一直在抖动,而gated lock因为设置了上面周期后,开始阶段始终为low,直到到达counter值后变为高电平,这就避免了locked的抖动。所以gated lock信号更加稳定。

这个时钟周期怎么算呢,如下:

To calculate the number of clock cycles needed, you must know the maximum lock time of the PLL, and the period of the PLL input clock. The lock time of the PLL is listed in the “PLL Timing Specifications” section of the DC & SwitchingCharacteristics chapter of the device handbook. The period of the PLL input clock is user-specified. For example, if the maximum lock time of a PLL is 1ms,and its input clock frequency is 100 MHz which corresponds to a 10 ns clock period, you calculate the value of the gated lock counter, by dividing 1 ms by 10 ns. The result is 100,000 clock cycles. 这个我就不解释了,大家自己看吧,很容易理解的。

不同器件类型对gated lock和self-reset的支持情况不一样

FPGA小白学习之路(4)PLL中的locked信号解析(转)的更多相关文章

- FPGA小白学习之路(1) System Verilog的概念以及与verilog的对比(转)

转自CSDN:http://blog.csdn.net/gtatcs/article/details/8970489 SystemVerilog语言简介 SystemVerilog是一种硬件描述和验证 ...

- FPGA小白学习之路(2)error:buffers of the same direction cannot be placed in series

锁相环PLL默认输入前端有个IBUFG单元,在输出端有个BUFG单元,而两个BUFG(IBUFG)不能相连,所以会报这样的错: ERROR:NgdBuild:770 - IBUFG 'u_pll0/c ...

- FPGA小白学习之路(5)clk为什么要用posedge,而不用negedge(转)

clk为什么要用posedge,而不用negedge 转自:http://www.cnblogs.com/dangxia/archive/2012/03/07/2383744.html Verilog ...

- FPGA小白学习之路(6)串口波特率问题的处理

串口波特率问题的处理 此博文一共包含三个方面的内容:(1)异步串口通信的数据格式:(2)为何串口通信中接收端采样时钟频率是传输的波特率的16倍:(3)串口波特率等概念. 1.异步串口通信的数据格式 串 ...

- USB小白学习之路(6) IIC EEPROM读取解析

IIC EEPROM读取解析 1. 编译错误处理(这里可以忽略) 在解压包解压了程序后,直接编译,出现如下错误. *** WARNING L14: INCOMPATIBLE MEMORY MODEL ...

- USB小白学习之路(1) Cypress固件架构解析

Cypress固件架构彻底解析及USB枚举 1. RAM的区别 56pin或者100pin的cy7c68013A,只有内部RAM,不支持外部RAM 128pin的cy7c68013A在pin脚EA=0 ...

- USB小白学习之路(10) CY7C68013A Slave FIFO模式下的标志位(转)

转自良子:http://www.eefocus.com/liangziusb/blog/12-11/288618_bdaf9.html CY7C68013含有4个大端点,可以用来处理数据量较大的传输, ...

- Qt 学习之路 2(4):信号槽

Home / Qt 学习之路 2 / Qt 学习之路 2(4):信号槽 Qt 学习之路 2(4):信号槽 豆子 2012年8月23日 Qt 学习之路 2 110条评论 信号槽是 Qt 框架引以 ...

- USB小白学习之路(8)FX2LP cy7c68013A——Slave FIFO 与FPGA通信(转)

此博客转自CSDN:http://blog.csdn.net/xx116213/article/details/50535682 这个博客只对自己理解CY7C68013的配置有一定的帮助,对于配置CY ...

随机推荐

- Codeforces1303F Number of Components

Description link 题意:给一个全\(0\)矩阵,每次支持一个修改,修改不还原(这要是还原了不就成\(A\)题了) 然后询问每一次修改完了当前矩阵的连通块个数 每一个修改的值单调不降 修 ...

- bzoj5104 Fib数列(BSGS+二次剩余)

快AFO了才第一次写二次剩余的题…… 显然应该将Fn写成通项公式(具体是什么写起来不方便而且大家也都知道),设t=((1+√5)/2)n,T=√5N,然后可以得到t-(-1)t/t=√5N,两边同时乘 ...

- 项目中关于RPC 和rocketMQ使用场景的感受

在花生待的这半年,切身体会了系统之间交互场景的接口技术实现方式,个人总结.仅供参考: 1.关于rpc接口,一般情况下 都是同步的.A系统的流程调用B系统.等着B返回,根据返回结果继续进行A接下来的流程 ...

- The website is API(2)

一.Beautifu Soup库 from bs4 import BeautifulSoup soup = BeautifulSoup(demo,"html.parser") Ta ...

- Lamda过滤替换List元素的属性值

import java.util.ArrayList;import java.util.HashMap;import java.util.Iterator;import java.util.List; ...

- linux chmod命令修改文件权限

在linux中,使用chmod命令修改一个文件的权限. 首先,我们查看一个文件夹下所有文件的权限 ls -l linux文件或目录的权限分为,读.写.可执行三种权限.文件访问的用户类别分为,文件创建者 ...

- ArcGIS自定义坐标变换中的方法说明

在10.1里面,一共提供了12种转换的方法,如下: Ø Geocentric_Translation Ø Molodensky Ø Molodensky_Abridged Ø Position ...

- 常用的GIT

# 初始化相关 git init git add . git commit -m "test001" git remote origin https://github.com/fa ...

- EncryptUtils

package me.zhengjie.core.utils; import org.springframework.util.DigestUtils; import javax.crypto.Cip ...

- 吴裕雄--天生自然 R语言开发学习:R语言的简单介绍和使用

假设我们正在研究生理发育问 题,并收集了10名婴儿在出生后一年内的月龄和体重数据(见表1-).我们感兴趣的是体重的分 布及体重和月龄的关系. 可以使用函数c()以向量的形式输入月龄和体重数据,此函 数 ...