DesignWareBuildingBlock IP的仿真与综合

感谢一下同学的协助,跑通了一个case。

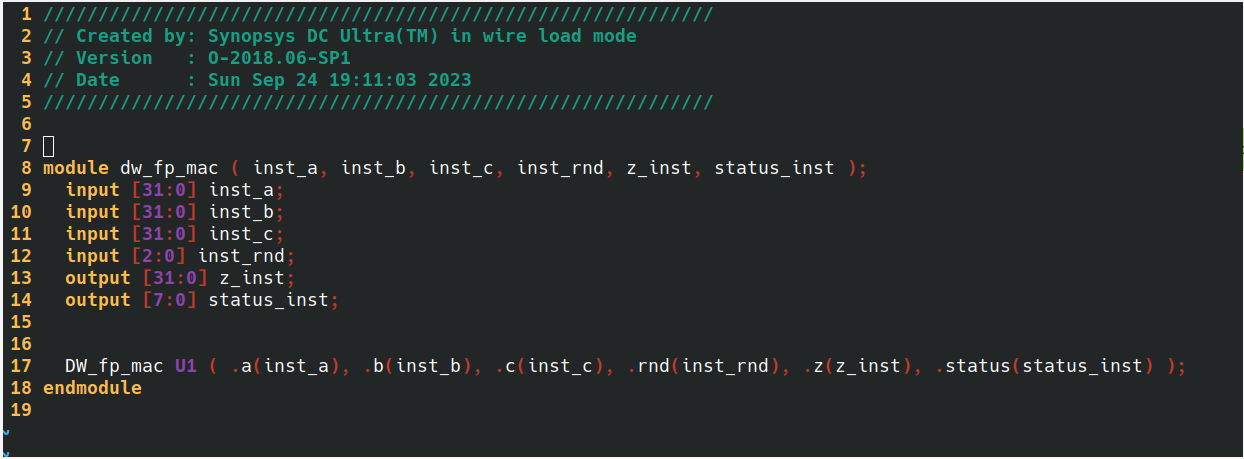

IP核调用 dw_fp_mac.sv

module dw_fp_mac( inst_a, inst_b, inst_c, inst_rnd, z_inst, status_inst );

parameter inst_sig_width = 23;

parameter inst_exp_width = 8;

parameter inst_ieee_compliance = 0;

input [inst_sig_width+inst_exp_width : 0] inst_a;

input [inst_sig_width+inst_exp_width : 0] inst_b;

input [inst_sig_width+inst_exp_width : 0] inst_c;

input [2 : 0] inst_rnd;

output [inst_sig_width+inst_exp_width : 0] z_inst;

output [7 : 0] status_inst;

// Instance of DW_fp_mac

DW_fp_mac #(inst_sig_width, inst_exp_width, inst_ieee_compliance) U1 (

.a(inst_a),

.b(inst_b),

.c(inst_c),

.rnd(inst_rnd),

.z(z_inst),

.status(status_inst) );

endmodule

需要在makefile里添加路径

SYNOPSYS = /home/synopsys/syn/O-2018.06-SP1

#start vcs compile

vcs_com:

cd ../work/vcs && vcs -sverilog -full64 +v2k -debug_pp -timescale=${TIMESCALE} -

cpp g++ -cc gcc -LDFLAGS -LDFLAGS -Wl,--no-as-needed -CFLAGS -fPIE -fsdb -f

../../prj/filelist.f -o ${OUTPUT} -l compile.log -y ${SYNOPSYS}/dw/sim_ver

+libext+.v+.inc +incdir+${SYNOPSYS}/dw/sim_ver

写了一个简单的tb

`timescale 1ps/1ps

module tb_dw_fp_mac;

// Parameters for testbench

parameter inst_sig_width = 23;

parameter inst_exp_width = 8;

parameter inst_ieee_compliance = 0;

// Inputs and Outputs

logic [inst_sig_width+inst_exp_width : 0] inst_a;

logic [inst_sig_width+inst_exp_width : 0] inst_b;

logic [inst_sig_width+inst_exp_width : 0] inst_c;

logic [2 : 0] inst_rnd;

wire [inst_sig_width+inst_exp_width : 0] z_inst;

wire [7 : 0] status_inst;

// Instantiate DW_fp_mac_inst

dw_fp_mac UUT (

.inst_a(inst_a),

.inst_b(inst_b),

.inst_c(inst_c),

.inst_rnd(inst_rnd),

.z_inst(z_inst),

.status_inst(status_inst)

);

task dump_output();

$dumpfile("out.vcd");

$dumpvars(0, tb_dw_fp_mac);

$fsdbDumpfile("tb_dw_fp_mac.fsdb"); //指定生成的的fsdb

$fsdbDumpvars("+all");//$fsdbDumpvars(0,tb_mesh);

//0表示生成u_rec_intra_top模 块及以下所有的仿真数据

$vcdpluson;

//下面这两个是保存所有仿真数据

$vcdplusmemon;

endtask

// Clock generation

logic clk = 0;

always #5 clk = ~clk;

// Reset generation

logic rst = 0;

initial begin

rst = 1;

#10 rst = 0;

end

// Test cases

initial begin

dump_output();

// Test case 1: Multiplication

inst_a = 32'h3F800000; // 1.0

inst_b = 32'h40000000; // 2.0

inst_c = 32'h3F000000; // 0.5

inst_rnd = 3'b000;

#20;

inst_a = 32'h40A9999A; // 5.3

inst_b = 32'h42C75EB8; // 99.685

inst_c = 32'h455C81FA; // 3528.123456 a*b+c = 7FFFFFFF (4,056.453956)

inst_rnd = 3'b000;

#20;

// Add more test cases here...

// Finish simulation

$finish;

end

// Monitor for displaying results

always_ff @(posedge clk) begin

$display("inst_a = %h, inst_b = %h, inst_c = %h, inst_rnd = %b, z_inst = %h,

status_inst = %h",

inst_a, inst_b, inst_c, inst_rnd, z_inst, status_inst);

end

endmodule

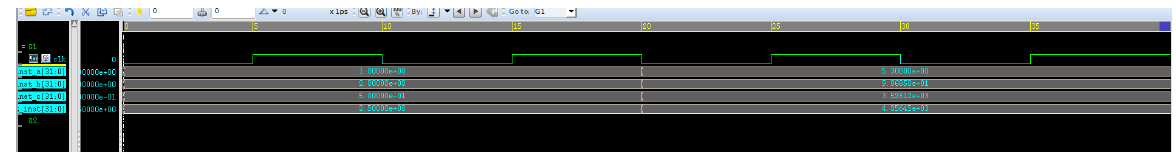

仿真结果

综合脚本:

set design_name "dw_fp_mac"

set stdcel_libs "

../../lib/logic/slow.db

"

set target_library "$stdcel_libs"

set synthetic_library "dw_foundation.sldb"

set link_library "* $target_library dw_foundation.sldb"

sh mkdir -p ./reports

sh mkdir -p ./outputs

set report_path "./reports"

set output_path "./outputs"

set_svf $output_path/${design_name}.svf

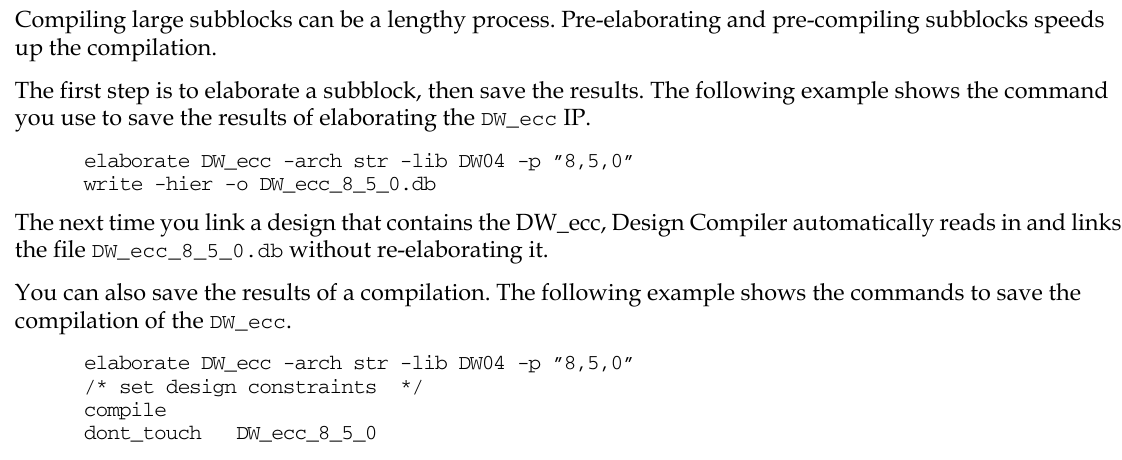

碰到的一个问题是最后吐出来的门级网表中没有IP的门级描述。

这样肯定是无法用于后端的。之前综合时使用的是compile_ultra -incremental命令,查阅DWBB的user_guide后发现:

于是在综合部分修改综合命令为compile:

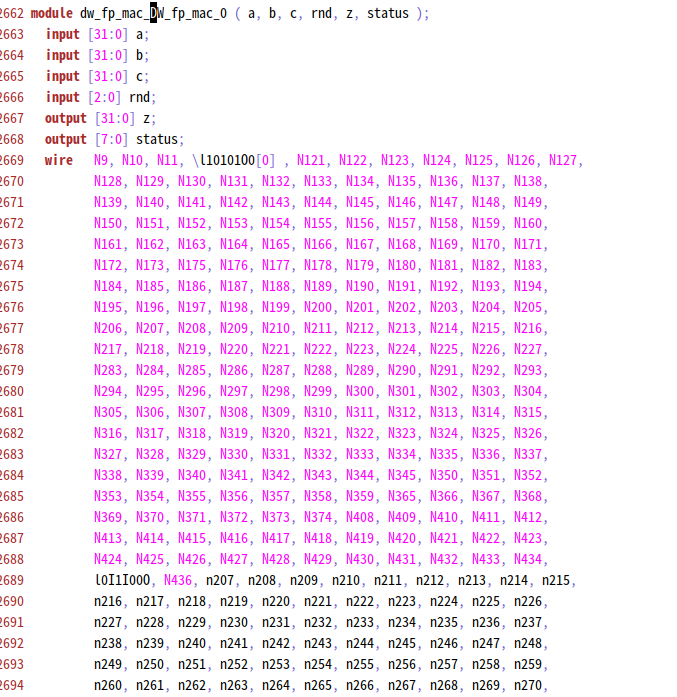

这样就产生了有门级描述的最终网表:

进一步试验后发现直接使用compile_ultra命令也可以,而且综合出的网表质量更高一些,只要去掉-incremental参数即可。-incremental代表进入增量工作模式,我们祖传脚本里就带了这个参数,但是一直没去细究含义,今天碰到这个坑了所以做个记录。

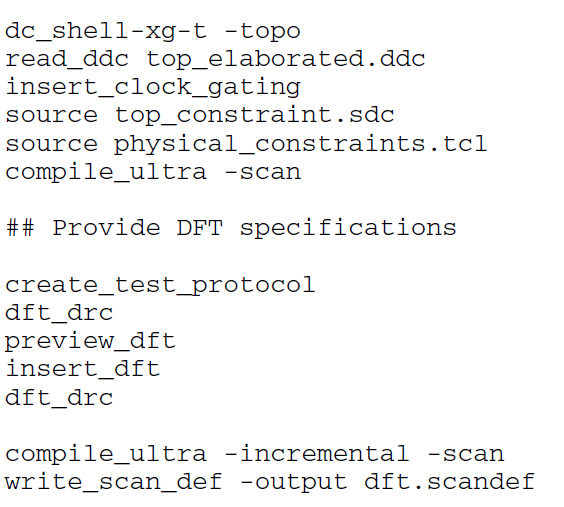

上面是dc user_guide里面的脚本例子,compile_ultra -incremental应该是在compile_ultra一次以后进行增量编译的操作。祖传脚本里却在没有前置的compile_ultra的情况下直接使用compile_ultra -incremental,在没有使用dw_foundation.sldb的情况下之前这样做没有碰到过问题,但是这次知道了实际上不可以的。

DesignWareBuildingBlock IP的仿真与综合的更多相关文章

- FIFO IP核仿真

FIFO IP核仿真 1.FIFO IP核配置 2.FIFO测试逻辑代码 首先往FIFO里面写入512个数据(FIFO深度的一半),然后再开始同时往FIFO里面写入,读出数据.FIFO读和写的时钟域不 ...

- ISE联合modelsim功能仿真和综合后仿真1

1.代码输入 (1).新建一个ISE工程,名字为count4. (2).新建一个verilog文件 (3).选择verilog module 输入file name为count4,单击next默认知道 ...

- ISE联合modelsim功能仿真和综合后仿真

1.代码输入 (1).新建一个ISE工程,名字为count4. (2).新建一个verilog文件 (3).选择verilog module 输入file name为count4,单击next默认知道 ...

- 用Modelsim仿真QuartusII综合后网表时库的添加方法(转)

这两天做综合后仿真,发现FPGA器件库又不会加了,无奈上网找方法.说起来不好意思,很早就接触Modelsim这个仿真软件了,可是没有好好琢磨.把这两天找的方法贴出来,再加上自己的理解,以后忘了可以上博 ...

- 数字集成电路设计-8-一个简单sobel图像边缘检测加速器的设计,实现,仿真与综合

引言 图像视频处理等多媒体领域是FPGA应用的最主要的方面之一,边缘检测是图像处理和计算机视觉中的基本问题,所以也是最常用的,随着数据量的不断增加以及对实时性的要求,一般软件已经不能满足实际需要,这时 ...

- vivado2016.2下系统自带DDR3 ip例程仿真运行

背景:从ISE14.7迁移到vivado2016.2. xilinx的软件改的真是不一般的大.两个软件操作差距真是让人想骂人.由于项目需要,准备调试DDR3.对于新手来说,例化一个DDR3 ip.如果 ...

- 初识QuartusII 9.0(破解,半加器的仿真,综合:下)

完成波形的随机设置(A,B任意给定高低电平即可,只是当作测试信号),选择任务栏Assignments[Setings],设置Simulation mode为functional,其余保持不变点击ok. ...

- 初识QuartusII 9.0(破解,半加器的仿真,综合:上)

由于在意大利期间,用的xilinx公司的ZYBO板子,相应的软件用ISE,SDK.回国买了altera公司的板子,自然也要学习国内较流行的软件(TB大西瓜家,因此相关例程也是大部分引用他家).Quar ...

- modelsim-altera IP核仿真

modelsim 仿真fifo时出现 Instantiation of 'scfifo' failed. The design unit was not found. 2012-07-21 13:27 ...

- Modelsimse10.1如何编译altera库文件以支持IP仿真

前言 se版本默认没有ip之类的库支持,如果你用到了pll之类的ip,仿真前就得把库编译好. 流程 本例用的是altera的verilog库. 1.首先在modelsim安装目录下新建altera文件 ...

随机推荐

- 面试官:谈谈你AI项目的具体实现?

在如今比较卷的 Java 面试市场,会 AI 技术是比较吃香的,它也可以作为一个技术或项目亮点,帮你拿到更多的面试机会,当然,也会帮你大大的提升面试的通过率. 但是在面试的过程中,如何展现你的 AI ...

- 获奖公告|RestCloud应用场景分享征稿大赛

- [AGC066C] Delete AAB or BAA

\(\mathbf{Part.-1}\) 给定一个由字符 A 和 B 组成的字符串 \(S\) . 在这根绳子上,您可以反复执行以下操作: 在字符串 \(S\) 中选择三个连续且相等的字符,这些字符要 ...

- vue cli mockjs

npm i -D mockjs 根目录新建 mock 文件夹 mock/utils.js const fs = require('fs'); const path = require('path'); ...

- AI应用开发-从Python入门到GPT集成实战

Python作为AI开发的首选语言,具有以下优势: 简洁易学:语法简单,上手快速 生态丰富:拥有强大的AI/ML库生态 社区活跃:大量开源项目和学习资源 广泛应用:从数据分析到深度学习都有涉及 Pyt ...

- NetCoreWebapi双向SSL自建证书演示程序

首先安装证书生成工具 OpenSSL 自行安装 一.创建根证书 生成key文件,输入密码: openssl genrsa -des3 -out root.key 生成请求证书文件,如果安装路径发生改 ...

- DHTMLX Gantt 甘特图计算工期少1天的问题解决及解决过程附带产生的问题解决

这几天在对之前开发的项目管理系统可视化部分当中的甘特图模块进行功能优化,过程中发现了之前未发现的Bug问题. 如下图所示,甘特图的工期计算结果少1天: 为此我排查了之前写的存储过程,对甘特图所需的du ...

- Senparc.AI 系列教程(二):配置大模型,开始开发应用

上一篇<Senparc.AI 系列教程(一):概要>中简要介绍了 Senparc.AI 所支撑的底层能力,本篇将介绍如何使用 Senparc.AI 打通 AI 算力,使用不同类型的大模型完 ...

- 谈谈 Qt 程序安装包的大小,以及简要打包指南

https://www.jianshu.com/p/0dd884a43de6 本文是水木社区KDE与Qt编程技术版版主的文章,我觉得写的很好,就转载过来了,原文地址:http://hgoldfish. ...

- json序列化数据超出最大值(maxJsonLength)

https://www.cnblogs.com/ellafive/p/13704301.html 1.序列化: 以下代码在对象过大时会报错:进行序列化或反序列化时出错.字符串的长度超过了为 maxJs ...