嵌入式ROM核的调用

本次设计的工具和源码在:http://download.csdn.net/detail/noticeable/9914766

课程目的:调用quartus II提供的rom(read only memory)进行系统项目设计

实验现象:将一组固定的波形数据以MIF的格式存储于fpga中使用IP核构建的片上ROM中,开发板上电后,系统从ROM 中读取数据,并将数据通过I/O口输出,使用signal TAP II取I/O口输出的数据,即可得到三角波形;并通过quartus II提供的in system memory content editor 工具在线更改ROM 中的数据,然后再次通过signal TAP II将更改后的波形读取出来。

知识点:1、mif文件的生成方法2、ROM IP核的使用。3、In-system memory content editor 内存查看工具的使用。4、signalTap II 调试工具的简单使用

开发流程:

首先,自己创建对应波形的mif文件,以便后面调用rom IP核的时候使用

可以自己创建一个文本,然后在文件中输入自己想自己想要显示的波形的数据再保存,但是这样设计使得设计过于繁琐,这里推荐使用软件mif_maker2010直接生成.mif文件(软件在源码压缩包中)

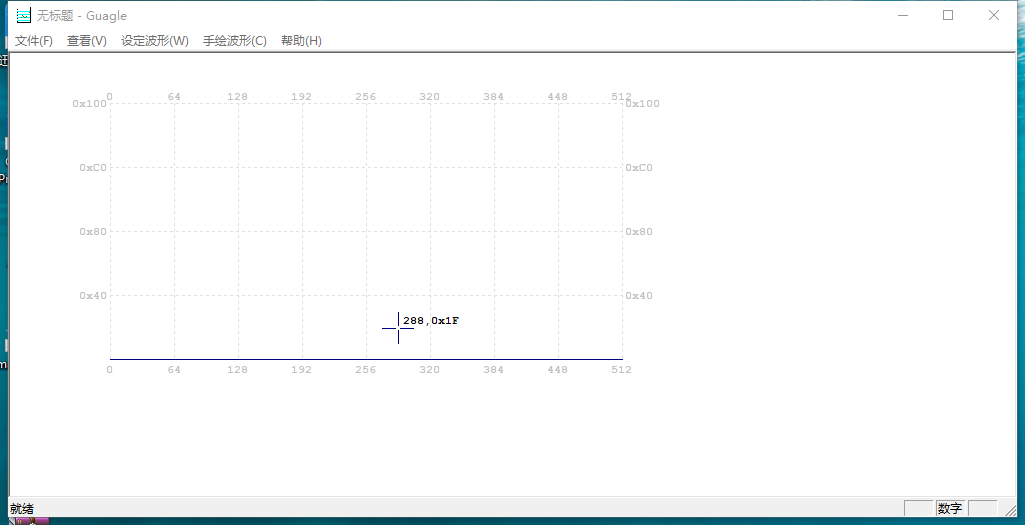

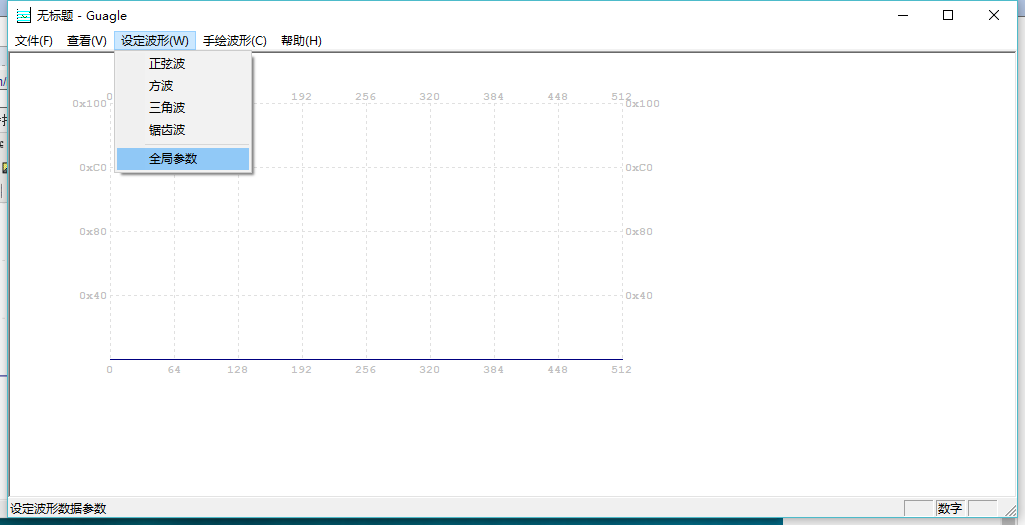

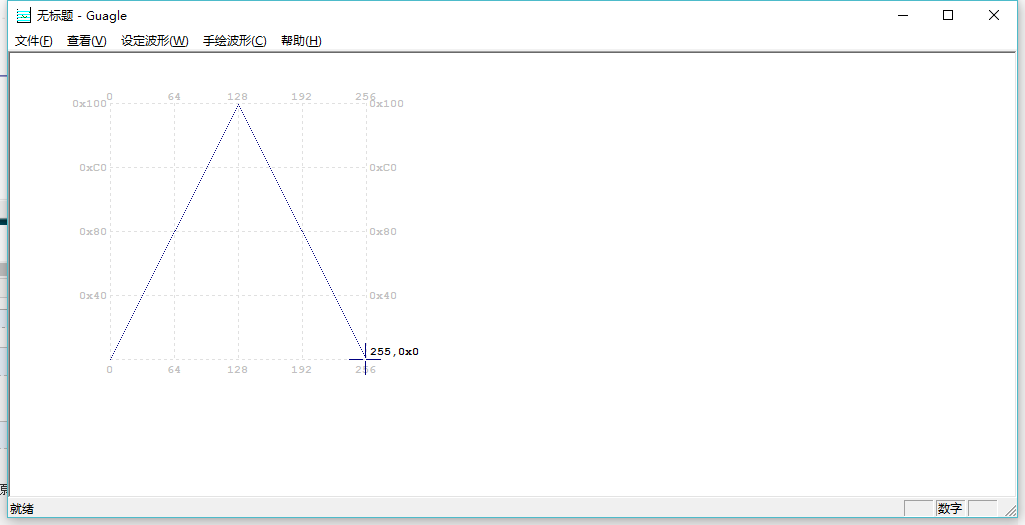

打开软件

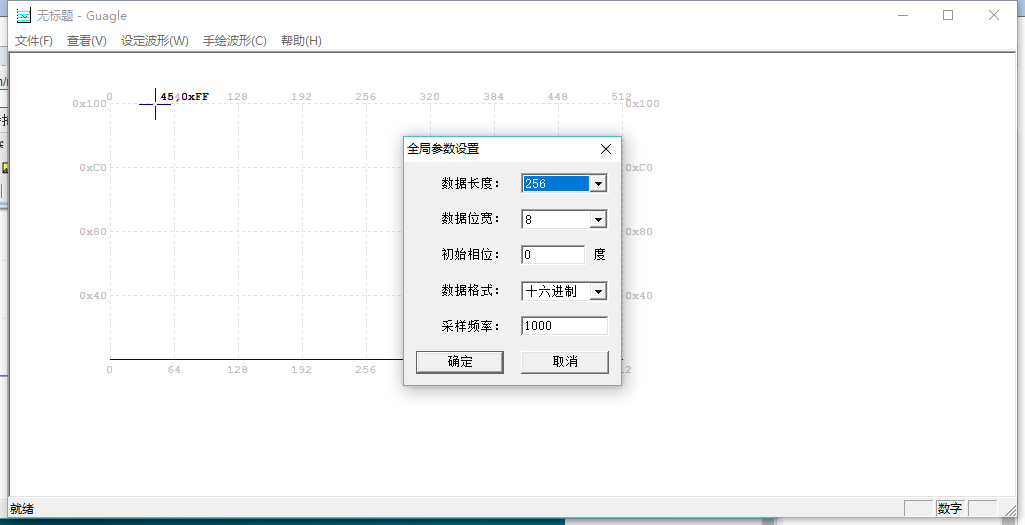

设置全局参数

本次设计为256个数据长度8位位宽

选择期望生成的波形,保存即可得到相应波形对应参数的mif文件。

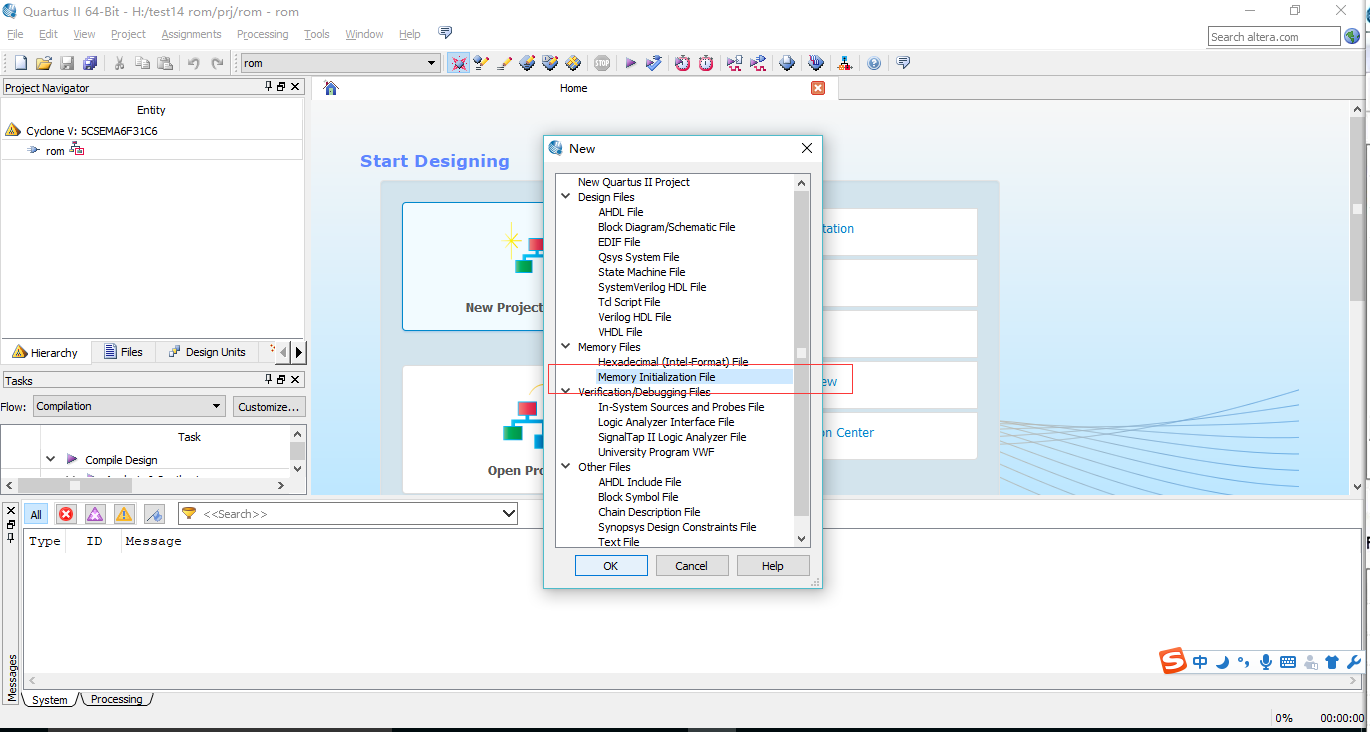

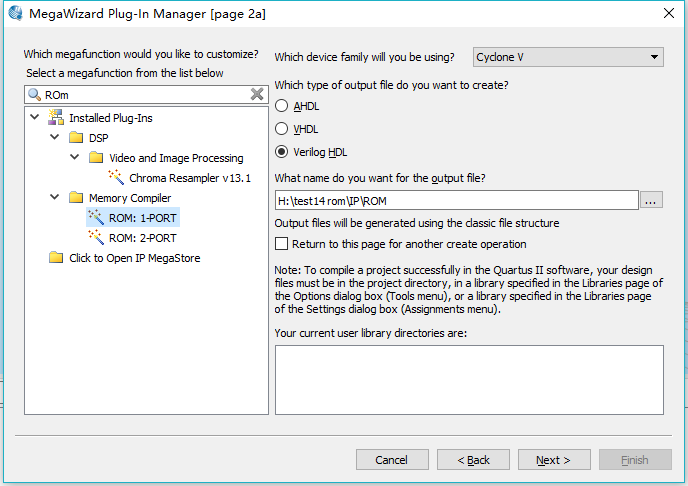

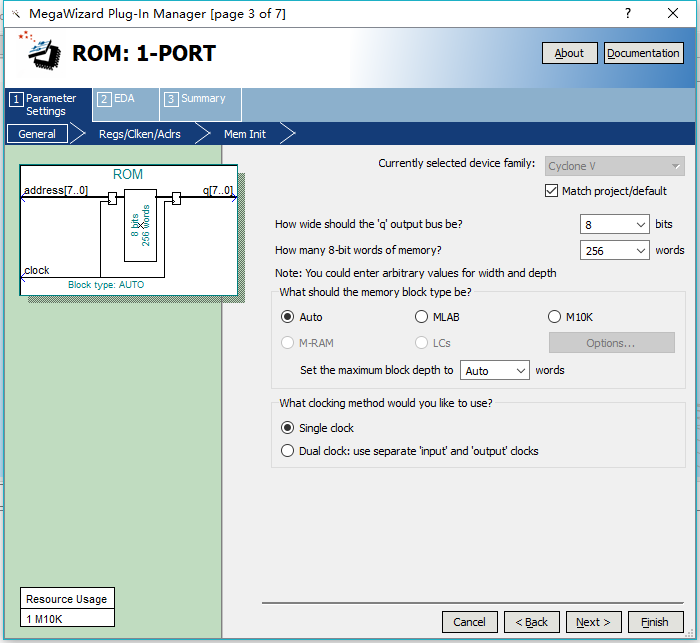

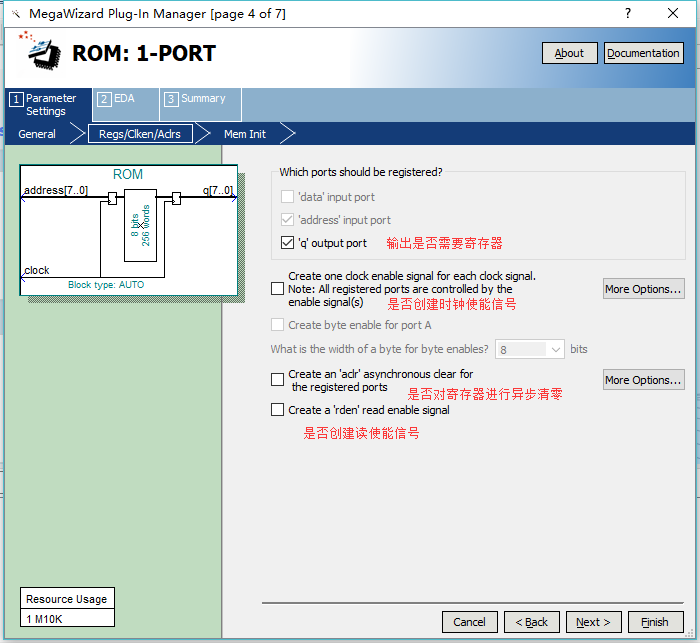

新建工程,调用rom ip核

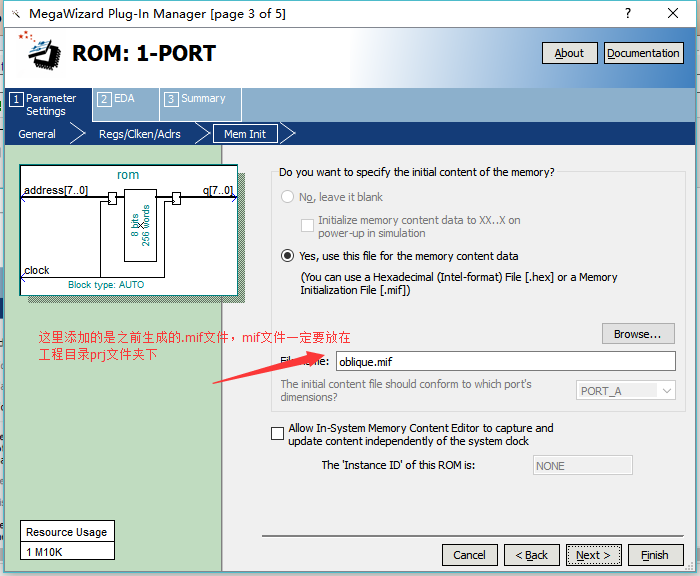

之后直接next到finish即完成生成rom文件了。

之后直接next到finish即完成生成rom文件了。

将IP核设置为顶层文件

然后编写IP核的testbench文件

`timescale 1ns/1ns

`define clock_period

module rom_tb;

reg [:]addr;

reg clk;

wire [7:0]q;

rom rom (

.address(addr),

.clock(clk),

.q(q));

initial clk=;

always#(`clock_period/)

clk=~clk; integer i;

initial

begin

addr=;

for(i=;i<=;i=i+)begin

#`clock_period;

addr=addr+;

end

#(`clock_period*);

$stop;

end endmodule

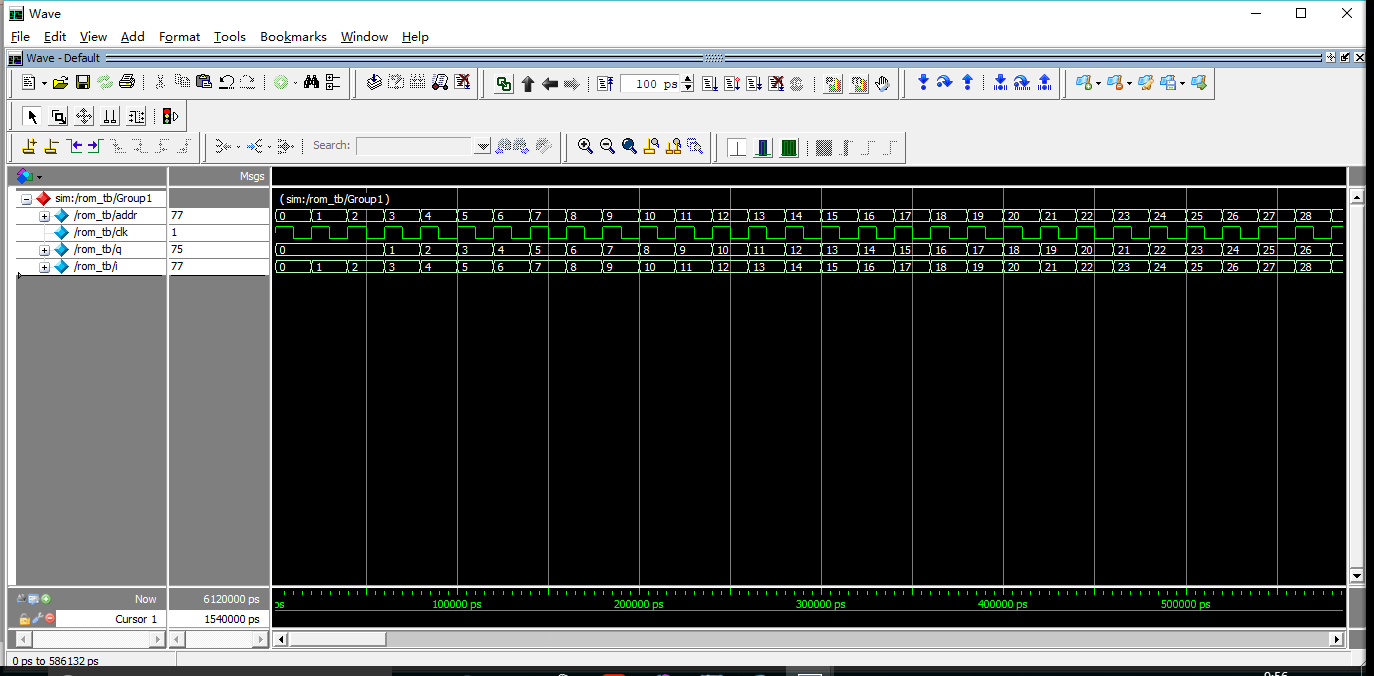

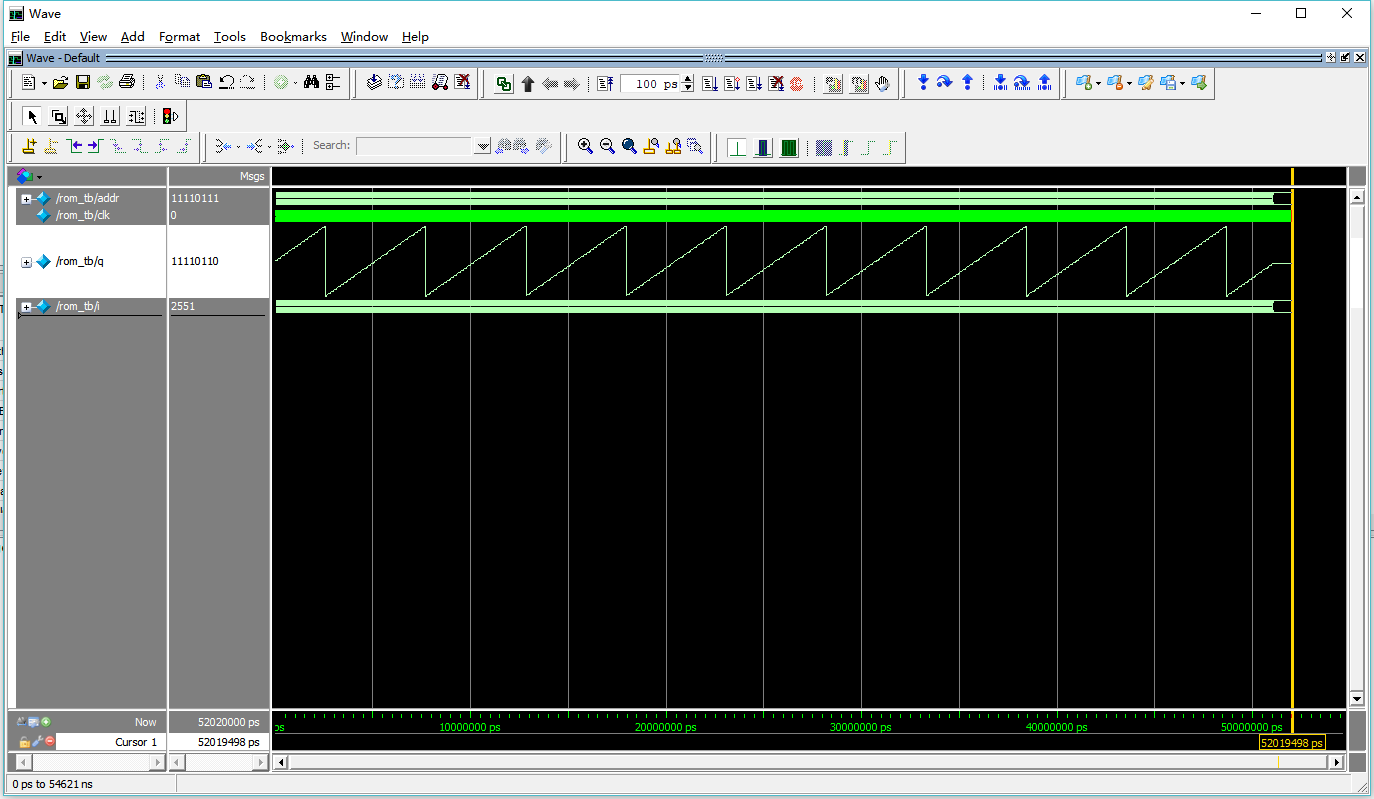

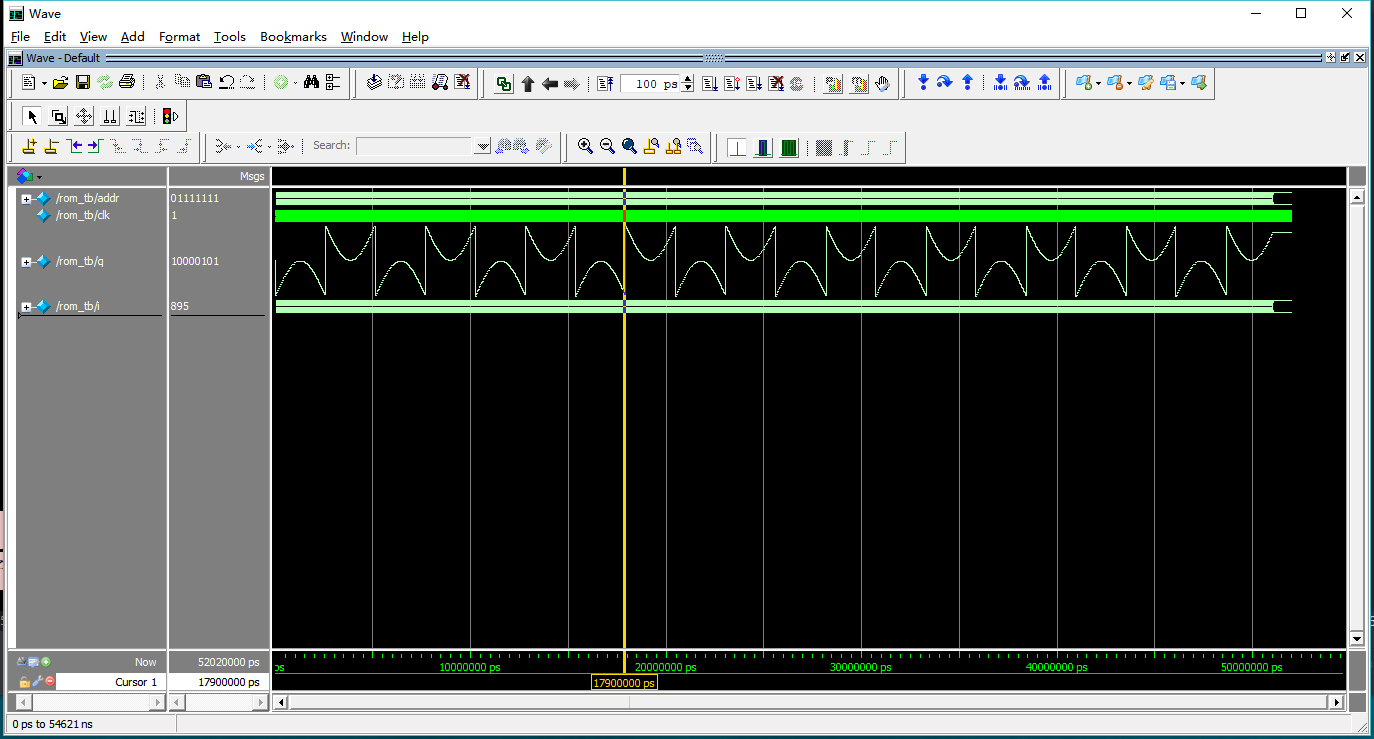

设定仿真路径进行仿真,可以看到q成功的将mif文件提取出来了,并通过仿真加强对romIP核的理解

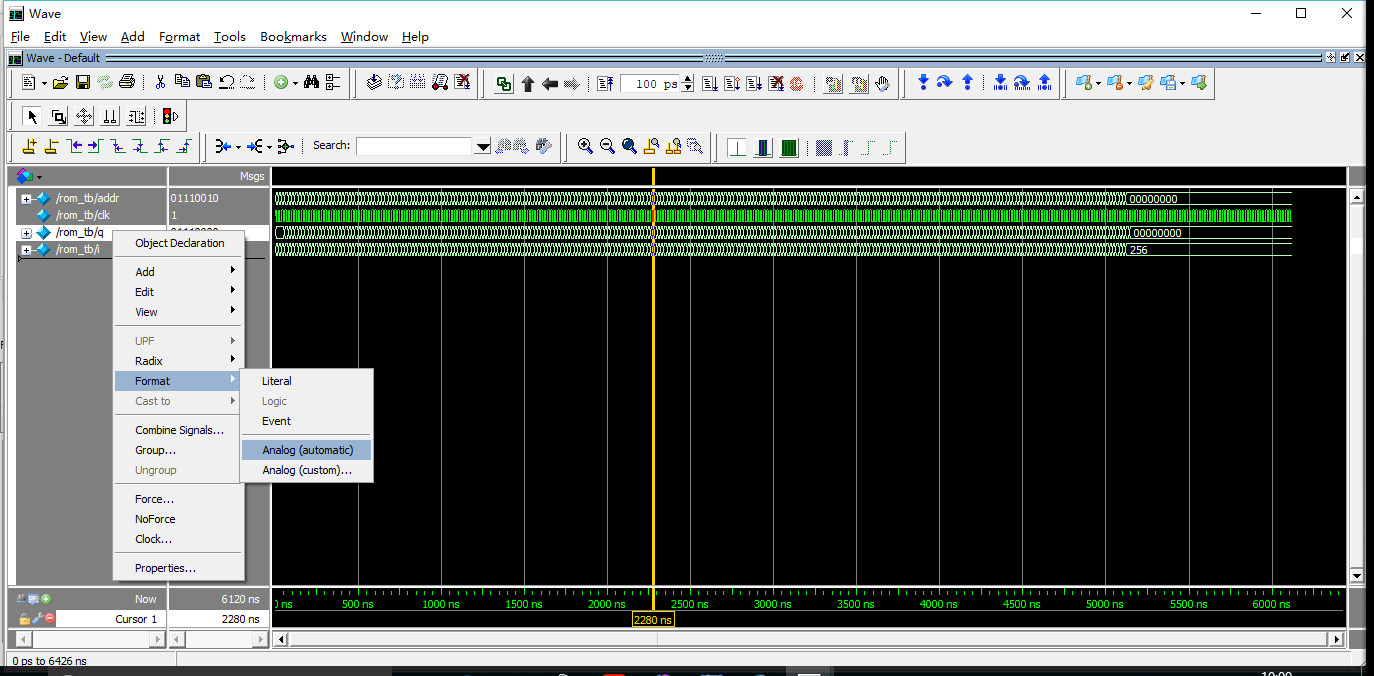

选中q,右键修改显示格式,即可看到仿真出来的模拟的锯齿波形。

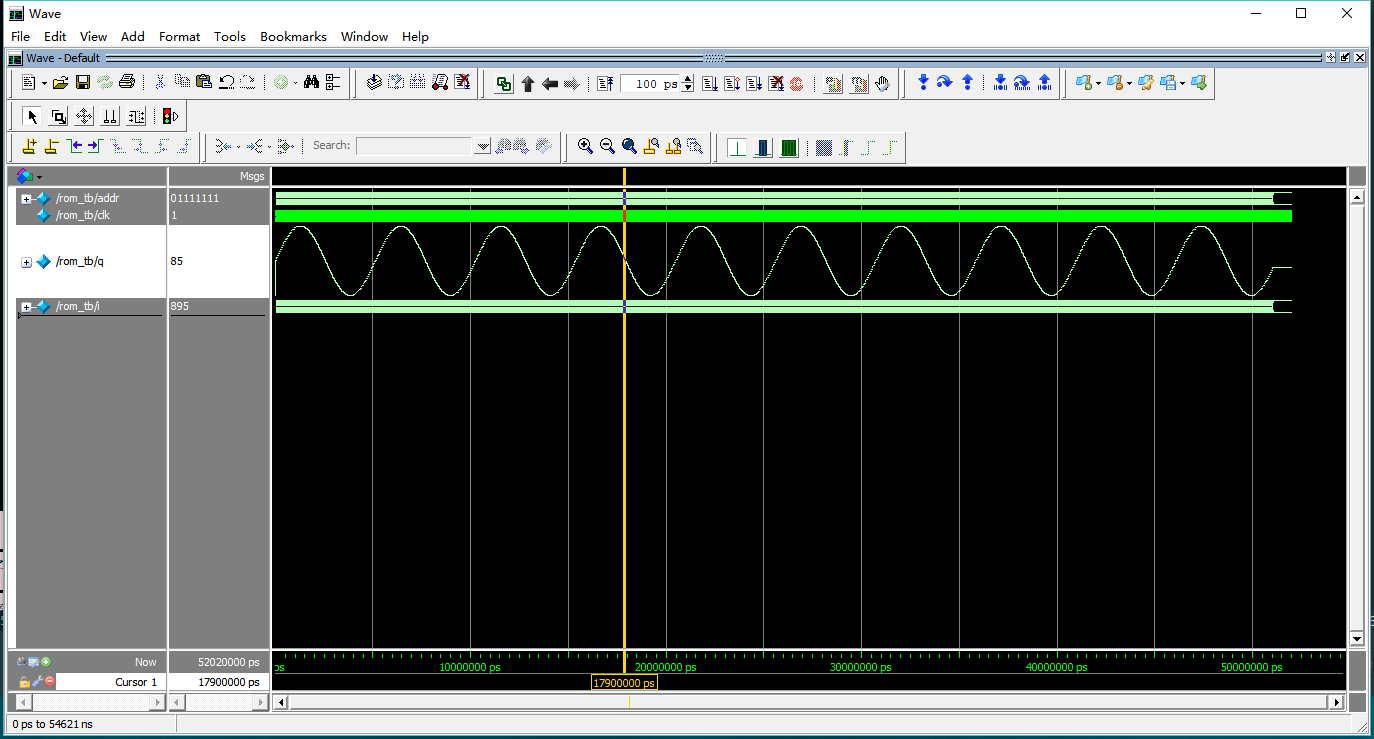

将mif未见改为正弦波的mif文件观察

此时发现波形有断层

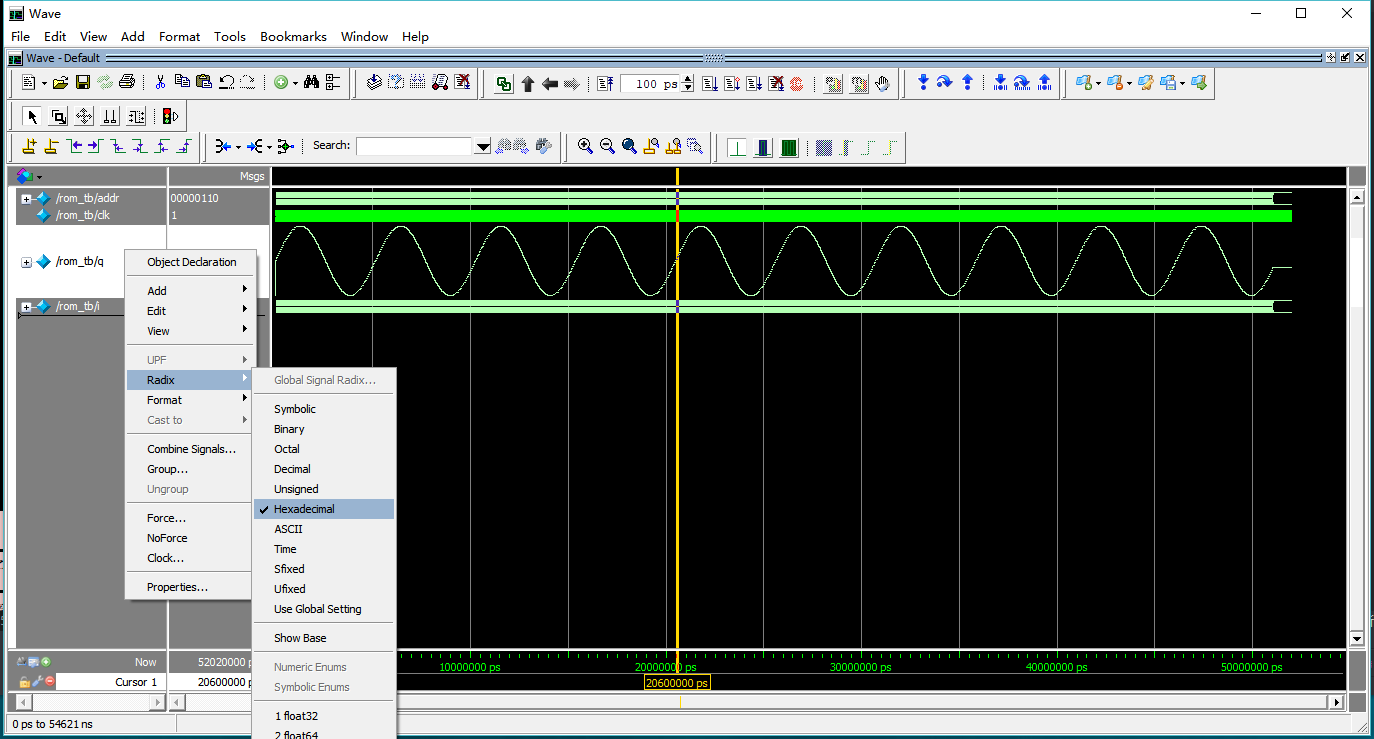

这是因为选择的显示格式为无符号的,将格式改为有符号的即可

在这里,波形发生器的仿真设计已经完成了(对于控制频率,其实就是一个控制地址变化的方式)。

新建一个rom_top文件,将其设置为顶层文件,其目的是设计地址发生模块:

module rom_top(clk,

rst_n,

q

); input clk;

input rst_n;

output [:]q;

reg [:]addr;

rom rom_1 (

.address(addr),

.clock(clk),

.q(q)); always@(posedge clk or negedge rst_n)

if(!rst_n)

addr<=;

else

addr<=addr+; endmodule

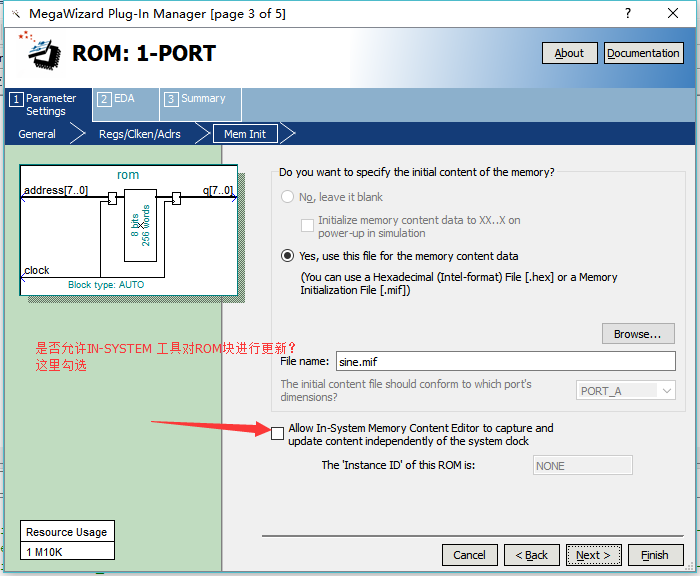

下面为了使in system memory content editor 工具在线修改ROM中的数据,需要对IP核进行设置

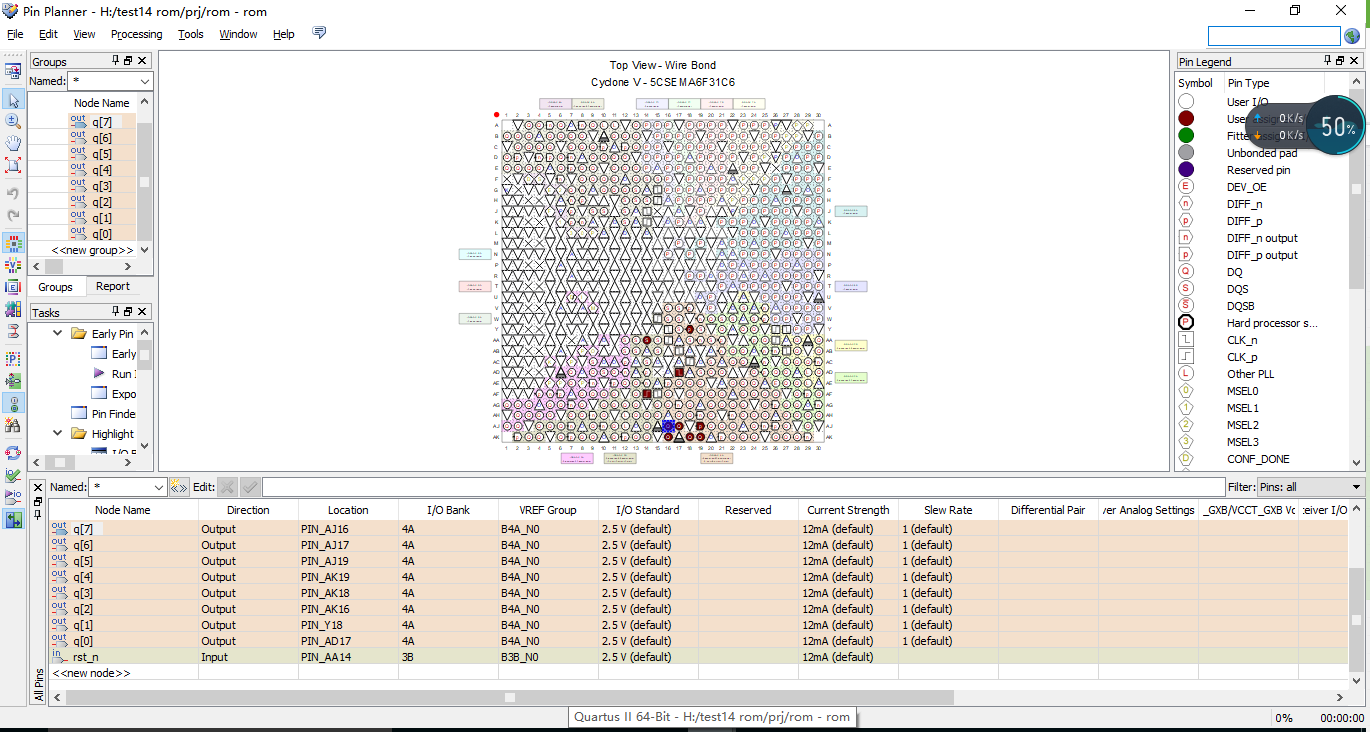

对引脚进行分配,其中q[0]~q[7]对应开发板上GOIP09~GPIO2

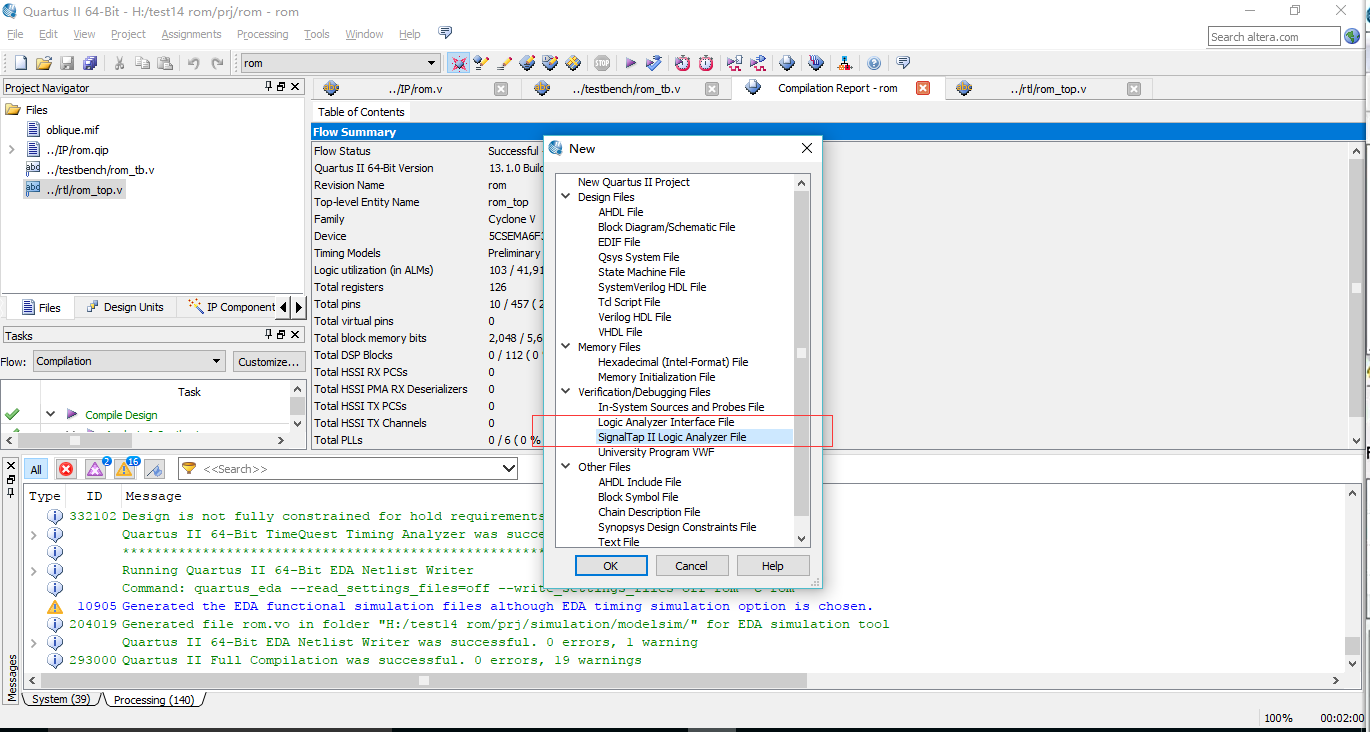

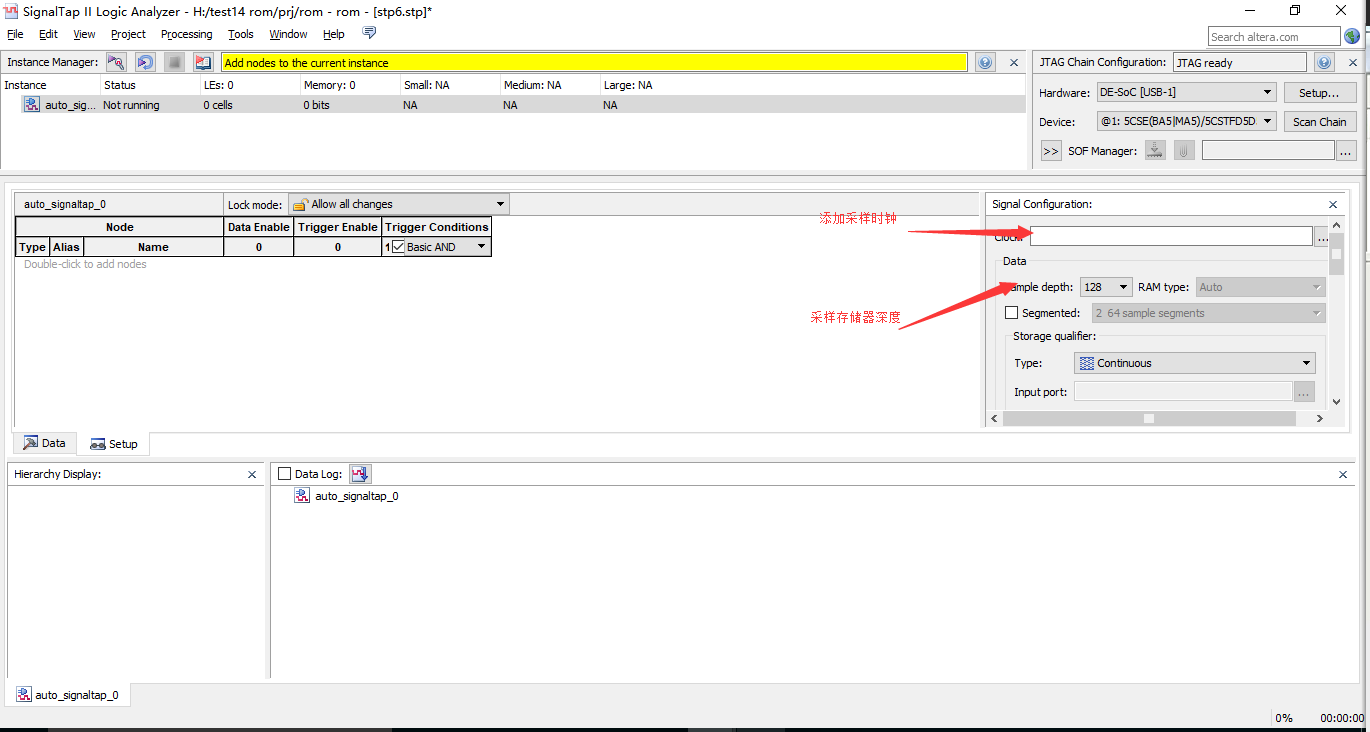

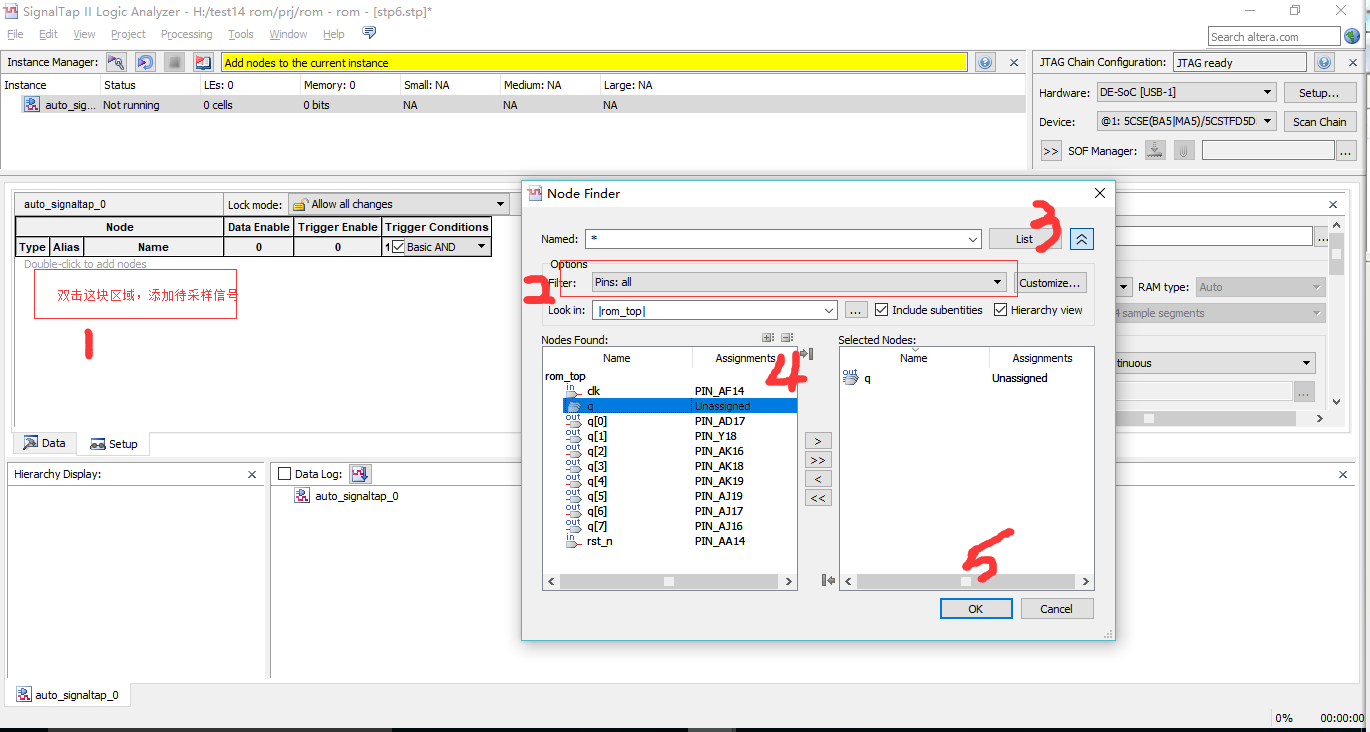

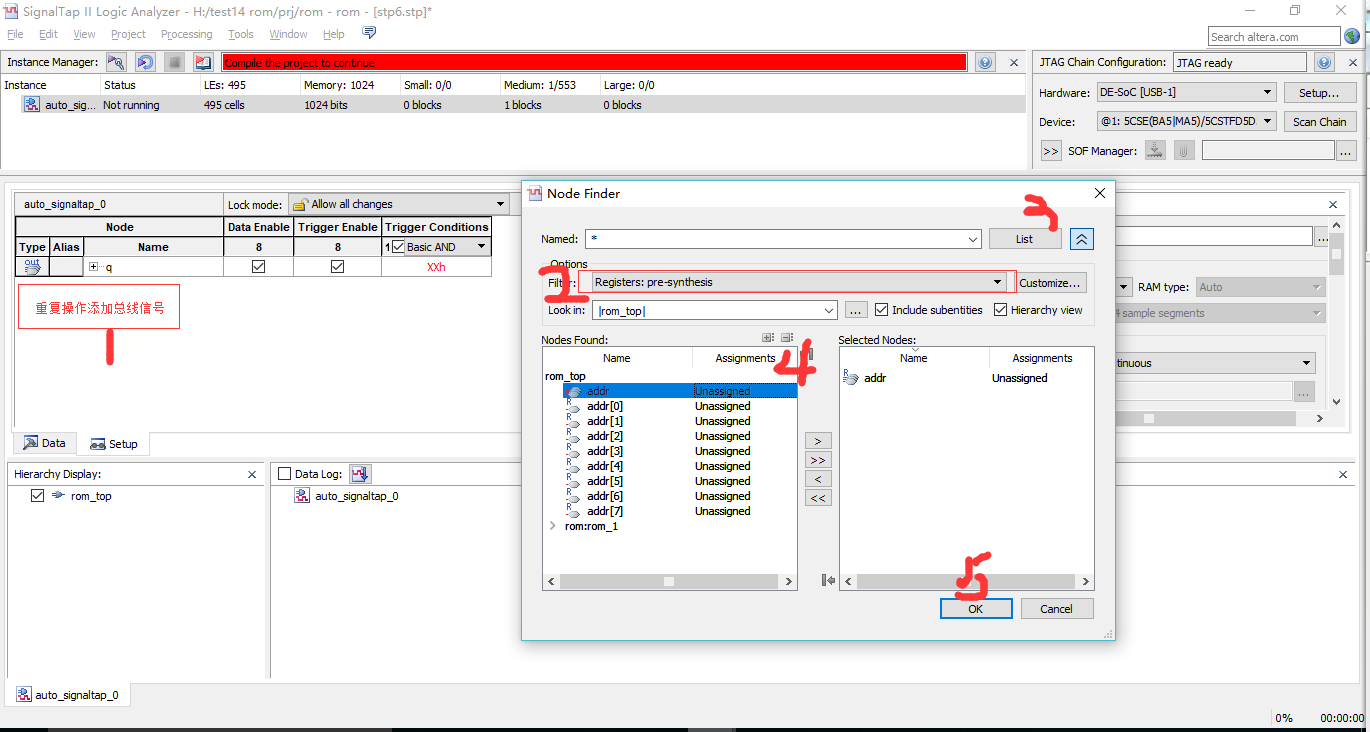

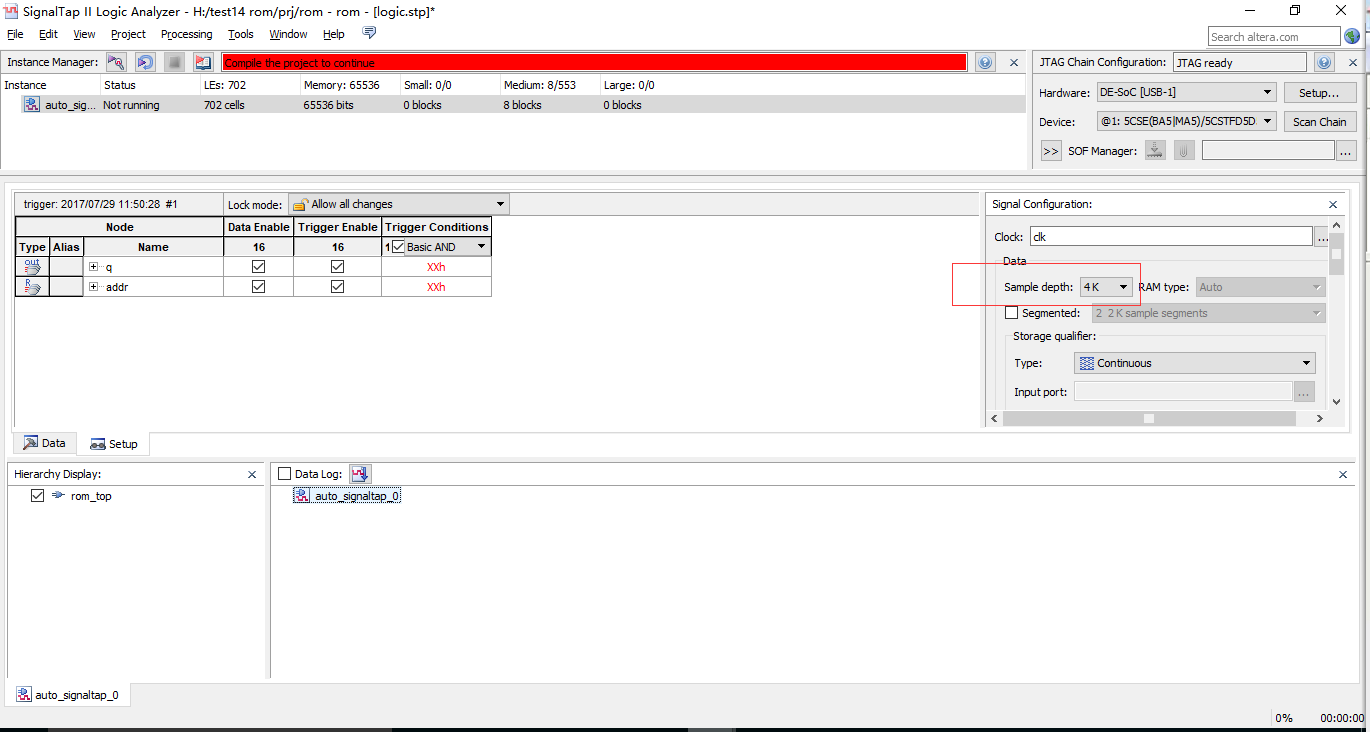

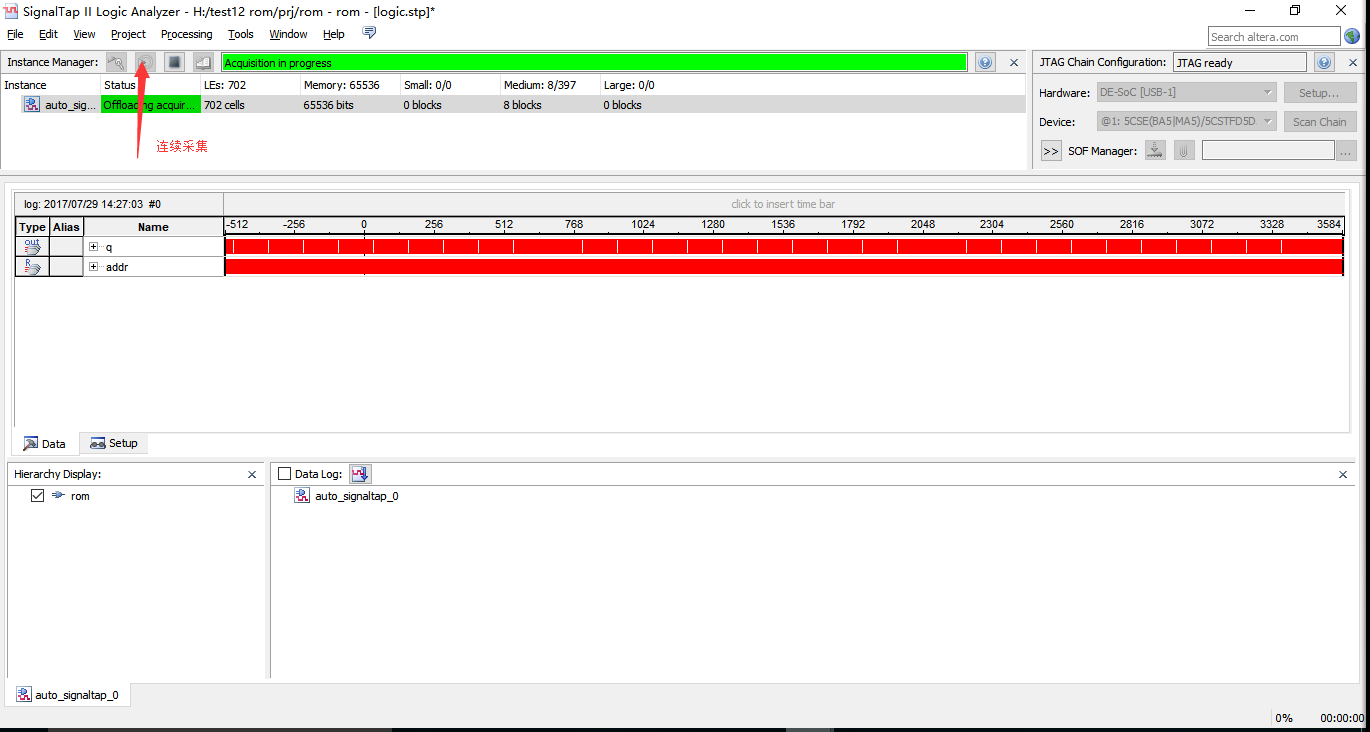

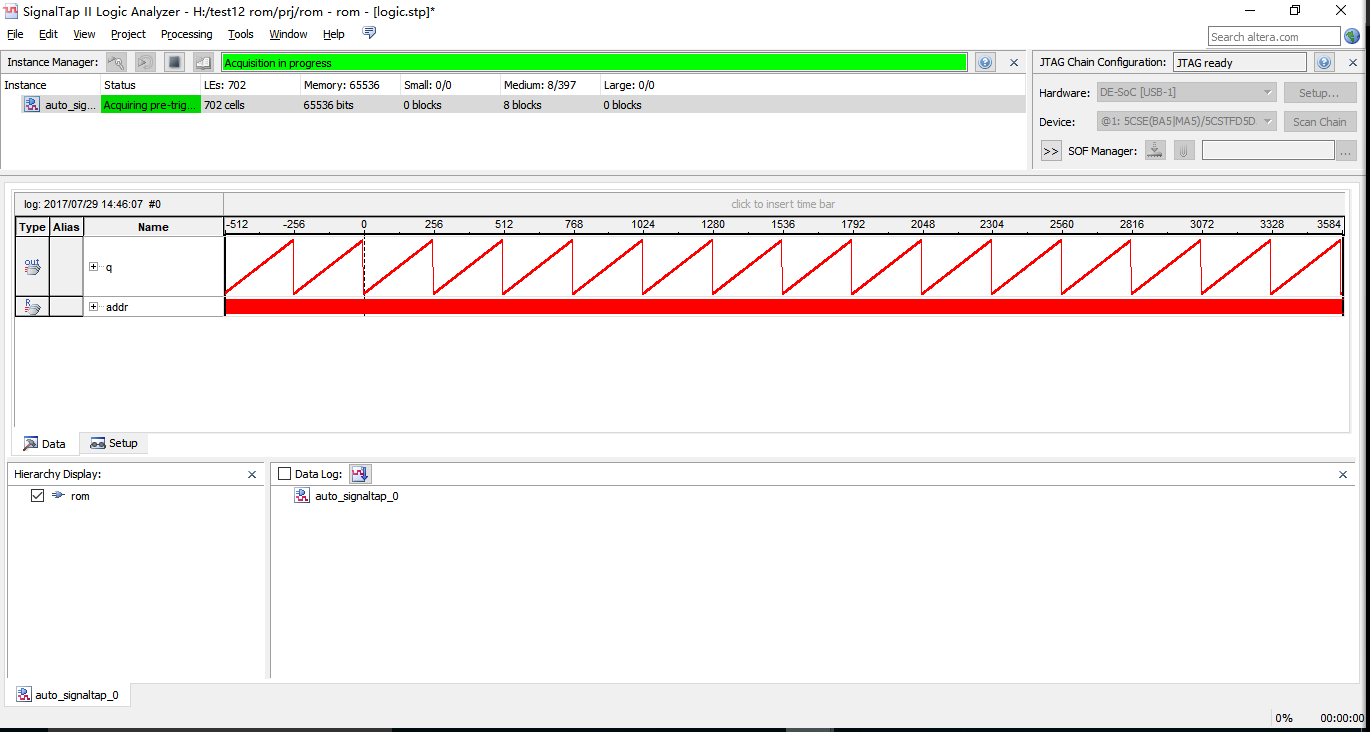

全编译后,通过FPGA内部搭建一个片上的逻辑分析仪,抓取rom里的文件:

新建一个signal tap II logic analyzer file文件

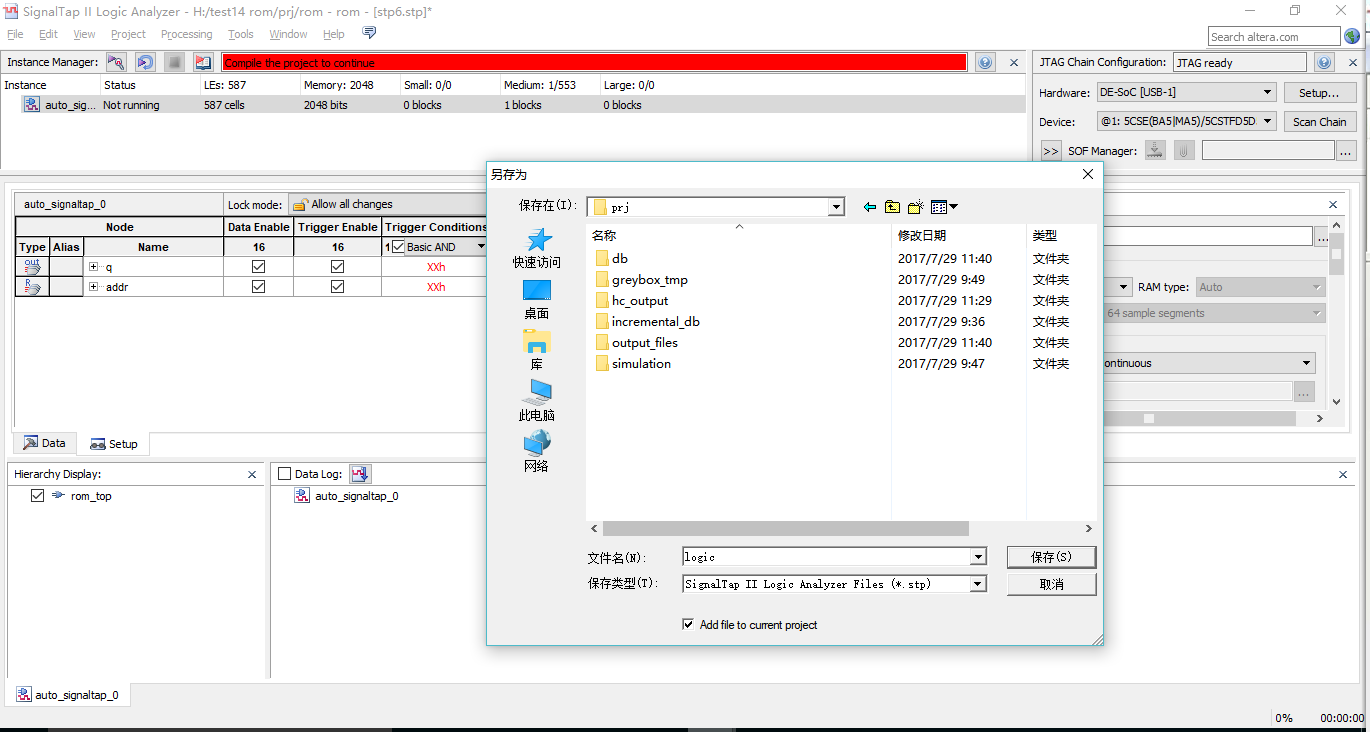

保存在工程目录下

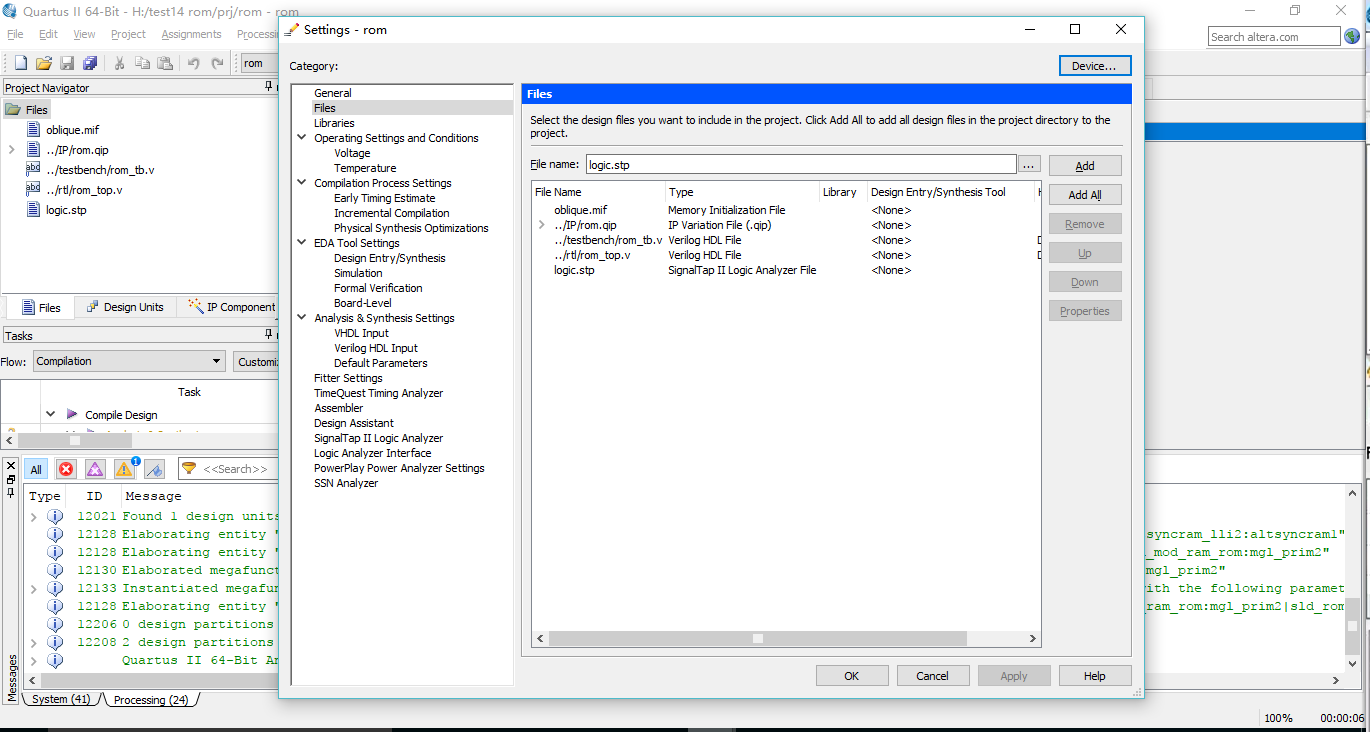

将逻辑分析仪工具添加到工程文件夹中,对工程进行全编译

将工程生成的.sof文件下载到FPGA开发板中,进行板级验证,烧写完成后打开logic.stp文件

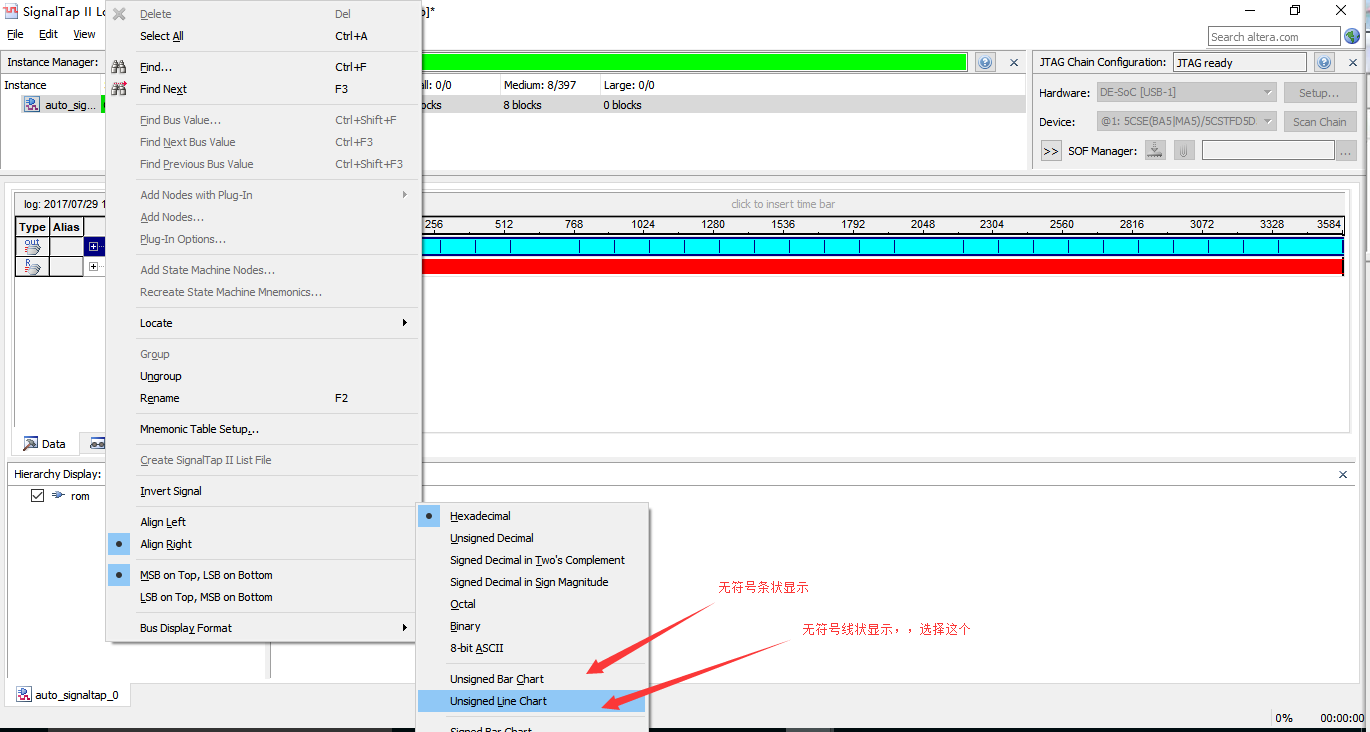

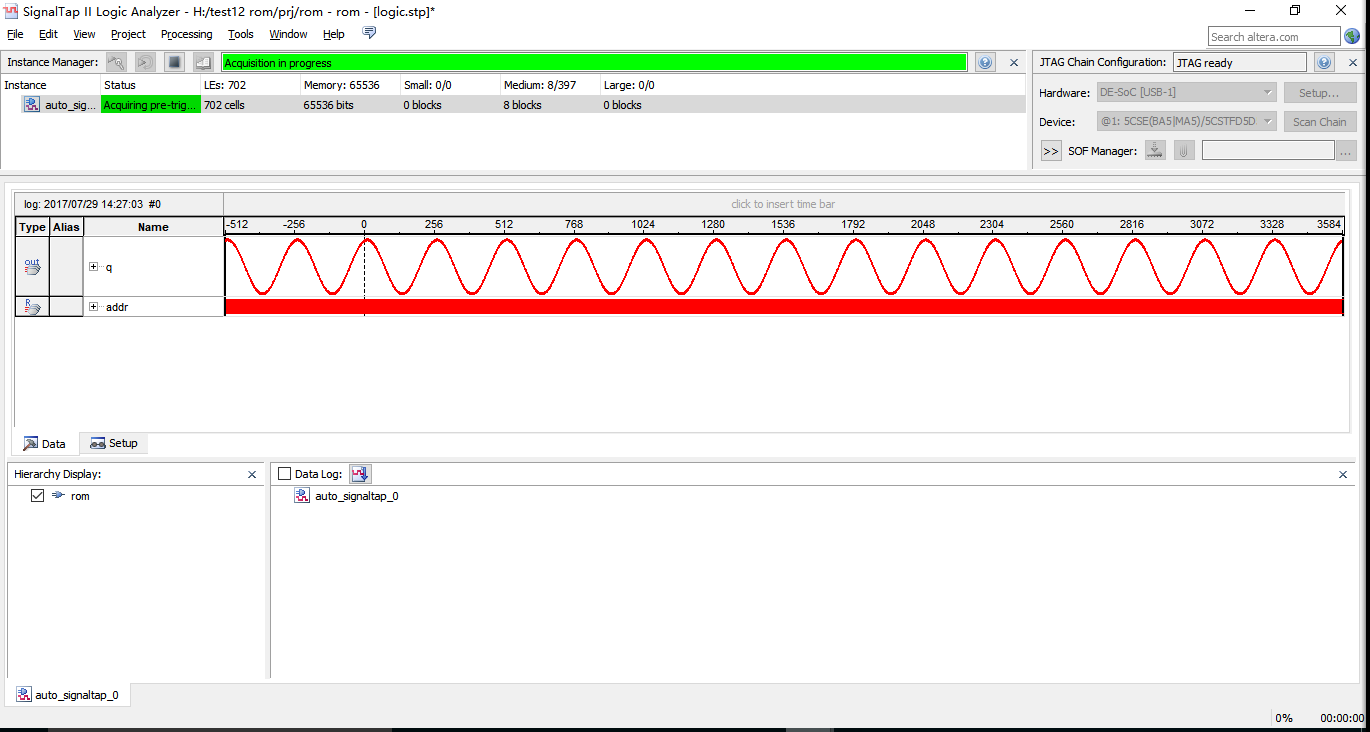

即可看到成功显示的正弦波波形了

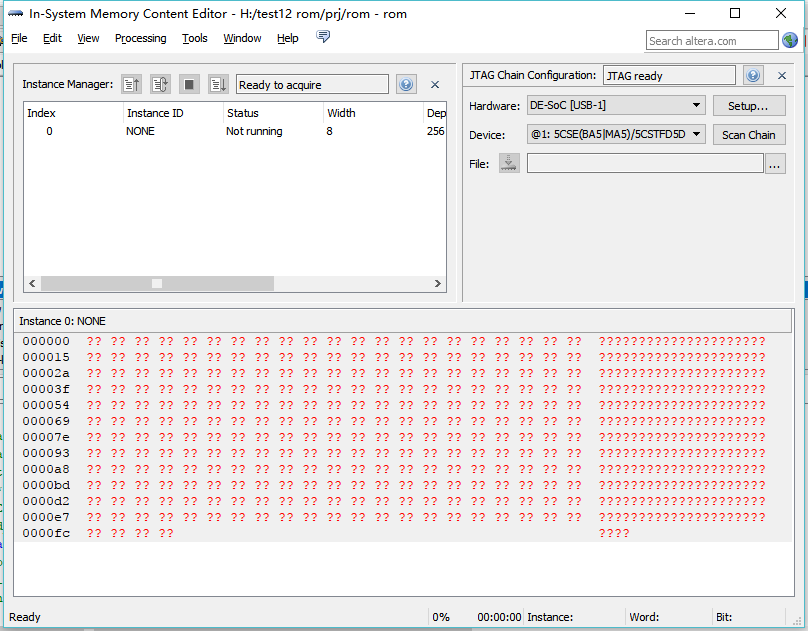

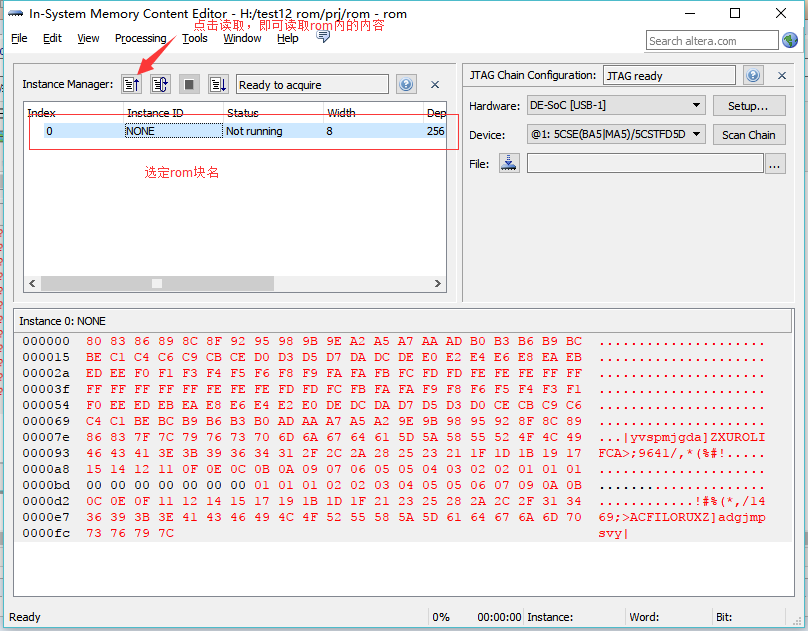

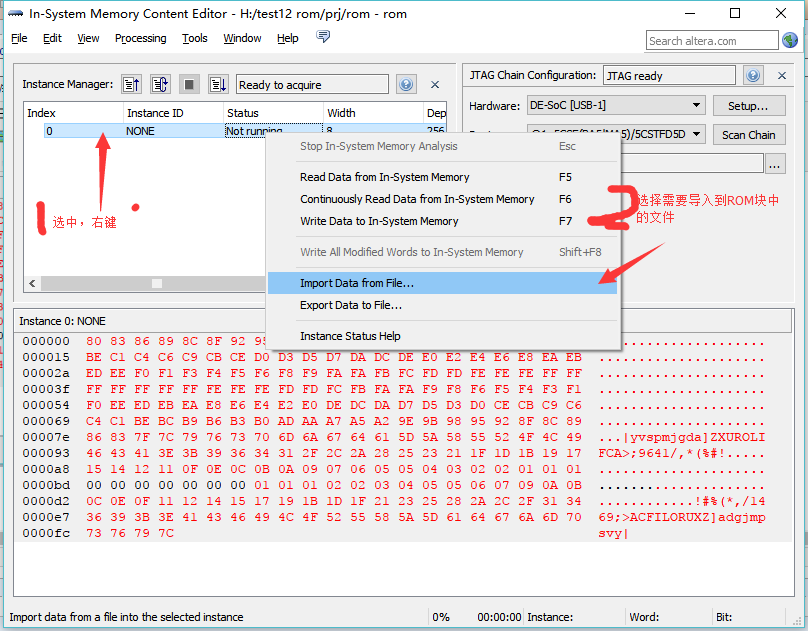

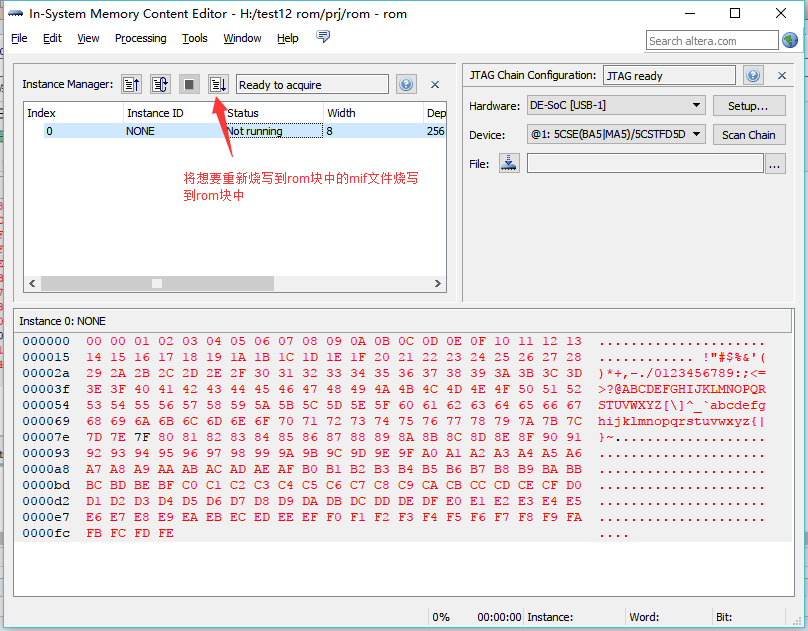

下面通过in system memory content editor 工具对rom 内容进行更改

可以看到signalTap II logic analyzer中显示的波形变为了锯齿波了。

至此,整个设计就完成了

嵌入式ROM核的调用的更多相关文章

- 嵌入式FIFO核的调用

本次设计源码下载地址:http://download.csdn.net/detail/noticeable/9915523 课程目标:学习调用quartus II 软件的FIFO(先进先出)IP核,并 ...

- modelSIM仿真ROM核报错

用Quartus Prime 15.1调用modelSIM进行RTL仿真,modelSIM的transcript框框总是有Failed to Open Readmem File提示. 错误原因:IP核 ...

- 移动工程后,打开ROM核无配置信息

问题: 从他人处下载的ISE工程,打开dw51的ROM IP核,无配置信息,为block memory generator的初始配置,并显示无法找到coe文件 原因:ROM配置过程中的部分内容丢失导致 ...

- FPGA分频与倍频的简单总结(涉及自己设计,调用时钟IP核,调用MMCM原语模块)

原理介绍 1.分频 FPGA设计中时钟分频是重要的基础知识,对于分频通常是利用计数器来实现想要的时钟频率,由此可知分频后的频率周期更大.一般而言实现偶数系数的分频在程序设计上较为容易,而奇数分频则相对 ...

- FPGA开发随笔汇总

点击标题即可进入相关随笔. DE-SOC开发板VrilogHDL开发相关部分: (本过程需要Verilog HDL 的基本语言基础) 1.FPGA的发展史及FPGA 的基础架构 2.首先看一下友晶DE ...

- 【lattice软核】ROM的使用

=======================>>>>> 一.ROM核调用:==================>>>>> ======== ...

- 基于Vivado调用ROM IP core设计DDS

DDS直接数字式频率合成器(Direct Digital Synthesizer) 下面是使用MATLAB生成正弦波.三角波.方波的代码,直接使用即可. t=:*pi/^:*pi y=0.5*sin ...

- System Generator 生成IP核在Vivado中进行调用

System Generator 生成IP核在Vivado中进行调用 1.首先在Simulink中搭建硬件模型 2.查看仿真结果 3.资源分析与时序分析 4.启动vivado,关联生成的IP核 5.调 ...

- 【小梅哥SOPC学习笔记】Altera SOPC嵌入式系统设计教程

Altera SOPC嵌入式系统设计教程 第1章 概述 SOPC(System On Programmable Chip,可编程的片上系统)是Altera公司提出来的一种灵活.高效的SOC解决方案.它 ...

随机推荐

- Java --Servlet 32个经典问题

Servlet方面 1.说一说Servlet的生命周期? Servlet有良好的生存期的定义,包括加载和实例化.初始化.处理请求以及服务结束.这个生存期由javax.servlet.Servlet接口 ...

- redis-单线程架构

单线程模型: redis中的数据结构并不全是简单的kv,还有list.hash等复杂的结构,这些结构很可能会进行细粒度的操作,比如在很长的列表偶棉添加一个元素,在hash当中或者删除一个对象,这样的一 ...

- [UnityShader基础]04.ColorMask

语法如下: ColorMask RGB | A | 0 | 其他R,G,B,A的组合 ColorMask R,意思是输出颜色中只有R通道会被写入 ColorMask 0,意思是不会输出任何颜色 默认值 ...

- javascript中let和var的区别

let是es6中新增命令,也是用来声明变量的,可能很多小伙伴都像我一样,定义变量的时候都会用var而很少用到let,那么,let和var到底有什么区别呢? let和var的区别体现在作用域上.var的 ...

- 4-29 c语言之栈,队列,双向链表

今天学习了数据结构中栈,队列的知识 相对于单链表来说,栈和队列就是添加的方式不同,队列就相当于排队,先排队的先出来(FIFO),而栈就相当于弹夹,先压进去的子弹后出来(FILO). 首先看一下栈(St ...

- vmware 里MAC 鼠标能移动 无法单击

vmware 里MAC 鼠标能移动 无法单击 移动有效果,能看到鼠标移动的光标,鼠标放到mac的图标上还有提示,就是无法单击. 键盘正常. 重启mac,重启vmware 20次好了,2小时.

- PHPMailer出现SMTP connect() failed.

很可能是端口问题,最好把$mailer->SMTPSecure和$mailer->Port分别设置为ssl与465或者tls与587,否则某些浏览器不接受不安全的链接,导致$mailer- ...

- 总结http状态码和200,304状态码

状态码 响应类别 中文意思 1XX 信息性状态码(Informational) 服务器正在处理请求 2XX 成功状态码(Success) 请求已正常处理完毕 3XX 重定向状态码(Redirec ...

- python 装饰器的理解以及类装饰器

python装饰器的作用就是在不改变原有函数结构的情况下给该函数增加一个新功能,就是不入侵到原来函数里面修改代码给其增加一个新功能 先看代码 def out(fn): def inner(*args, ...

- java.lang.String (JDK1.8)

String类实现了java.io.Serializable, Comparable<String>, CharSequence这三个interface. 看了下这三个interface中 ...