Verilog HDL门级建模

Verilog HDL内部定义了12个基本门级元件可以直接用,用这些门级原件直接对逻辑图进行描述,称为门级建模。

每个门输入可能是逻辑0,逻辑1,不确定态x和高阻态z四个值之一。

1.多输入门

主要有与门(and),与非门(nand),或门(or),或非门(nor),异或门(xor),同或门(xnor)。

符号都知道,为了省事我选择直接拍照。

相比于之前,就加了一个高阻态和不确定态,除了正常用法,其他输出的值都是x,多输入门不可能输出z。

在verilog中,一般引用格式为:

Gate_name <instance> (OutputA, Input1, Input2, ..., InputN);

输出在前,输入在后,instance是我们自己命名的实例引用名字,可以省略。

举例:

and U1(out, in1, in2);

xnor (out, in1, in2, in3, in4); //省略instance

2.多输出门

主要有缓冲器(buf),反相器(非门,not)。

还是输出在前,输入在后。图和真值表如下:

举例:

buf B1(out1, out2, ..., in);

not (out1, out2, ..., in) //省略instance

3.三态门

输出为低电平0,高电平1,高阻态z,所以叫三态门。verilog中有四个元件模型,分别是bufif1,bufif0,notif1,notif0。图、功能、真值表分别如下:

4.门级建模举例

一个2线-4线译码器,功能和真值表如下:

(1)verilog HDL门级代码Decoder2x4_gates.v

module Decoder2x4_gates(

input [1:0]A,

input En,

output [3:0]Y);

wire A1not, A0not; //声明电路内部节点

not (A0not, A[0]);

not (A1not, A[1]);

nand U0(Y[0], En, A0not, A1not),

U1(Y[1], En, A[0], A1not),

U2(Y[2], En, A0not, A[1]),

U3(Y[3], En, A[0], A[1]);

endmodule

(2)激励文件Test_Decoder2x4.v

`include "Decoder2x4_gates.v"

`timescale 1us/1us

module Test_Decoder2x4;

reg En;

reg [1:0] A;

wire [3:0] Y;

Decoder2x4_gates U0(A, En, Y);

initial begin

En = 1'b0; A = 2'b10;

#4 En = 1'b1;

end

always begin

#2 A = A + 1'b1;

end

initial begin

//变化一次monitor执行一次

$monitor($time, ":A[2]A[1]A[0]=%b%b%b\ten=%b\tY[2][1][0]=%b%b%b\t\ttest=%d", A[2], A[1], A[0], En, Y[2], Y[1], Y[0], 4'sd9);

$dumpfile("Decoder2x4.vcd");

$dumpvars;

#15 $finish;

end

endmodule

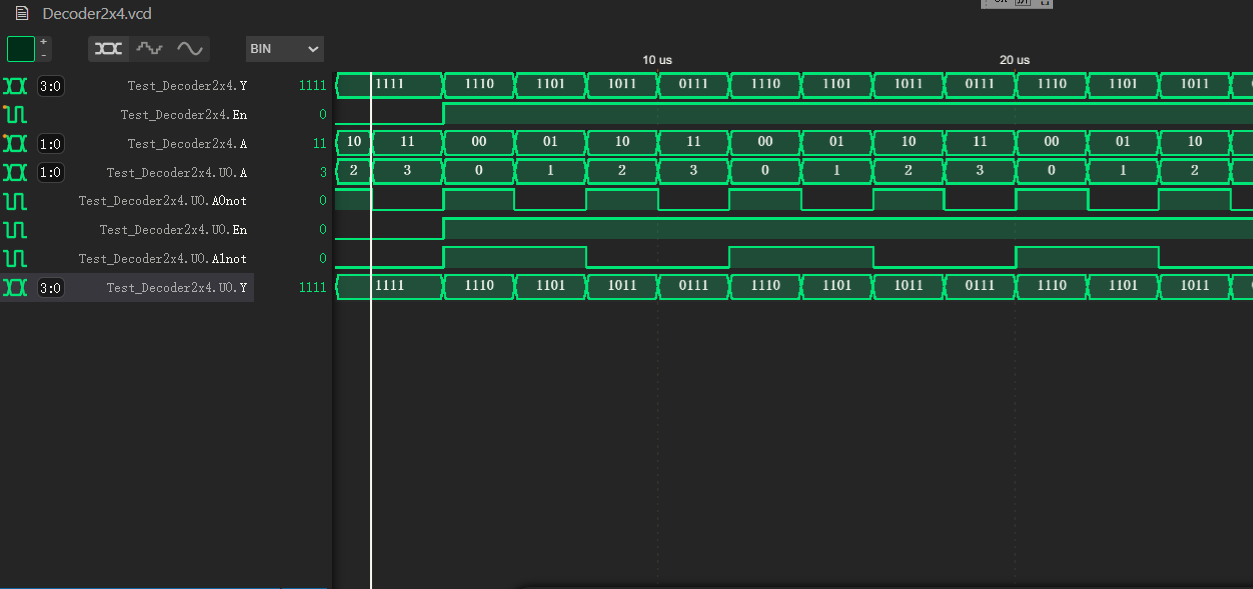

(3)我用$dumpfile生成了Decode2x4.vcd文件,直接使用vscode的WaveTrace插件打开即可,嘎嘎好用啊。

Verilog HDL门级建模的更多相关文章

- Verilog门级建模

门级建模就是将逻辑电路图用HDL规定的文本语言表示出来,即调用Verilog语言中内置的基本门级元件描述逻辑图中的元件以及元件之间的连接关系. Verilog语言内置了12个基本门级元件模型,如下表所 ...

- 【转】Verilog HDL常用建模方式——《Verilog与数字ASIC设计基础》读书笔记(四)

Verilog HDL常用建模方式——<Verilog与数字ASIC设计基础>读书笔记(四) Verilog HDL的基本功能之一是描述可综合的硬件逻辑电路.所谓综合(Synthesis) ...

- 【黑金教程笔记之003】【建模篇】akuei2的Verilog hdl心路

Verilog hdl不是“编程”是“建模” Verilog hdl语言是一种富有“形状”的语言. 如果着手以“建模”去理解Verilog hdl语言,以“形状”去完成Verilog hdl语言的设计 ...

- Verilog HDL的程序结构及其描述

这篇博文是写给要入门Verilog HDL及其初学者的,也算是我对Verilog HDL学习的一个总结,主要是Verilog HDL的程序结构及其描述,如果有错,欢迎评论指出. 一.Verilog ...

- 自己动手写处理器之第二阶段(2)——Verilog HDL简单介绍

将陆续上传本人写的新书<自己动手写处理器>(尚未出版),今天是第六篇.我尽量每周四篇 2.3 Verilog HDL简单介绍 本书实现的OpenMIPS处理器是使用Verilog HDL编 ...

- Verilog HDL设计规范及经验谈(转载)

1. 规范很重要 工作过的朋友肯定知道,公司里是很强调规范的,特别是对于大的设计(无论软件还是硬件),不按照规范走几乎是不可实现的.逻辑设计也是这样:如果不按规范做的话,过一个月后调试时发现 ...

- Verilog HDL实用教程笔记

Verilog HDL实用教程笔记 DRC - Design Rule Check 几何规则检查ERC - Electrical Rule Check 电学规则检查自动参数提取LVS - Logic ...

- No.1 Verilog HDL简介

硬件描述语言HDL(Hardware Description Language)是一种用形式化方法来描述数字电路和系统的语言.设计者利用HDL可以从抽象到具体逐层描述自己的设计思想,用一系列的分 ...

- Verilog HDL模型的不同抽象级别

所谓不同的抽象类别,实际上是指同一个物理电路,可以在不同层次上用Verilog语言来描述.如果只从行为功能的角度来描述某一电路模块,就称作行为模块.如果从电路结构的角度来描述该电路模块,就称作结构模块 ...

- Gate level Simulation(门级仿真)

1 什么是后仿真? 后仿真也成为时序仿真,门级仿真,在芯片布局布线后将时序文件SDF反标到网标文件上,针对带有时序信息的网标仿真称为后仿真. 2 后仿真是用来干嘛的? 检查电路中的timing vio ...

随机推荐

- .Net Web API 005 Controller上传小文件

1.附属文件对象定义 一般情况下,系统里面的文件都会附属一个对象存在,例如用户的头像文件,会附属用户对象存在.邮件中的文件会附属邮件存在.所以在系统里面,我们会创建一个附属文件对象,命名为Attach ...

- [selenium]点击元素出现的obscure问题

前言 我们一般使用如下方式点击元素: elem = driver.find_element(...) elem.click() # 或者使用带等待条件的方式 elem = WebDriverWait( ...

- [PWN之路]堆攻击那些事儿

原文:https://www.freebuf.com/articles/endpoint/371095.html 0x00 前言 根据某大佬所说,pwn之路分为栈,堆,和内核.当前,如果你看到这个文章 ...

- MIT6.s081/6.828 lectrue5/6:System call entry/exit 以及 Lab4 心得

这篇博客主要复习 lecture05:GDB calling conentions 和 lecture06:System call entry/exit 的内容,外加 Lab4:traps 的心得 前 ...

- python flask 简单应用开发

转载请注明出处: Flask 是一个基于 Python 的微型 Web 框架,它提供了一组简洁而强大的工具和库,用于构建 Web 应用程序.Flask 的主要作用是帮助开发者快速搭建轻量级的.灵活的 ...

- 手机用户的开源福音「GitHub 热点速览」

不知道多少用安卓机的小伙伴,被开屏广告烦过.相比有些克制的 iOS 机,安卓机是个应用基本上都有开屏广告,少则 3s 多则 10s,本周获得 1k+ star 的 Android-Touch-Help ...

- 图解 LeetCode 算法汇总——链表

本文首发公众号:小码A梦 一般数据主要存储的形式主要有两种,一种是数组,一种是链表.数组是用来存储固定大小的同类型元素,存储在内存中是一片连续的空间.而链表就不同于数组.链表中的元素不是存储在内存中可 ...

- sqoop1.4.7完全支持Hadoop3.x, Hive3.x Hbase2.x

已经修改好 保存至云盘 自己下载 花了时间的,记得关注我... 链接:https://pan.xunlei.com/s/VNe6P6Tm1A9Q-RG5GByN08rdA1# 提取码:5nke 复制这 ...

- Understanding UML in seconds

UML 是一种分析设计语言,也就是一种建模语言. UML结构解析 UML其结构主要包括以下几个部分: 视图(View) 多个图形组成的集合: 图(Diagram) 图的种类有13种图,但常用的也就两种 ...

- Blazor前后端框架Known-V1.2.15

V1.2.15 更新日期 2023-09-17 更新内容 修复角色不启用相关问题 RadioList组件支持平原(Plain)模式 CheckList组件支持平原(Plain)模式 DataGrid组 ...