E203 itcm

E203 itcm是64Kb,所以地址总线为16位,2^16=64Kb, 数据线宽度为64 bits(8 bytes),所以address width是16-3=13bit,ram depth 是2^16/8=2^13。

itcm的基地址默认是0x8000_0000。

在目录e200_opensource/riscv-tools/riscv-tests/isa/generated,这儿有很多生成好的test文件。比如test rv32ui-p-andi

文件rv32ui-p-andi是riscv的可执行elf文件, rv32ui-p-andi.dump是对应的汇编文件,rv32ui-p-andi.verilog是对于的机器码文件,可以在verilog中用下面的代码把要执行的机器码装入itcm中。

//default itcm size is 64Kb, so E203_ITCM_RAM_DP=13

reg [7:0] itcm_mem [0:(`E203_ITCM_RAM_DP*8)-1];

initial begin

$readmemh({testcase, ".verilog"}, itcm_mem); for (i=0;i<(`E203_ITCM_RAM_DP);i=i+1) begin

`ITCM.mem_r[i][00+7:00] = itcm_mem[i*8+0];

`ITCM.mem_r[i][08+7:08] = itcm_mem[i*8+1];

`ITCM.mem_r[i][16+7:16] = itcm_mem[i*8+2];

`ITCM.mem_r[i][24+7:24] = itcm_mem[i*8+3];

`ITCM.mem_r[i][32+7:32] = itcm_mem[i*8+4];

`ITCM.mem_r[i][40+7:40] = itcm_mem[i*8+5];

`ITCM.mem_r[i][48+7:48] = itcm_mem[i*8+6];

`ITCM.mem_r[i][56+7:56] = itcm_mem[i*8+7];

end

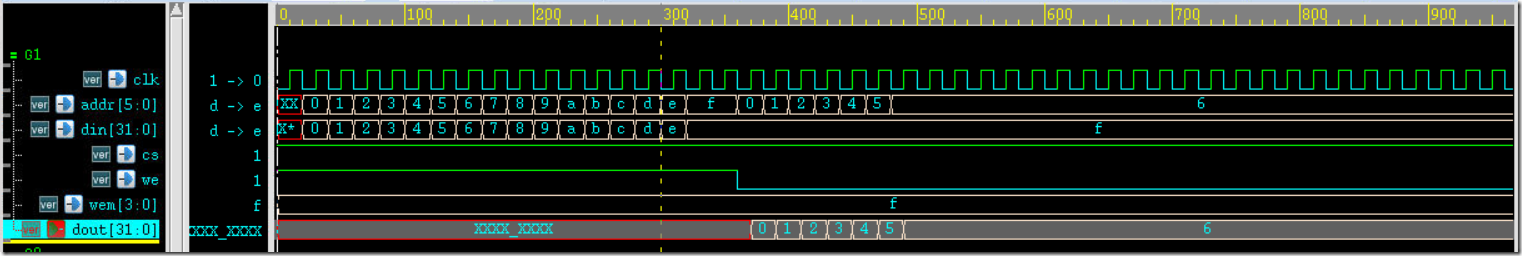

itcm实际上就是一块sram,对itcm的读写如下,读写数据宽度都是按32bit进行的,对于写可以通过write mask只写某个byte。

module sirv_sim_ram

#(parameter DP = 512,

parameter FORCE_X2ZERO = 0,

parameter DW = 32,

parameter MW = 4,

parameter AW = 32

)

(

input clk,

input [DW-1 :0] din,//input data

input [AW-1 :0] addr,//input address

input cs, //chip select

input we, //write enable

input [MW-1:0] wem,//write enable mask

output [DW-1:0] dout //write data out

); reg [DW-1:0] mem_r [0:DP-1];

reg [AW-1:0] addr_r;

wire [MW-1:0] wen;

wire ren; assign ren = cs & (~we);

//it is 4 bits, and every bit mask a byte write

assign wen = ({MW{cs & we}} & wem); genvar i; always @(posedge clk)

begin

if (ren) begin

addr_r <= addr;

end

end generate

for (i = 0; i < MW; i = i+1) begin :mem

if((8*i+8) > DW ) begin: last

always @(posedge clk) begin

if (wen[i]) begin

mem_r[addr][DW-1:8*i] <= din[DW-1:8*i];

end

end

end

else begin: non_last

always @(posedge clk) begin

if (wen[i]) begin

mem_r[addr][8*i+7:8*i] <= din[8*i+7:8*i];

end

end

end

end

endgenerate wire [DW-1:0] dout_pre;

assign dout_pre = mem_r[addr_r]; generate

if(FORCE_X2ZERO == 1) begin: force_x_to_zero

for (i = 0; i < DW; i = i+1) begin:force_x_gen

`ifndef SYNTHESIS//{

assign dout[i] = (dout_pre[i] === 1'bx) ? 1'b0 : dout_pre[i];

`else//}{

assign dout[i] = dout_pre[i];

`endif//}

end

end

else begin:no_force_x_to_zero

assign dout = dout_pre;

end

endgenerate endmodule

testbench文件

module sirv_sim_ram_tb;

reg clk=0;

reg cs=1;

reg we=1;

reg[3:0] wem=4'b1111;

reg[31:0] addr;

reg[31:0] din; wire[31:0] dout;

integer i,j; sirv_sim_ram #(

.FORCE_X2ZERO (1),

.DP (64),

.AW (6),

.MW (4),

.DW (32)

)u_sirv_sim_ram (

.clk (clk),

.din (din),

.addr (addr),

.cs (cs),

.we (we),

.wem (wem),

.dout (dout)

);

always #10 clk = ~clk; initial

begin

for(i=0; i<16; i=i+1)

#20 addr=i;

#20

#20 we = 0;

addr = 0;

#20 addr = 1;

#20 addr = 2;

#20 addr = 3;

#20 addr = 4;

#20 addr = 5;

#20 addr = 6; end initial

begin

for(j=0; j<16; j=j+1)

#20 din=j;

end

initial

begin

//$dumpfile("dump.vcd");

//$dumpvars;

$fsdbDumpfile("dump.fsdb");

$fsdbDumpvars("+all");

end initial

begin

$monitor($time,,,"%d,%d,%d,%d,%d,%d)",cs,din,addr,we,wem,dout);

#1000 $finish;

end

endmodule

E203 itcm的更多相关文章

- E203 CSR rtl实现分析

CSR状态控制寄存器,每个hart都有自己的CSR.对于每个hart,可以配置的状态寄存器是4k.CSR寄存器的功能见:https://www.cnblogs.com/mikewolf2002/p/1 ...

- 蜂鸟E203 IFU模块

E203的IFU(instruction fetch unit)模块主要功能和接口如下: IFU的PC生成单元产生下一条指令的PC. 该PC传输到地址判断和ICB生成单元,就是根据PC值产生相应读指请 ...

- 蜂鸟E203系列——Linux下运行hello world例程

欲观原文,请君移步 创建程序 在 -/hbird-e-sdk-master/software 路径下创建一个"helloworld"中文件夹 在 -/hbird-e-sdk-mas ...

- 蜂鸟E203系列——Linux调试(GDB+Openocd)

欲观原文,请君移步 本文基于文章<蜂鸟E203系列--利用 Hbrid-E-SDK 环境开发程序> GDB 简介 GDB(GNU Project Debugger),是 GNU 工具链中的 ...

- Save ITCM

Debug String if below 64 BYTE it will in DRAM or it will in ITCM So to save ITCM , move it to ALLStr ...

- 童话故事 --- CPU的贴身侍卫ITCM和ICache

"叮铃铃- 叮铃铃-" "谁呀?"黛丝博士打开了家门,"哇,高飞,你怎么来了?" 高飞狗:"好久不见,想来看看你,还买了你最喜欢吃 ...

- 【STM32H7教程】第28章 STM32H7时间关键代码在ITCM执行的超简单方法

完整教程下载地址:http://www.armbbs.cn/forum.php?mod=viewthread&tid=86980 第28章 STM32H7时间关键代码在ITCM执行 ...

- 在vcs中编译及运行测试E203例子

E203的Makefile默认是调用 iverilog编译rtl,我们可以做如下修改,使其支持vcs编译. 1. 首先修改e200_opensource/tb/tb_top.v, 增加dump波形的两 ...

- E203 CSR寄存器

RiscV架构则定义了一些控制和状态寄存器(CSR),用于配置或记录一些运行的状态.CSR寄存器是处理器内核内部的寄存器,使用专有的12位地址编码空间,对一个hart,可以配置4k的CSR寄存器. 蜂 ...

随机推荐

- 一起学Android之音频视频

概述 Android多媒体框架支持各种常见的媒体类型,可以很容易地将音频.视频和图像集成到App中.通过MediaPlayer Api,可以从应用程序资源(RAW).文件系统或网络上数据流资源来播放音 ...

- 为Bootstrap Modal(模态框)全局添加拖拽操作

在js中绑定方法 $(document).on("show.bs.modal", ".modal", function(){ $(this).draggable ...

- CRM第二篇

检索策略 : 相当于优化查询,主要是分为立即加载和延迟加载. 当你查询一个对象的时候,要想立马使用这个对象,或者说是立即查询出来,就使用立即加载. 当你查询这个对象时候不想立马查询出来,而是在使用这个 ...

- NumPy数据的归一化

数据的归一化 首先我们来看看归一化的概念: 数据的标准化(normalization)和归一化 数据的标准化(normalization)是将数据按比例缩放,使之落入一个小的特定区间.在某些比较和评价 ...

- iOS与JS交互-WKWebView

iOS移动端应用中,一般都会嵌入网页,在网页中处理的结果需要反馈给iOS让移动端做出相应的处理(例如页面跳转), 1.webview的配置 2.代理方法中拿到事件进行处理 二.JS中的配套出发事件 当 ...

- MySQL基础之常用函数

数学函数的使用 常用数学函数 函数 作用 函数 作用 ceil() 进一取整 abs() 取绝对值 floor() 舍掉小数部分 power() 幂运算 round() 四舍五入 pi() 圆周率 t ...

- Sql之for update

for updateselect * from xxxxxxx where namemc='筛查' for update那是一种行级锁,一旦用户对某个行施加了行级加锁,则该用户可以查询也可以更新被加锁 ...

- 网络编程之tcp协议以及粘包问题

网络编程tcp协议与socket以及单例的补充 一.单例补充 实现单列的几种方式 #方式一:classmethod # class Singleton: # # __instance = None # ...

- centos python3 的 卸载 删除

卸载/删除python 3.4看到网上说慎用 apt-get remove和 yum remove ,因此不敢用此类命令用卸载了(以后阿里云服务器快过期不用了的时候可以试一下,看看系统是否会崩,哈哈) ...

- 11.web5

先补充点小知识: 关于jjencode 和 aaencode(颜文字) 1.什么是jjencode? 将JS代码转换成只有符号的字符串 2.什么是aaencode? 将JS代码转换成常用的网络表情 ...