Verilog HDL学习_1:分频器/PWM的实现

(一)参考学习资料

(二)实际操作

1. 相关变量计算:

|

First Initial |

Second Initial |

|||

|

Upper case |

H |

X |

||

|

ASCII (Dec) |

72 |

88 |

||

|

Lengths of the pulse |

||||

|

Mu |

Mu_1 |

2.5*105 |

Mu_2 |

2.5*105 |

|

k : mu |

ku_1 : mu_1 |

1.2812:3.7188 |

ku_2 : mu_2 |

1.3438:3.6562 |

|

nu |

nu_1 |

18 |

nu_2 |

18 |

|

Ku |

Ku_1 |

64060 |

Ku_2 |

67190 |

|

Lower case |

h |

x |

||

|

ASCII (Dec) |

104 |

120 |

||

|

Lengths of the pulse |

||||

|

Ml |

Ml_1 |

2.5*105 |

Ml_2 |

2.5*105 |

|

k : ml |

kl_1 : ml_1 |

1.4063:3.5937 |

k : ml_2 |

1.4688:3.5312 |

|

nl |

nl_1 |

18 |

nl_2 |

18 |

|

Kl |

Kl_1 |

70315 |

Kl_2 |

73440 |

2. 第一版:

module Assignment2(rst, CP, Z);

input CP;

input rst; //1 for upper & 0 for lower reg turn = ;

reg [:] cyc = ; //use for the number of cycles //constant parameters

parameter k = , n = , K = ;

parameter KK = K-; //take parameters according to rst input

reg [:] M;

reg [:] MM;

reg [:] m;

//output of the lautch

output Z;

reg Z; //parameters of upper case

parameter [:] Mu [:] = {, };

parameter [:] mu [:] = {, };

//parameter Ku_1 = k*Mu_1/(k+mu_1);

parameter [:] MMu [:] = {, };

//Parameter []KKu_1 = Ku_1-1; //parameters of lower case

parameter [:] Ml [:] = {, };

parameter [:] ml [:] = {, };

parameter [:] MMl [:] = {, }; //Check rst to determine upper or lower.

//check the number of turn to determine the first two or the second.

always@(posedge CP)

begin

if(rst)

begin

M <= turn ? Mu[]:Mu[];

m <= turn ? mu[]:mu[];

MM <= turn ? MMu[]:MMu[];

end

else if(!rst)

begin

M <= turn ? Ml[]:Ml[];

m <= turn ? ml[]:ml[];

MM <= turn ? MMl[]:MMl[];

end

end //Latch

reg [n-:] Q = ;

wire ld, cz;

assign ld = Q>=MM;

assign cz = (Q<KK)|ld; always@(posedge CP)

begin

{Q,Z} <= {ld?:Q+, cz};

cyc = ld ? cyc+ : cyc; if(cyc == )

begin

turn <= ;

cyc <= ;

end

else begin

turn <= ;

end

end endmodule

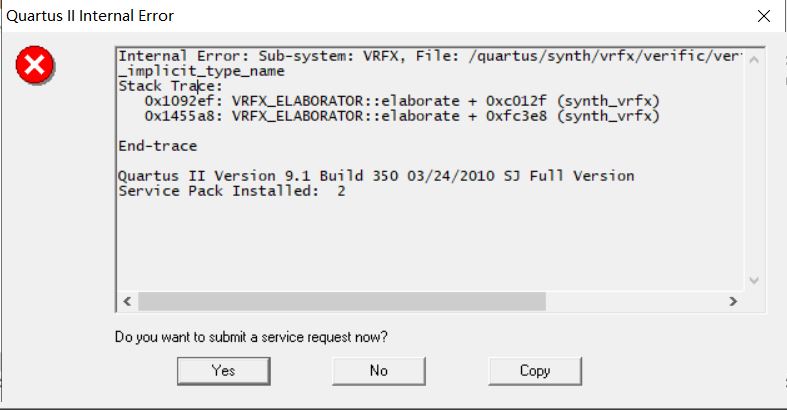

- 出现问题1:

解决方案:将如下部分的变量类型由reg改为了input,系统没有再次崩溃。

//take parameters according to rst input

reg [:] M;

reg [:] MM;

reg [:] m;

//output of the lautch

output Z;

reg Z;

原因:不明

补充:reg变量不可按位赋值,在二维数组中的赋值应为下图第一种方法。

// Correct

M <=Mu[]; // Wrong

M <=Mu[][:];

- 出现问题2:vwf文件仿真时,M没有成功赋值

解决方案:修正了对reg宽度的定义。

补充:

1. Verilog中reg类型的宽度是自定义的,若无定义则默认为1bit。reg的宽度影响变量的取值,若赋值超出reg的范围,不会产生Error,reg变量的最大值将被默认为reg宽度。修改变量时应注意该变量的取值范围。

2. reg变量只能存储整数,允许的运算为加减乘除,若要实现浮点数需要以此为基础构建相关专门的模块。

3. 第二版:

module Assignment2(rst, CP, Z, K);

input CP;

input rst; //1 for upper & 0 for lower reg turn = ;

//use to determine whether the first group of pulses or the second one

reg [:] cyc = ;

//use for the number of pulses in one 'turn' ////constant parameters

parameter n = , M = ;

parameter MM = M-; ////take parameters according to rst input

output [n-:] K;

reg [n-:] K = ; ////output of the lautch

output Z;

reg Z; ////parameters of upper case

parameter Ku_1 = ;

parameter Ku_2 = ; ////parameters of lower case

parameter Kl_1 = ;

parameter Kl_2 = ; ////Latch

reg [n-:] Q;

wire ld, cz;

assign ld = Q>=MM;

assign cz = (Q<K-)|ld; always@(posedge CP)

begin

////Check rst to determine upper or lower.

////check the number of turn to determine the first two or the second.

case(rst)

: begin

if(turn)K <= Kl_2;

else if(!turn)K <= Kl_1;

else K <= ;

end

: begin

if(turn)K <= Ku_2;

else if(!turn)K <= Ku_1;

else K <= ;

end

default: K <= ;

endcase ////renew the state and output clock.

{Q,Z} <= {ld?:Q+, cz};

cyc = ld ? cyc+ : cyc; ////1 cyc represent a pulse

////2 cycles cause an increment in turn

////4 cycles for an entire loop

if(cyc == )

begin

turn <= ;

end

else if(cyc== && turn==)

begin

turn <= ;

cyc <= ;

end end endmodule

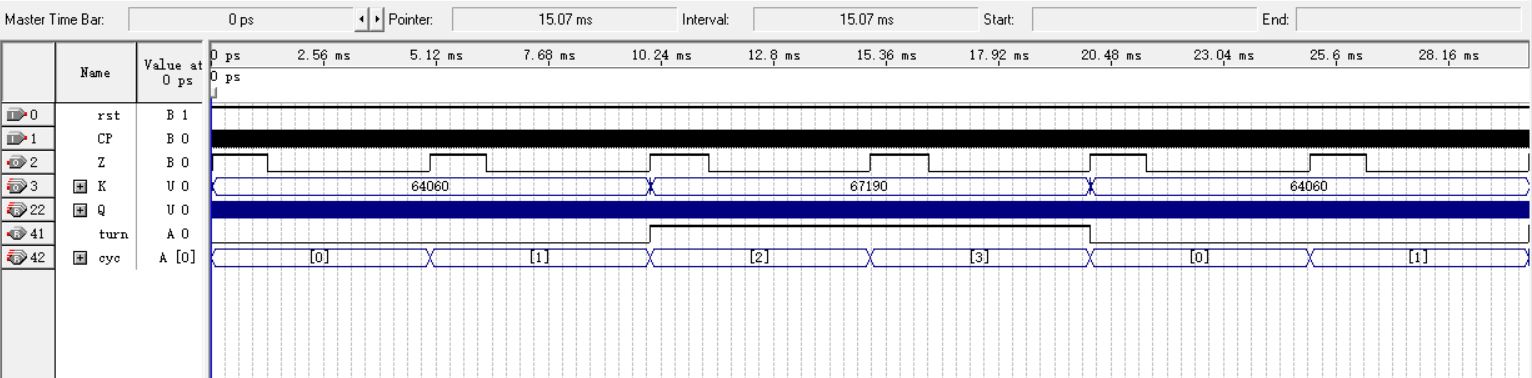

- 仿真结果://K的取值有修改。

- 补充:在Z的第一个输出前有一小段空白期,测量为微秒级,第一个输出仍为5ms。感觉应该不影响时钟的使用,但没有经过硬件检测。

Verilog HDL学习_1:分频器/PWM的实现的更多相关文章

- Verilog HDL的程序结构及其描述

这篇博文是写给要入门Verilog HDL及其初学者的,也算是我对Verilog HDL学习的一个总结,主要是Verilog HDL的程序结构及其描述,如果有错,欢迎评论指出. 一.Verilog ...

- Verilog HDL基础语法讲解之模块代码基本结构

Verilog HDL基础语法讲解之模块代码基本结构 本章主要讲解Verilog基础语法的内容,文章以一个最简单的例子"二选一多路器"来引入一个最简单的Verilog设计文件的 ...

- 基于Verilog HDL整数乘法器设计与仿真验证

基于Verilog HDL整数乘法器设计与仿真验证 1.预备知识 整数分为短整数,中整数,长整数,本文只涉及到短整数.短整数:占用一个字节空间,8位,其中最高位为符号位(最高位为1表示为负数,最高位为 ...

- 浅谈Verilog HDL代码编写风格

消失了好久,没有写文章,也没有做笔记,因为最近再赶一个比赛,时间很紧,昨天周六终于结束了,所以趁着周末这会儿有时间,写点东西,记录下来.首先我学习FPGA才一年多,我知道自己没有资格谈论一些比较深层次 ...

- 如何高效的编写Verilog HDL——进阶版

博主之前写过一篇文章来谈论如何高效的编写Verlog HDL——菜鸟版,在其中主要强调了使用Notepad++来编写Verilog HDL语言的便捷性,为什么说是菜鸟版呢,因为对于新手来说,在还没有熟 ...

- verilog HDL -模块代码基本结构

1--verilog HDL 语言的预编译指令作用:指示在编译verliog HDL源代码前,需要执行哪些操作. 2--模块内容是嵌在module 和endmodule两个语句之间.每个模块实现特定的 ...

- Verilog HDL 使用规范(一)

本博文参考:<大规模逻辑设计指导书>,对于写出规范的代码,培养良好的代码风格颇有裨益. wire and register 一个reg变量只能在一个always语句中赋值: 这个说明至关重 ...

- 关于初次使用Verilog HDL语言需要懂的基本语法

关于初次使用Verilog HDL语言需要懂的基本语法 1.常量 数字表达式全面的描述方式为:<位宽><进制><数字> 8’b10101100,表示位宽为8的二进制 ...

- FPGA Verilog HDL 系列实例--------步进电机驱动控制

[连载] FPGA Verilog HDL 系列实例 Verilog HDL 之 步进电机驱动控制 步进电机的用途还是非常广泛的,目前打印机,绘图仪,机器人等等设备都以步进电机为动力核心.那么,下面我 ...

随机推荐

- ubuntu系统下载后的.deb软件安装命令

查看某个软件是否安装,比如查看QQ软件是否安装并列出软件包名: dpkg -l | grep qq 删除某款软件:sudo dpkg -r 软件包名 安装软件 : sudo dpkg -i *.deb

- Oracle设置序列方法

create sequence SEQ_LoanApplicantGuarantee minvalue 1 nomaxvalue start with 1 increment by 1 nocycle ...

- 机器学习- Sklearn (交叉验证和Pipeline)

前面一节咱们已经介绍了决策树的原理已经在sklearn中的应用.那么这里还有两个数据处理和sklearn应用中的小知识点咱们还没有讲,但是在实践中却会经常要用到的,那就是交叉验证cross_valid ...

- Ceph 之RGW Cache

Overview 缓存是为达到系统快速响应的一项关键技术,Ceph 作为一个复杂的分布式存储系统,有多种.多级缓存存在.缓存按照位置分为: 客户端缓存 服务端缓存 网络中缓存 按照部署方式分为: 单体 ...

- UML--->用例图梳理

用例图梳理 概述 用例图主要用来描述"用户.需求.系统功能单元"之间的关系.它展示了一个外部用户能够观察到的系统功能模型图. 用例图的主要目的是帮助开发团队以一种可视化的方式理解系 ...

- a标签跳转小程序

随着小程序应用的逐步广泛,与公众号之前的协同运营越来越重要,通过公众号的各个入口为小程序导流.最近在运营中发现,大家对公众号关注后回复.关键词回复,超链接小程序的需求. 首先把小程序绑定 ...

- JMeter入门 | 第一个并发测试

JMeter入门 | 第一个并发测试 背景 近期我们组新来了一些新同事,之前从来没有用过JMeter做个并发测试,于是准备了一系列小教程去指引新同事,本章主要是新人入门体验教程,快速实现第一个接口并发 ...

- centos7.2 部署k8s集群

一.背景 二.使用范围 ♦ 测试环境及实验环境 三.安装前说明 ♦ k8s网络基本概念 ♦ 集群规划图 ♦ 软件版本选取 Name Version Description docker-ce 18. ...

- selenium 多表单切换

frame/iframe表单嵌套页面的应用.WebDrivr只能在一个页面上对元素识别与定位,对于在frame/iframe表单内嵌页面上的元素无法直接定位.这时需要使用 switch_to.fram ...

- 认识Git与GitHub

Git介绍 Git是一个开源的分布式版本控制系统,用以有效.高速的处理从很小到非常大的项目版本管理.相比CVS.SVN等版本控制工具,Git更加优秀,功能也更加强大.但是相对也难学. 使用Git来管理 ...