SciTech-Hardware-SoC/FPGA-ASIC 设计 之 System C: 使用SystemC做 系统建模(硬件+软件) 以及 RTL和C/C++ 的联合仿真验证

SystemC: The language for System-level design, modeling and verification.

SystemC addresses the need for a system design and verification language that,

spans hardware and software. It is a language built in standard C++ by extending the language with the use of class libraries

https://news.eda365.com/tech/pcbsj/120011621071262.html

什么是 ASIC 设计

ASIC 设计是开发复杂电子系统的过程。该系统可制造成特殊用途的半导体设备,通常用于大批量应用或具有严格的功耗、性能和尺寸限制的应用。

ASIC 系统设计人员使用高级语言并通过仿真和可视化来开发和评估算法。在半导体领域,开发产品 是抽象开发 规范的模型,通常用C/C++来实现。

这里,SystemC和C++库提供了很大帮助。它简化了共存的硬件和软件设计的概念化。

再加上实现TLM(事务级模型)间接口连接的TLM传送库,SystemC加速了整个验证过程。

另一个重要方面是对所有不同的抽象架构, SystemC有增强的可移植性, 因此同一配置可以无缝地用于不同抽象级的设计。

TLM(事务级模型)是一种 对数字系统进行建模 的方案:

- 将 模块之间的具体通信 与 功能单元或通信架构的具体实现 分开;

- 把 总线或FIFO这类通信机制 模型化成Channel(信道),用SystemC接口类将这些信道 提供给 模块和部件;

- 这些 信道模型的信令接口功能 将取代 事务请求,这将掩藏具体的深层信息交换。利用基于SystemC/TLM的方法学进行IP开发和FPGA建模, 发布时间:2022-03-11, 标签:总线

随着系统级芯片技术的出现,设计规模越来越大,变得非常复杂,同时上市时间也大幅加速。

因此, 正驱使 设计师开发新的方法学,用于复杂IP(硬件和软件)以及复杂系统的验证, 取代通常用的RTL方法学。

ST公司建立了一个设计流,它从抽象开始,易于将模型写入IP的精密周期或RTL模型中。

当转入低级抽象时,建模变得复杂,故IP验证也复杂。我们的方案适合于这种应用场景,

因为它允许人们在各地相似的环境运行相同的测试平台和测试场景,

因而允许在整个开发周期里高效地复用所有的测试范例和环境。示例目标是设计和实现UWB MAC(媒体访问层)IP。决定用SystemC来实现整个IP。

还开发了抽象级具有不同程度变化的不同架构。所付出的努力比较少,得到的仿真速度很快,

软件的实际编写也可以在设计周期非常早的阶段开始。

该IP的RTL结果被移植到了SPEAr系列的FPGA。

除ARM内核和相应的一系列IP,SPEAr还提供一个可配置逻辑块,这为用户在实现其逻辑功能时提供了无与伦比的灵活性。

从而缩短了上市时间,同样也实现了空前的成本节省。

设计开发方法学

SystemC是用标准C/C++语言实现, 因此

即可以 描述硬件的: 系统设计、建模、仿真、测试、验证,

也可用 实现软件的: 系统软件、SDK、Library、...; 因为有C/C++的特性。

https://www.cl.cam.ac.uk/teaching/0809/SysOnChip/additional/lg2-systemc/SystemC-Tutorial.pdf

http://www.forteds.com/:

https://www.cadence.com/en_US/home/tools/digital-design-and-signoff/synthesis/stratus-high-level-synthesis.html

Stratus High-Level Synthesis:

- Cuts IP development from months to weeks

- Enabling a Faster Path to Verified, High-Quality RTL(Register Transfer Level) Implementations from Abstract SystemC, C, or C++ Models

https://learnsystemc.com/codegen, Your data privacy:

- the auto-generation script runs 100% on the client side, your json contend stays locally, it is NOT uploaded to our server.

- The output SystemC code and text-based UML diagrams are temporary variables only visible locally. They don't exist anywhere in the internet.

Nobody other than you can see those files. - We use PlantUML's server to generate the UML diagrams.

Thus, if you choose to see the diagrams, the wsd files will be submitted to plantuml, and the figures are returned.

If this is concerning to you, you can opt-out the diagram generation, and launch plantuml manually to convert the wsd files into diagrams.

https://learnsystemc.com/basic/concurrency

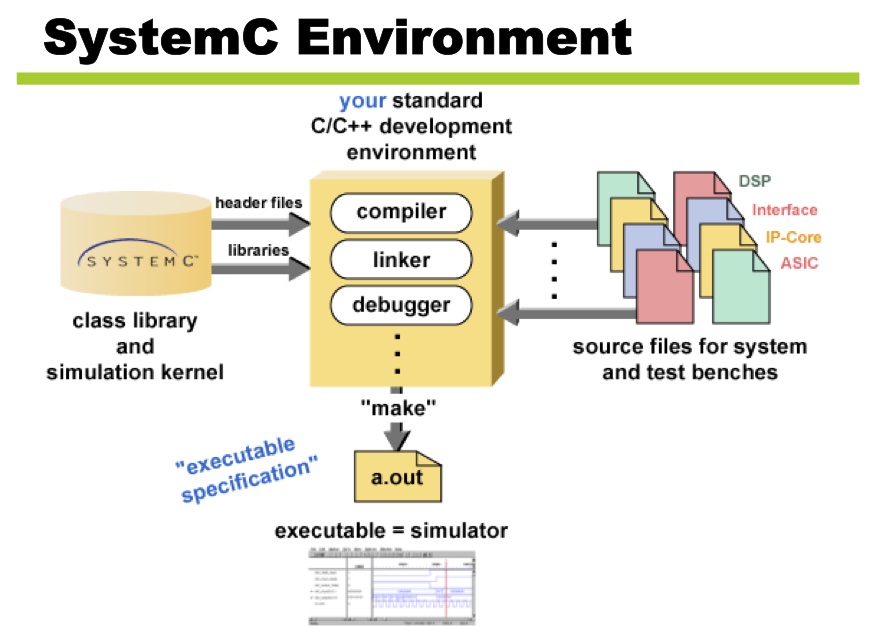

SystemC Environment:

SystemC Methodology:

SystemC

The language for System-level design, modeling and verification

SystemC addresses the need for a system design and verification language that spans hardware and software. It is a language built in standard C++ by extending the language with the use of class libraries. The language is particularly suited to model system's partitioning, to evaluate and verify the assignment of blocks to either hardware or software implementations, and to architect and measure the interactions between and among functional blocks. Leading companies in the intellectual property (IP), electronic design automation (EDA), semiconductor, electronic systems, and embedded software industries currently use SystemC for architectural exploration, to deliver high-performance hardware blocks at various levels of abstraction and to develop virtual platforms for hardware/software co-design. SystemC has been standardized by the Open SystemC Initiative (OSCI) and Accellera Systems Initiative and ratified as IEEE Std 1666-2023.

image

Why SystemC?

An SoC is literally a system on a chip, consisting of both silicon and embedded software. Its design involves complex algorithm and architecture development and analysis similar to that performed in system design – a trade-off process that determines critical metrics, such as SOC performance, functionality, and power consumption.

Consequently, design tools must deliver orders-of-magnitude improvement in productivity at both architectural and implementation (RT and physical) levels. Moreover, tools must support a methodology that enables the early development of embedded application and system software, long before the availability of the RTL design or silicon prototype. Failure to achieve the requisite improvements in design productivity would result in missed market windows, and exploding design costs.

SystemC is a single, unified design and verification language that expresses architectural and other system-level attributes in the form of open-source C++ classes. It enables design and verification at the system level, independent of any detailed hardware and software implementation, as well as enabling co-verification with RTL design. This higher level of abstraction enables considerably faster, more productive architectural trade-off analysis, design, and redesign than is possible at the more detailed RT level. Furthermore, verification of system architecture and other system-level attributes is orders of magnitude faster than that at the pin-accurate, timing-accurate RT level.

The SystemC community consists of a large and growing number of system design companies, semiconductor companies, intellectual property providers, and EDA tool vendors who have joined together to support and promote the standard.

SystemC Transaction Level Modeling (TLM)

The Transaction Level Modeling standard defines interfaces for SystemC, providing an essential framework for model exchange within companies and across the IP supply chain for architecture analysis, software development and performance analysis, and hardware verification. It explicitly addresses virtual prototyping in which SystemC models can easily be exchanged and arranged within a system, enabling the optimal reuse of models and modeling effort across different use cases.

More information about SystemC TLM

SystemC Analog/Mixed-Signal (AMS)

The SystemC AMS standard defined in IEEE Std 1666.1-2016 introduces system-level design and modeling of embedded Analog/Mixed-Signal (AMS) systems. SystemC AMS provides unique capabilities for the design and modeling of embedded analog/mixed-signal applications at higher levels of design abstraction. The SystemC AMS extensions define a uniform and standardized modeling approach that can be used in combination with digitally-oriented ESL design methods, supporting a design refinement methodology for functional modeling, architecture exploration, and virtual prototyping of embedded analog/mixed-signal systems.

More information about SystemC AMS

SystemC Configuration, Control and Inspection (CCI)

The goal of Configuration, Control and Inspection (CCI) is to improve efficiency and return-on-investment for model creators and tool providers. The CCI standards will allow suppliers to instrument models so that a rich user experience is enabled, and they will allow industry tools to leverage this instrumentation to provide powerful debug and analysis capabilities. The CCI working group has released the CCI 1.0 reference implementation to enable model configuration between SystemC models and tools.

More information about SystemC CCI

SystemC Synthesis Subset Standard

The SystemC Synthesis Subset Standard defines the syntactic elements in C++ and SystemC that are appropriate for use in SystemC models intended as input for High Level Synthesis (HLS) tools. The current version of the synthesizable subset is based on ISO/IEC 14882:2003 and IEEE Std 1666-2011, and the SystemC Synthesis Working Group is now looking to incorporate changes and enhancements that result from the evolution towards C++17 and IEEE Std 1666-2023.

More information about the SystemC Synthesis Subset Language Reference Manual

SystemC Verification (UVM-SystemC, SCV)

The UVM-SystemC library provides an implementation of the Universal Verification Methodology (UVM) in SystemC. The UVM-SystemC class library enables the development of scalable and reusable verification collateral for system-level verification and testing.

The SystemC Verification (SCV) library provides a common set of APIs that are used as a basis to verification activities with SystemC (generation of values under constraints, transaction recording, etc.). These APIs are implemented in all major SystemC simulators available on the market.

More information about SystemC Verification

Resources

Download SystemC/TLM standard, IEEE 1666-2023

Download SystemC AMS extensions standard, IEEE 1666.1-2016

SystemC Synthesis Subset Language Reference Manual, version 1.4.7

SystemC/TLM reference implementation on GitHub

SystemC Standards Update, December 2023

SciTech-Hardware-SoC/FPGA-ASIC 设计 之 System C: 使用SystemC做 系统建模(硬件+软件) 以及 RTL和C/C++ 的联合仿真验证的更多相关文章

- EDA技术与ASIC设计和FPGA开发有什么关系?FPGA在ASIC设计中有什么用途?

利用EDA技术进行电子系统设计的最后目标是完成专用集成电路ASIC的设计和实现:FPGA和CPLD是实现这一途径的主流器件.FPGA和CPLD通常也被称为可编程专用IC,或可编程ASIC.FPGA和C ...

- Intel Cyclone SoC FPGA介绍

3.1 Intel Cyclone SoC FPGA介绍 3.1.1 SoC FPGA的基本概念 Intel Cyclone V SoC FPGA是Intel PSG(原Altera)于2013年发布 ...

- FPGA&ASIC基本开发流程

FPGA&数字IC笔面试常考系列 题目:简述ASIC设计流程,并列举出各部分用到的工具. ASIC开发基本流程 芯片架构,考虑芯片定义.工艺.封装 RTL设计,使用Verilog.System ...

- SoC FPGA开发板的FPGA配置数据下载和固化

小梅哥编写,未经许可,严禁用于任何商业用途 2018年7月2日星期一 soc fpga的烧写和固化方式与传统的纯fpga固化方式即存在形式上的相同,也存在细节上的差异,特整理此文. AC501-So ...

- ASIC设计-终极指南

ASIC设计-终极指南 ASIC Design – The Ultimate Guide ASIC设计-终极指南 ASICs代表特定于应用的集成电路,指的是针对特定应用而设计的半导体解决方案,与其他解 ...

- FPGA/CPLD设计思想与技巧

本文讨论的四种常用FPGA/CPLD设计思想与技巧:乒乓操作.串并转换.流水线操作.数据接口同步化,都是FPGA/CPLD逻辑设计的内在规律的体现,合理地采用这些设计思想能在FPGA/CPLD设计工作 ...

- FPGA高级设计——时序分析和收敛(转)

何谓静态时序分析(Static Timing Analysis,简称STA)? 它可以简单的定义为:设计者提出一些特定的时序要求(或者说是添加特定的时序约束),套用特定的时序模型,针对特定的电路进行分 ...

- 深入理解CPU和异构计算芯片GPU/FPGA/ASIC (上篇)

王玉伟,腾讯TEG架构平台部平台开发中心基础研发组资深工程师,专注于为数据中心提供高效的异构加速云解决方案.目前,FPGA已在腾讯海量图片处理以及检测领域已规模上线. 随着互联网用户的快速增长,数据体 ...

- SoC嵌入式软件架构设计

内存是SoC(System on Chip,片上系统)集成设计的重要模块,是SoC中成本比重较大的部分.内存管理的软硬件设计是SoC软件架构设计的重要一环,架构设计师必须要在成本和效率中取得平衡,做到 ...

- 【转载】FPGA算法设计随笔

FPGA设计算法依次需要完成MATLAB浮点仿真 MATLAB定点仿真 verilogHDL定点运算以及数据对比的流程.其中浮点到定点的转换尤为重要,需要在数据表示范围和精度之间做出权衡.另外掌握定点 ...

随机推荐

- ASP.NET Core之由配置系统与创建app所想到的

先看文件配置的代码: ConfigurationBuilder configBuilder=new ConfigurationBuiler();//典型的创建者模式 configBuilder.Add ...

- Error: A JNI error has occurred, please check your installation and try again Exception in thread "main" java.lang.UnsupportedClassVersionError: HelloWorld has been compiled by a more

一个新手容易遇到的问题,电脑上装了多个版本的java,比如8和11,导致javac和java的版本不一样 在控制面板里将其他版本卸载,留个8就行 然后在环境变量里重新配置一下就ok

- pta求符合给定条件的整数集 C语言

题目如下 给定不超过6的正整数A,考虑从A开始的连续4个数字.请输出所有由它们组成的无重复数字的3位数. 输入格式: 输入在一行中给出A. 输出格式: 输出满足条件的的3位数,要求从小到大,每行6个整 ...

- 构建具备推理与反思能力的高级 Prompt:LLM 智能代理设计指南

在构建强大的 AI 系统,尤其是基于大语言模型(LLM)的智能代理(Agent)时,Prompt 设计的质量决定了系统的智能程度.传统 Prompt 通常是简单的问答或填空式指令,而高级任务需要更具结 ...

- CentOS 7 系统调优深度指南

从内核参数.资源分配.存储性能到网络优化,覆盖全维度调优策略,并强调稳定性保障. 一.调优核心维度与操作命令 1. 内核参数调优 (/etc/sysctl.conf) bash # 编辑配置文件 vi ...

- 终极指南:Scrum中如何设置需求优先级

需求众多不知道如何下手?总想先做简单的需求,复杂需求却一拖再拖?那么,我们是时候开始考虑如何设置需求优先级了. 本期终极指南将展示如何为需求设置有效优先级,如何有效管理工作量,让效率指数倍增长,搭配 ...

- 跨平台之 KMP / KMM 详解

任何事情,急于求成都是幼稚的幻想,急于求成的结果一定是不成,对此不应该有任何怀疑. 一. KMP 和 Compose Multiplatform 摘要:减少为不同平台编写和维护相同业务逻辑代码所花费的 ...

- iStore实现 SmartDNS + AdGuard Home IP优选+广告屏蔽

iStore实现 SmartDNS + AdGuard Home IP优选+广告屏蔽 参考自openwrt 官方版 安装配置 AdGuard Home + smartdns 告别广告烦扰 教程 软路由 ...

- 开源公开课丨大数据调度系统Taier任务调度介绍

一.直播介绍 前几期,我们为大家分享了Taier基本介绍.控制台.Web前端架构及数据开发介绍,本期我们为大家分享Taier任务调度介绍. 本次直播我们将从Taier的任务调度实例生成.调度及提交等方 ...

- [abc306h/ex] Balance Scale

Ex - Balance Scale 考虑只有>和<的情况,相当于给每条边定向,当且仅当成环时不合法,那么方案数就是\(DAG\)的方案数 对于=,就是将两个点合并 然后对于一般的求\(n ...