stm32F429启动时钟配置

STM32f429在启动时会在startup_stm32f429_439xx.s中调用static void SetSysClock(void)函数。默认使用的是25M晶振,把系统时钟设置为180M.

在system_stm32f4xx.c中给出了相关的默认时钟参数设置。static void SetSysClock(void)函数执行的就是这个参数设置的过程。

*=============================================================================

* Supported STM32F42xxx/43xxx devices

*-----------------------------------------------------------------------------

* System Clock source | PLL (HSE)

*-----------------------------------------------------------------------------

* SYSCLK(Hz) |

*-----------------------------------------------------------------------------

* HCLK(Hz) |

*-----------------------------------------------------------------------------

* AHB Prescaler |

*-----------------------------------------------------------------------------

* APB1 Prescaler |

*-----------------------------------------------------------------------------

* APB2 Prescaler |

*-----------------------------------------------------------------------------

* HSE Frequency(Hz) |

*-----------------------------------------------------------------------------

* PLL_M |

*-----------------------------------------------------------------------------

* PLL_N |

*-----------------------------------------------------------------------------

* PLL_P |

*-----------------------------------------------------------------------------

* PLL_Q |

*-----------------------------------------------------------------------------

* PLLI2S_N | NA

*-----------------------------------------------------------------------------

* PLLI2S_R | NA

*-----------------------------------------------------------------------------

* I2S input clock | NA

*-----------------------------------------------------------------------------

* VDD(V) | 3.3

*-----------------------------------------------------------------------------

* Main regulator output voltage | Scale1 mode

*-----------------------------------------------------------------------------

* Flash Latency(WS) |

*-----------------------------------------------------------------------------

* Prefetch Buffer | ON

*-----------------------------------------------------------------------------

* Instruction cache | ON

*-----------------------------------------------------------------------------

* Data cache | ON

*-----------------------------------------------------------------------------

* Require 48MHz for USB OTG FS, | Disabled

* SDIO and RNG clock |

*-----------------------------------------------------------------------------

*=============================================================================

假设外部晶振改成了其他的数值比如说8M ,要修改 "stm32f4xx.h " 文件中的 "HSE_VALUE" 宏定义。

如果程序在运行过程中动态修改了PLL倍频系数,或者切换了时钟源,请务必执行一次 SystemCoreClockUpdate()函数,这个函数会自动根据PLL倍频参数计算出实际的主频。

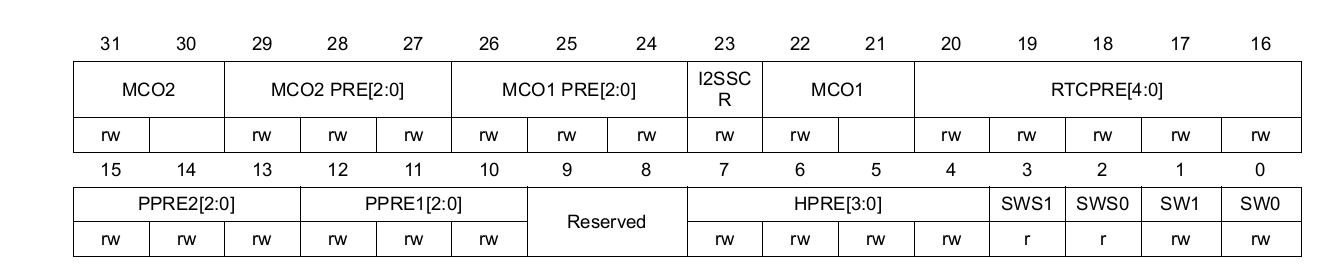

void SystemCoreClockUpdate(void)函数会检测 RCC clock configurat ion register (RCC_CFGR)寄存器的 Bits 3:2 这两位是只读的,由硬件清除和设置,不能软件写入。

Bits 3:2 SWS: System clock switch status

Set and cleared by hardware to indicate which clock source is used as the system clock.

00: HSI oscillator used as the system clock

01: HSE oscillator used as the system clock

10: PLL used as the system clock

11: not applicable

根据这两位通过置swtich语句分析设置源的选择,进一步进行设置,如果是用PLL还要读取RCC_PLLCFGR寄存器的值

获取P N M PLLSRC等参数,来更新系统时钟。系统时钟SYSCLK 有下列公式决定。

PLL_VCO = (HSE_VALUE or HSI_VALUE / PLL_M) * PLL_N

SYSCLK = PLL_VCO / PLL_P

最后获得HCLK frequency :

tmp = AHBPrescTable[((RCC->CFGR & RCC_CFGR_HPRE) >> 4)];

/* HCLK frequency */

SystemCoreClock >>= tmp;

void SystemCoreClockUpdate(void)

{

uint32_t tmp = , pllvco = , pllp = , pllsource = , pllm = ;

#if defined(STM32F446xx)

uint32_t pllr = ;

#endif /* STM32F446xx */

/* Get SYSCLK source -------------------------------------------------------*/

tmp = RCC->CFGR & RCC_CFGR_SWS; switch (tmp)

{

case 0x00: /* HSI used as system clock source */

SystemCoreClock = HSI_VALUE;

break;

case 0x04: /* HSE used as system clock source */

SystemCoreClock = HSE_VALUE;

break;

case 0x08: /* PLL P used as system clock source */

/* PLL_VCO = (HSE_VALUE or HSI_VALUE / PLL_M) * PLL_N

SYSCLK = PLL_VCO / PLL_P

*/

pllsource = (RCC->PLLCFGR & RCC_PLLCFGR_PLLSRC) >> ;

pllm = RCC->PLLCFGR & RCC_PLLCFGR_PLLM; #if defined(STM32F40_41xxx) || defined(STM32F427_437xx) || defined(STM32F429_439xx) || defined(STM32F401xx) || defined(STM32F446xx) || defined(STM32F469_479xx)

if (pllsource != )

{

/* HSE used as PLL clock source */

pllvco = (HSE_VALUE / pllm) * ((RCC->PLLCFGR & RCC_PLLCFGR_PLLN) >> );

}

else

{

/* HSI used as PLL clock source */

pllvco = (HSI_VALUE / pllm) * ((RCC->PLLCFGR & RCC_PLLCFGR_PLLN) >> );

}

#elif defined(STM32F410xx) || defined(STM32F411xE)

#if defined(USE_HSE_BYPASS)

if (pllsource != )

{

/* HSE used as PLL clock source */

pllvco = (HSE_BYPASS_INPUT_FREQUENCY / pllm) * ((RCC->PLLCFGR & RCC_PLLCFGR_PLLN) >> );

}

#else

if (pllsource == )

{

/* HSI used as PLL clock source */

pllvco = (HSI_VALUE / pllm) * ((RCC->PLLCFGR & RCC_PLLCFGR_PLLN) >> );

}

#endif /* USE_HSE_BYPASS */

#endif /* STM32F40_41xxx || STM32F427_437xx || STM32F429_439xx || STM32F401xx || STM32F446xx || STM32F469_479xx */

pllp = (((RCC->PLLCFGR & RCC_PLLCFGR_PLLP) >>) + ) *;

SystemCoreClock = pllvco/pllp;

break;

#if defined(STM32F446xx)

case 0x0C: /* PLL R used as system clock source */

/* PLL_VCO = (HSE_VALUE or HSI_VALUE / PLL_M) * PLL_N

SYSCLK = PLL_VCO / PLL_R

*/

pllsource = (RCC->PLLCFGR & RCC_PLLCFGR_PLLSRC) >> ;

pllm = RCC->PLLCFGR & RCC_PLLCFGR_PLLM;

if (pllsource != )

{

/* HSE used as PLL clock source */

pllvco = (HSE_VALUE / pllm) * ((RCC->PLLCFGR & RCC_PLLCFGR_PLLN) >> );

}

else

{

/* HSI used as PLL clock source */

pllvco = (HSI_VALUE / pllm) * ((RCC->PLLCFGR & RCC_PLLCFGR_PLLN) >> );

} pllr = (((RCC->PLLCFGR & RCC_PLLCFGR_PLLR) >>) + ) *;

SystemCoreClock = pllvco/pllr;

break;

#endif /* STM32F446xx */

default:

SystemCoreClock = HSI_VALUE;

break;

}

/* Compute HCLK frequency --------------------------------------------------*/

/* Get HCLK prescaler */

tmp = AHBPrescTable[((RCC->CFGR & RCC_CFGR_HPRE) >> )];

/* HCLK frequency */

SystemCoreClock >>= tmp;

}

另外也可以自己实现两个设置时钟的函数:

/*

* 使用HSE时,设置系统时钟的步骤

* 1、开启HSE ,并等待 HSE 稳定

* 2、设置 AHB、APB2、APB1的预分频因子

* 3、设置PLL的时钟来源

* 设置VCO输入时钟 分频因子 m

* 设置VCO输出时钟 倍频因子 n

* 设置PLLCLK时钟分频因子 p

* 设置OTG FS,SDIO,RNG时钟分频因子 q

* 4、开启PLL,并等待PLL稳定

* 5、把PLLCK切换为系统时钟SYSCLK

* 6、读取时钟切换状态位,确保PLLCLK被选为系统时钟

*/ /*

* m: VCO输入时钟 分频因子,取值2~63

* n: VCO输出时钟 倍频因子,取值192~432

* p: PLLCLK时钟分频因子 ,取值2,4,6,8

* q: OTG FS,SDIO,RNG时钟分频因子,取值4~15

* 函数调用举例,使用HSE设置时钟

* SYSCLK=HCLK=180M,PCLK2=HCLK/2=90M,PCLK1=HCLK/4=45M

* HSE_SetSysClock(25, 360, 2, 7);

* HSE作为时钟来源,经过PLL倍频作为系统时钟,这是通常的做法 * 系统时钟超频到216M爽一下

* HSE_SetSysClock(25, 432, 2, 9);

*/

void HSE_SetSysClock(uint32_t m, uint32_t n, uint32_t p, uint32_t q)

{

__IO uint32_t HSEStartUpStatus = ; // 使能HSE,开启外部晶振,秉火F429使用 HSE=25M

RCC_HSEConfig(RCC_HSE_ON); // 等待HSE启动稳定

HSEStartUpStatus = RCC_WaitForHSEStartUp(); if (HSEStartUpStatus == SUCCESS)

{

// 调压器电压输出级别配置为1,以便在器件为最大频率

// 工作时使性能和功耗实现平衡

RCC->APB1ENR |= RCC_APB1ENR_PWREN;

PWR->CR |= PWR_CR_VOS; // HCLK = SYSCLK / 1

RCC_HCLKConfig(RCC_SYSCLK_Div1); // PCLK2 = HCLK / 2

RCC_PCLK2Config(RCC_HCLK_Div2); // PCLK1 = HCLK / 4

RCC_PCLK1Config(RCC_HCLK_Div4); // 如果要超频就得在这里下手啦

// 设置PLL来源时钟,设置VCO分频因子m,设置VCO倍频因子n,

// 设置系统时钟分频因子p,设置OTG FS,SDIO,RNG分频因子q

RCC_PLLConfig(RCC_PLLSource_HSE, m, n, p, q); // 使能PLL

RCC_PLLCmd(ENABLE); // 等待 PLL稳定

while (RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET)

{

} /*-----------------------------------------------------*/

//开启 OVER-RIDE模式,以能达到更高频率

PWR->CR |= PWR_CR_ODEN;

while((PWR->CSR & PWR_CSR_ODRDY) == )

{

}

PWR->CR |= PWR_CR_ODSWEN;

while((PWR->CSR & PWR_CSR_ODSWRDY) == )

{

}

// 配置FLASH预取指,指令缓存,数据缓存和等待状态

FLASH->ACR = FLASH_ACR_PRFTEN

| FLASH_ACR_ICEN

| FLASH_ACR_DCEN

| FLASH_ACR_LATENCY_5WS;

/*-----------------------------------------------------*/ // 当PLL稳定之后,把PLL时钟切换为系统时钟SYSCLK

RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK); // 读取时钟切换状态位,确保PLLCLK被选为系统时钟

while (RCC_GetSYSCLKSource() != 0x08)

{

}

}

else

{ // HSE启动出错处理 while ()

{

}

}

} /*

* 使用HSI时,设置系统时钟的步骤

* 1、开启HSI ,并等待 HSI 稳定

* 2、设置 AHB、APB2、APB1的预分频因子

* 3、设置PLL的时钟来源

* 设置VCO输入时钟 分频因子 m

* 设置VCO输出时钟 倍频因子 n

* 设置SYSCLK时钟分频因子 p

* 设置OTG FS,SDIO,RNG时钟分频因子 q

* 4、开启PLL,并等待PLL稳定

* 5、把PLLCK切换为系统时钟SYSCLK

* 6、读取时钟切换状态位,确保PLLCLK被选为系统时钟

*/ /*

* m: VCO输入时钟 分频因子,取值2~63

* n: VCO输出时钟 倍频因子,取值192~432

* p: PLLCLK时钟分频因子 ,取值2,4,6,8

* q: OTG FS,SDIO,RNG时钟分频因子,取值4~15

* 函数调用举例,使用HSI设置时钟

* SYSCLK=HCLK=180M,PCLK2=HCLK/2=90M,PCLK1=HCLK/4=45M

* HSI_SetSysClock(16, 360, 2, 7);

* HSE作为时钟来源,经过PLL倍频作为系统时钟,这是通常的做法 * 系统时钟超频到216M爽一下

* HSI_SetSysClock(16, 432, 2, 9);

*/ void HSI_SetSysClock(uint32_t m, uint32_t n, uint32_t p, uint32_t q)

{

__IO uint32_t HSIStartUpStatus = ; // 把RCC外设初始化成复位状态

RCC_DeInit(); //使能HSI, HSI=16M

RCC_HSICmd(ENABLE); // 等待 HSI 就绪

HSIStartUpStatus = RCC->CR & RCC_CR_HSIRDY; // 只有 HSI就绪之后则继续往下执行

if (HSIStartUpStatus == RCC_CR_HSIRDY)

{

// 调压器电压输出级别配置为1,以便在器件为最大频率

// 工作时使性能和功耗实现平衡

RCC->APB1ENR |= RCC_APB1ENR_PWREN;

PWR->CR |= PWR_CR_VOS; // HCLK = SYSCLK / 1

RCC_HCLKConfig(RCC_SYSCLK_Div1); // PCLK2 = HCLK / 2

RCC_PCLK2Config(RCC_HCLK_Div2); // PCLK1 = HCLK / 4

RCC_PCLK1Config(RCC_HCLK_Div4); // 如果要超频就得在这里下手啦

// 设置PLL来源时钟,设置VCO分频因子m,设置VCO倍频因子n,

// 设置系统时钟分频因子p,设置OTG FS,SDIO,RNG分频因子q

RCC_PLLConfig(RCC_PLLSource_HSI, m, n, p, q); // 使能PLL

RCC_PLLCmd(ENABLE); // 等待 PLL稳定

while (RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET)

{

} /*-----------------------------------------------------*/

//开启 OVER-RIDE模式,以能达到更高频率

PWR->CR |= PWR_CR_ODEN;

while((PWR->CSR & PWR_CSR_ODRDY) == )

{

}

PWR->CR |= PWR_CR_ODSWEN;

while((PWR->CSR & PWR_CSR_ODSWRDY) == )

{

}

// 配置FLASH预取指,指令缓存,数据缓存和等待状态

FLASH->ACR = FLASH_ACR_PRFTEN

| FLASH_ACR_ICEN

|FLASH_ACR_DCEN

|FLASH_ACR_LATENCY_5WS;

/*-----------------------------------------------------*/ // 当PLL稳定之后,把PLL时钟切换为系统时钟SYSCLK

RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK); // 读取时钟切换状态位,确保PLLCLK被选为系统时钟

while (RCC_GetSYSCLKSource() != 0x08)

{

}

}

else

{ // HSI启动出错处理

while ()

{

}

}

}

stm32F429启动时钟配置的更多相关文章

- 痞子衡嵌入式:系统时钟配置不当会导致i.MXRT1xxx系列下OTFAD加密启动失败

大家好,我是痞子衡,是正经搞技术的痞子.今天痞子衡给大家分享的是系统时钟配置不当会导致i.MXRT1xxx系列下OTFAD加密启动失败问题. 我们知道,i.MXRT1xxx家族早期型号(RT1050/ ...

- S3C2440时钟配置

参考: http://blog.csdn.net/mr_raptor/article/details/6555734 http://blog.csdn.net/mjx91282041/article/ ...

- STM32F4_RCC系统时钟配置及描述

Ⅰ.概述 对于系统时钟应该都知道它的作用,就是驱动整个芯片工作的心脏,如果没有了它,就等于人没有了心跳. 对于使用开发板学习的朋友来说,RCC系统时钟这一块知识估计没怎么去配置过,原因在于开发板提供的 ...

- STM32F0xx_RTC实时时钟配置详细过程

Ⅰ.概述 今天总结RTC(Real Time Clock)实时时钟相关的知识,顺带将BKP简单总结一下. STM32的RTC模块和时钟配置系统(RCC_BDCR寄存器)处于后备区域,即在系统复位或从待 ...

- memcached的基本命令(安装、卸载、启动、配置相关)

memcached的基本命令(安装.卸载.启动.配置相关):-p 监听的端口 -l 连接的IP地址, 默认是本机 -d start 启动memcached服务 -d restart 重起memcac ...

- windows下jboss启动、配置、访问

window 下的jboss启动.配置.访问 1.进入jboss\server\default\deploy\jboss-web.deployer 执行run命令 2.jboss访问地址:http:/ ...

- 四轴飞行器1.2.3 STM32F407时钟配置和升级标准库文件

原创文章,欢迎转载,转载请注明出处 这个星期进度比较慢哈,只有周末和晚上下班回来才能做,事件不连续,琐碎的事情又比较多,挺烦的,有多琐碎呢? 1.本人有点小强迫症哈,虽然RTT将文 ...

- stm32时钟配置总结

stm32时钟配置时钟源: 1,HSE(高速外部时钟)即常见的外接8M晶振方案: 2,HSI(高速内部时钟) 即8M内部振荡时钟方案: 3,LSE(低速外部时钟)即常见的32.768Khz晶振方案: ...

- STM32F4系统时钟配置及描述

STM32F4系统时钟配置及描述 stm32f407时钟配置方法(感觉很好,分享一下) STM32F4_RCC系统时钟配置及描述 STM32F4时钟设置分析 stm32f4 - 时钟树分析配置

随机推荐

- flask-数据库 进阶

1. 级联操作 Cascade意为“级联操作”,就是在操作一个对象的同时,对相关的对象也执行某些操作.我们通过一个Post模型和Comment模型来演示级联操作,分别表示文章(帖子)和评论,两者为一对 ...

- springMVC中的ModelAndView说明

ModelAndView 类别就如其名称所示,是代表了Spring Web MVC程式中呈现画面时所使用Model资料物件与View资料物件,由于Java程式中一次只能返回一个物件,所以ModelAn ...

- python3笔记二十四:Mysql数据库操作命令

一:学习内容 Mysql操作命令:启动服务.停止服务.连接数据库.退出数据库.查看版本.显示当前时间.远程连接 数据库操作命令:创建数据库.删除数据库.切换数据库.查看当前选择的数据库 表操作命令:查 ...

- Note 1 for <Pratical Programming : An Introduction to Computer Science Using Python 3>

Book Imformation : <Pratical Programming : An Introduction to Computer Science Using Python 3> ...

- Memcached 在Windows和Linux的安装和使用

Memcached 把经常操作的数据导入到内存中 Memcached是一个高性能的支持分布式的内存存储系统,可以看成一个巨大的hash表.形式:key->value key(唯一键值string ...

- 理解MQ

1.定义 2.消息队列比较 参考文章:https://www.jianshu.com/p/068b8d1610ee

- LC 894. All Possible Full Binary Trees

A full binary tree is a binary tree where each node has exactly 0 or 2 children. Return a list of al ...

- openerp学习笔记 视图中字段只变化(on_change)联动其他字段值、选择和过滤

1.修改产品数量时,自动计算产品销售金额.销售成本和销售利润<field name="num" on_change="on_change_product(produ ...

- (转载)IDEA中对Git的常规操作(合并,提交,新建分支,更新)

工作中多人使用版本控制软件协作开发,常见的应用场景归纳如下: 假设小组中有两个人,组长小张,组员小袁 场景一:小张创建项目并提交到远程Git仓库 场景二:小袁从远程Git仓库上获取项目源码 场景三:小 ...

- Java学习之==>Java8 新特性详解

一.简介 Java 8 已经发布很久了,很多报道表明Java 8 是一次重大的版本升级.Java 8是 Java 自 Java 5(发布于2004年)之后的最重要的版本.这个版本包含语言.编译器.库. ...