DUAL PORT RAM应用实例

作者:桂。

时间:2018-05-14 12:11:00

链接:http://www.cnblogs.com/xingshansi/p/9035522.html

前言

主要是Xilinx 常用模块汇总(verilog)【03】中双端口RAM的细节补充,限于篇幅,单独列出。

一、双端口RAM简述

具体细节参考ug473_7Series_Memory_Resources.pdf.

这里直接调用IP核。

二、IP核参数简述

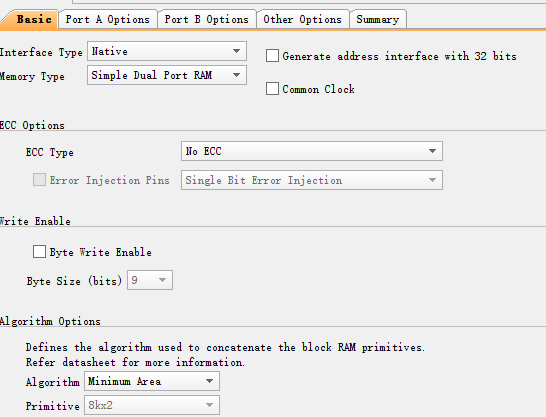

A-Page1

- Common Clock:同源时钟

- Generate adderss..:默认32bit地址,否则根据深度自动调节

- ECC:纠错

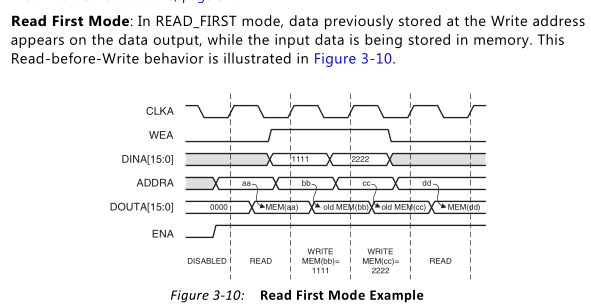

- Read First Operating Mode is supported when the Common Clock option is selected.

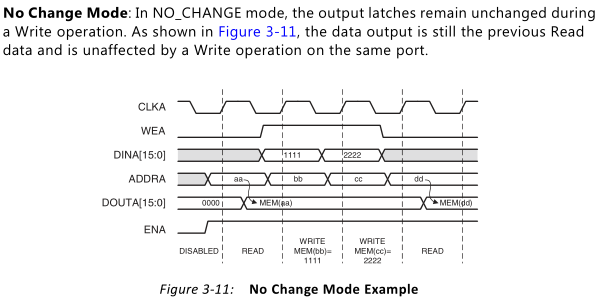

- no change mode

这里使用,通常选择no change mode。

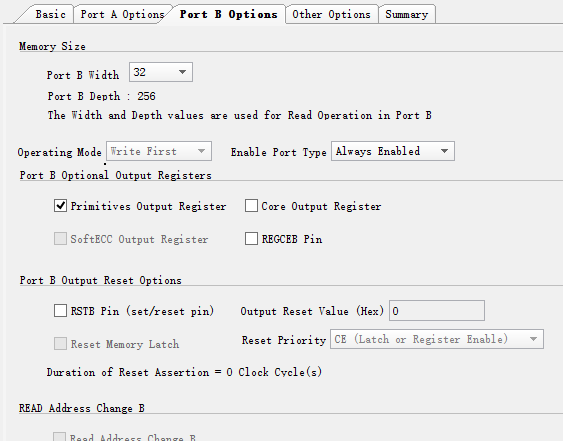

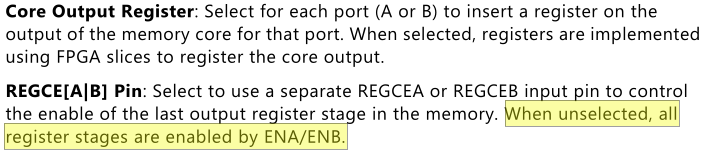

C-Page3

在输出添加一个锁存器,即多延1拍,保证时序良好。

D-Page4

三、仿真验证

任务要求【简化】:

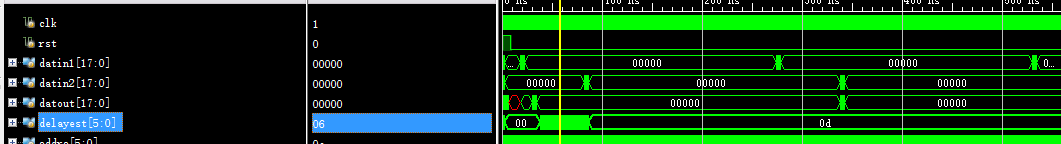

两路周期为64clocks【对应最大延迟数】的数据链,相差delay clocks,现在需要用DUAL PORT RAM进行对齐处理。

思路分析:

1)选1路为参考,一路进入DUAL PORT RAM修正;

2)修正思路:对于脉冲信号,信号高为有效->判断延拍数—>根据延拍数进行地址偏移->输出对齐的数据。

Testbench:

`timescale 1ns / 1ps

/*

Function: DPRAM for data aligned

Author: Gui.

Data: 2018年5月14日12:49:07

*/

module dpram_tb;

//parameter

//parameter datwidth = 18;

parameter delay = ;

parameter start = ;

//port

logic clk,rst;

logic [:] datin1;

logic [:] datin2;

logic [:] datout;

logic [:] addra, addrb, counter, delayest;

logic [:] flag;//FSM

//initial

initial begin

clk = ;

rst = ;

#

rst = ;

#

$stop;

end always # clk = ~clk; always @(posedge clk)

begin

if(rst) begin

datin1 <= ;

datin2 <= ;

counter <= ;

end

else begin

counter <= counter+;

if(counter == start)

begin

datin1 <= {'b1,17'b0};

end

else begin

datin1 <= ;

end

if (counter == (start + delay ))

begin

datin2 <= {'b1,17'b0};

end

else begin

datin2 <= ;

end

end

end //flag control

always @(posedge clk)

begin

if(rst)

begin

delayest <= ;

addra <= ; //for primitive output register

addrb <= ;

flag <= ;

end

else begin

if (flag == 'b00)

begin

if(datout[])

begin

delayest <= ;

flag <= 'b01;

end

end

if (flag == 'b01)

begin

delayest <= delayest + ;

end

if ((flag == 'b01) & datin2[17])

begin

flag <= 'b10;

end

if (flag == 'b10)

begin

addra <= addra + delayest + ;

flag <= 'b11;//next flag state

end

else begin

addra <= addra + ;

end

addrb <= addrb + ;

end

end

//IP

blk_mem_gen_0 uut(

.clka(clk),

.wea('b1),

.addra(addra),

.dina(datin1),

.clkb(clk),

.addrb(addrb),

.doutb(datout)

); endmodule

datout是datin1的修正,可见datin1修正后的结果—>datout 已经与datin2对齐。

DUAL PORT RAM应用实例的更多相关文章

- Xilinx ISE 14.1中模拟True Dual Port RAM例子

<一>创建工程 创建工程在此略过. <二>基本代码 1.创建一个Verilog modual代码如下: module main( input clk, input rsta, ...

- AHB总线RAM Verilog实例

//*************************************************************************** // Copyright(c)2017, L ...

- Xilinx 常用模块汇总(verilog)【03】

作者:桂. 时间:2018-05-10 2018-05-10 21:03:44 链接:http://www.cnblogs.com/xingshansi/p/9021919.html 前言 主要记 ...

- 单双口RAM

// Quartus II Verilog Template// Simple Dual Port RAM with separate read/write addresses and// singl ...

- RAM建模和初始化

冯诺依曼提出的存储计算,计算存储,因此,几乎所有的CPU和ASIC都会使用存储器,它们的类型很多,包括异步RAM.同步RAM.ZBT RAM.DDR DRAM.ROM等.由于大部分的异步RAM和SRA ...

- [RAM] FPGA的学习笔记——RAM

1.RAM——随机存取存储器, 分为SRAM和DRAM. SRAM:存和取得速度快,操作简单.然而,成本高,很难做到很大.FPGA的片内存储器,就是一种SRAM,用来存放程序,以及程序执行过程中,产生 ...

- 单口 RAM、伪双口 RAM、真双口 RAM、单口 ROM、双口 ROM 到底有什么区别呢?

打开 IP Catalog,搜索 Block Memory Generator,即可看到其 Memory Type 可分为 5 中,分别是单口 RAM(Single Port RAM).伪双口 RAM ...

- IP核——RAM

一.Quartus 1.打开Quartus ii,点击Tools---MegaWizard Plug-In Manager 2.弹出创建页面,选择Creat a new custom megafunc ...

- Vivado的helloword计划(一个):硬件project部分

硬件平台:ZedBoard 软件平台:vivado2013.3 本演示样例通过综合.实现,生成比特流,发送到SDK实现. 启动vivado而且创建一个项目 依据提示操作一步步创建新项目的时候记得选择R ...

随机推荐

- PHP 数组中取出随机取出指定数量子值集

#关键:array_rand() 函数返回数组中的随机键名,或者如果您规定函数返回不只一个键名,则返回包含随机键名的数组.#思路:先使用array_rand()随机取出所需数量键名,然后将这些键名指向 ...

- C# 反编译防范

C# 编写的代码通过VS编译器生成 dll 或 exe ,很容易被一些反编译工具查看到源码或对源码进行修改.为防止代码被反编译或被篡改,我们可以进行一定的防范措施.但不能杜绝,因为DotNet编写代码 ...

- 使用js在浏览器中禁止右键、审查元素、复制功能

//禁止右键 document.oncontextmenu = function () { return false } //禁止f12 document.onkeydown = function(e ...

- Linux 输入子系统驱动程序范例

<按键驱动程序> #include <stdio.h> #include <fcntl.h> #include <linux/input.h> #inc ...

- jenkins使用总结

这个教程很全面,可以参考 https://www.jianshu.com/p/dceaa1c7bb49

- 类文件结构-----Class类文件的结构

①无关性的基石 “与平台无关的”得理想最终实现在操作系统的应用层上:Sun公司和其他虚拟机提供商发布了许多可以在各种不同平台上的虚拟机,这些虚拟机都可以载入和执行同一种平台无关的字节码,从而实现了程序 ...

- BZOJ4261 : 建设游乐场

将图黑白染色,每个点拆成两个点,分别表示水平和竖直方向,再增加一个点以控制流量,那么每个格子都需要找两个方向去连接. $S$到每个黑点的控制点连边,流量$2$,费用$0$: 控制点向两个方向的点各连两 ...

- Netbeans异常之cannet locate java installation in specified jdkhome

原因:更改了jdk安装版本 方法:修改netbeans安装目录下ect下netbeans文件, 详细代码位置: # Default location of JDK: # (set by install ...

- c++内存管理的一些资料

C++内存分配方式详解--堆.栈.自由存储区.全局/静态存储区和常量存储区 如何动态调用DLL中的导出类 在dll中导出类,并结合继承带来的问题 如何更好的架构一个界面库,欢迎大家一起讨论 pim ...

- 更改mac系统语言及其软件

如图,把所用语音置顶 https://support.apple.com/zh-cn/HT202036 1.firefox需要下载英文版,同时可以保留中文版,两个不能同时启动.如果你只是为了切换浏览器 ...