【译】x86程序员手册11- 4.1系统寄存器

4.1 Systems Registers 系统寄存器

The registers designed for use by systems programmers fall into these classes:

为系统程序设计的寄存器分为如下几类:

- EFLAGS 标志寄存器FLAGS

- Memory-Management Registers 内存管理寄存器

- Control Registers 控制寄存器

- Debug Registers 调试寄存器

- Test Registers 测试寄存器

4.1.1 Systems Flags 系统标志

The systems flags of the EFLAGS register control I/O, maskable interrupts, debugging, task switching, and enabling of virtual 8086 execution in a protected, multitasking environment. These flags are highlighted in Figure 4-1 .

EFLAGS寄存的系统标志控制着I/O、可屏蔽中断、调试、任务切换和在多任务环境及保护模式下虚拟8086。这些标志见图4-1。

IF (Interrupt-Enable Flag, bit 9) 中断使能标志,位9

Setting IF allows the CPU to recognize external (maskable) interrupt requests. Clearing IF disables these interrupts. IF has no effect on either exceptions or nonmaskable external interrupts . Refer to Chapter 9 for more details about interrupts .

IF置位允许CPU识别外部(可屏蔽的)中断请求。IF不影响异常和不可屏蔽外部中断。更多关于中断的信息见第9章。

NT (Nested Task, bit 14) 嵌套任务,位14

The processor uses the nested task flag to control chaining of interrupted and called tasks. NT influences the operation of the IRET instruction . Refer toChapter 7 and Chapter 9 for more information on nested tasks.

处理器使用嵌套任务标志来控制中断和调用任务链。NT标志影响IRET指令的操作。参考第7章和第9章关于嵌套任务的信息。

RF (Resume Flag, bit 16) 重置标志,位16

The RF flag temporarily disables debug exceptions so that an instruction can be restarted after a debug exception without immediately causing another debug exception . Refer to Chapter 12 for details .

RF标志临时关闭调试异常,这样一条指令可以在一个没有立即引起另一个调试异常的调试异常之后被重新执行。参见第12章。

TF (Trap Flag, bit 8) 陷阱标志,位8

Setting TF puts the processor into single-step mode for debugging. In this mode, the CPU automatically generates an exception after each instruction, allowing a program to be inspected as it executes each instruction. Single-stepping is just one of several debugging features of the 80386 . Refer to Chapter 12 for additional information .

TF置位使处理器进入单步调试模式。在这个模式中,CPU在每和指令执行后自动生成一个异常,允许程序在执行每条指令时被检查。单步特性是80386多个调试特性之一。参见第12章。

VM (Virtual 8086 Mode, bit 17) 虚拟8086模式,位17

When set, the VM flag indicates that the task is executing an 8086 program . Refer to Chapter 14 for a detailed discussion of how the 80386 executes 8086 tasks in a protected, multitasking environment.

当设置该位后,表明任务正在执行一个8086程序。参见第14章。

4.1.2 Memory-Management Registers 内存管理寄存器

Four registers of the 80386 locate the data structures that control segmented memory management:

80386的4个寄存器用来定位控制分段内存管理的数据结构。

GDTR Global Descriptor Table Register 全局描述符表寄存器GDTR

LDTR Local Descriptor Table Register 本地描述符表寄存器LDTR

These registers point to the segment descriptor tables GDT and LDT. Refer to Chapter 5 for an explanation of addressing via descriptor tables.

这两个寄存器指向一个段描述符表GDT和LDT。关于通过描述符寻址的解释参见第5章。

IDTR Interrupt Descriptor Table Register 中断描述符表寄存器IDTR

This register points to a table of entry points for interrupt handlers (the IDT ) . Refer to Chapter 9 for details of the interrupt mechanism .

这个寄存器指向一个中断处理例程(IDT)的入口地址表。关于中断机制参见第9章。

TR Task Register 任务寄存器TR

This register points to the information needed by the processor to define the current task . Refer to Chapter 7 for a description of the multitasking features of the 80386.

这个寄存器指向任务信息,这些信息被处理器用来定义当前任务。关于80386的多任务特性的描述参见第7章。

4.1.3 Control Registers 控制寄存器

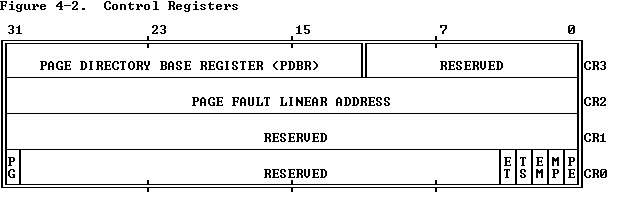

Figure 4-2 shows the format of the 80386 control registers CR0, CR2, and CR3. These registers are accessible to systems programmers only via variants of the MOVinstruction, which allow them to be loaded from or stored in general registers; for example:

图4-2展示了80386的控制寄存器CR0、CR1、CR2、CR3的格式。系统程序仅能通过MOV指令来访问这些寄存器,这就允许他们被存储到通用寄存器中或从其中恢复;如:

MOV EAX, CR0 从CR0中取值到EAX中

MOV CR3, EBX 将EBX中的值放到CR3中

CR0 contains system control flags, which control or indicate conditions that apply to the system as a whole, not to an individual task.

CR0中的系统控制标志,控制或表明一定的条件,这些控制或条件使系统做为一个整体而不是个别任务。

EM (Emulation, bit 2) 虚拟,位2

EM indicates whether coprocessor functions are to be emulated. Refer to Chapter 11 for details .

EM表明协处理器功能是否被模仿。参见第11章。

ET (Extension Type, bit 4) 扩展标志,位4

ET indicates the type of coprocessor present in the system (80287 or 80387 ) . Refer to Chapter 11 and Chapter 10 for details.

ET表明系统中慧在此类型的协处理(80287或80387)。参见第11章和第10章。

MP (Math Present, bit 1) 数学存在,位1

MP controls the function of the WAIT instruction, which is used to coordinate a coprocessor . Refer to Chapter 11 for details .

MP控制在协同协处理器进使用的WAIT指令功能。参见第11章。

PE (Protection Enable, bit 0) 保护模式开户,位0

Setting PE causes the processor to begin executing in protected mode. Resetting PE returns to real-address mode . Refer to Chapter 14 and Chapter 10 for more information on changing processor modes .

PE置位导致处理器开始在保护模式下运行。重置PE返回到实地址模式。参见第14章和第10章关于如何改变处理器模式。

PG (Paging, bit 31) 分页开启,位31

PG indicates whether the processor uses page tables to translate linear addresses into physical addresses . Refer to Chapter 5 for a description of page translation; refer to Chapter 10 for a discussion of how to set PG.

PG表明是否处理器使用页表来转换线性地址到物理地址。参见第5章关于分页转换;参见第10章关于如何设置PG。

TS (Task Switched, bit 3) 任务切换,位3

The processor sets TS with every task switch and tests TS when interpreting coprocessor instructions . Refer to Chapter 11 for details .

每次任务切换处理器都置位TS,并在解释协处理器指令时测试TS标志。参见第11章。

CR2 is used for handling page faults when PG is set. The processor stores in CR2 the linear address that triggers the fault . Refer to Chapter 9 for a description of page-fault handling.

当PG被置位后,CR2来处理页错误。处理器在CR2中保存触发错误的线性地址。参见第9章页错误处理。

CR3 is used when PG is set. CR3 enables the processor to locate the page table directory for the current task . Refer to Chapter 5 for a description of page tables and page translation.

CR3在PG置位后使用。处理器通过CR3来定位当前任务的页目录表。参见第5章关于页表和页转换的描述。

4.1.4 Debug Register 调试寄存器

The debug registers bring advanced debugging abilities to the 80386, including data breakpoints and the ability to set instruction breakpoints without modifying code segments . Refer to Chapter 12 for a complete description of formats and usage.

调试寄存器给80386带来高级的调试能力,包括数据断点、不修改代码段就可以下指令断点。详细的描述和用法参见第12章。

4.1.5 Test Registers 测试寄存器

The test registers are not a standard part of the 80386 architecture. They are provided solely to enable confidence testing of the translation lookaside buffer (TLB), the cache used for storing information from page tables . Chapter 12 explains how to use these registers .

测试寄存器不是标准80386架构的一部分。他们仅能提供对后备缓冲区(TLB)进行信任测试,该缓冲区被用来保存页表信息。第12章解释了如何使用这些寄存器。

【译】x86程序员手册11- 4.1系统寄存器的更多相关文章

- 【译】x86程序员手册01

Intel 80386 Reference Programmer's Manual 80386程序员参考手册 Chapter 1 -- Introduction to the 80386 第1章 - ...

- 【译】x86程序员手册08 -2.6中断和异常

2.6 Interrupts and Exceptions 中断和异常 The 80386 has two mechanisms for interrupting program execution: ...

- 【译】x86程序员手册03 - 2.1内存组织和分段

2.1 Memory Organization and Segmentation 内存组织和分段 The physical memory of an 80386 system is organized ...

- 【译】x86程序员手册00 - 翻译起因

从上一次学习MIT的操作系统课程又过去了一年.上次学习并没有坚持下去.想来虽有种种原因,其还在自身无法坚持罢了.故此次再鼓起勇气重新学习,发现课程都已由2014改版为2016了.但大部分内容并没有改变 ...

- 【译】x86程序员手册38-10.2实在址模式下的软件初始化

10.2 Software Initialization for Real-Address Mode 实地址模式的软件初始化 In real-address mode a few structur ...

- 【译】x86程序员手册35-9.8异常条件

译注:一些异常没有翻译,因为看书时主要为了理解linux代码,所以代码中没有主要使用的就没有仔细看.这部分内容后期再看时再进行翻译. 9.8 Exception Conditions 异常条件 The ...

- 【译】x86程序员手册31- 第9章 异常和中断

Chapter 9 Exceptions and Interrupts 第9章 异常和中断 Interrupts and exceptions are special kinds of control ...

- 【译】x86程序员手册26-7.5任务切换

7.5 Task Switching 任务切换 The 80386 switches execution to another task in any of four cases: 80386在以下四 ...

- 【译】x86程序员手册25-7.1任务状态段

7.1 Task State Segment 任务状态段 All the information the processor needs in order to manage a task is st ...

随机推荐

- Extended symmetrical multiprocessor architecture

An architecture for an extended multiprocessor (XMP) computer system is provided. The XMP computer s ...

- xcode5下取消ARC

打开你的工程,点击目录的工程文件,最顶端蓝色的,然后选择project下你的工程,还是蓝色那项,然后build Settings,然后往下拉,在Apple LLVM 5.0 - Language - ...

- ubuntu 安装 swift

第一步 安装mysql和mysql的python支持 apt-get install python-mysqldb mysql-server 第二步 配置mysql vim /etc/mysql/my ...

- Chrome 如何查看/修改Cookie

- Entity Framework性能影响因素分析

1.对象管理机制-复杂为更好的管理模型对象,EF提供了一套内部管理机制和跟踪对象的状态,保存对象一致性,使用方便,但是性能有所降低. 2.执行机制-高度封装在EF中,所有的查询表达式都会经过语法分析. ...

- PLY格式文件具体解释

链接:http://blog.csdn.net/szchtx/article/details/7587999 http://cdu.net.cn/3D/2014-04-23/705.html 一.PL ...

- vue—你必须知道的 js数据类型 前端学习 CSS 居中 事件委托和this 让js调试更简单—console AMD && CMD 模式识别课程笔记(一) web攻击 web安全之XSS JSONP && CORS css 定位 react小结

vue—你必须知道的 目录 更多总结 猛戳这里 属性与方法 语法 计算属性 特殊属性 vue 样式绑定 vue事件处理器 表单控件绑定 父子组件通信 过渡效果 vue经验总结 javascript ...

- 转 java面试题

● 简述synchronized?Object:Monitor机制: ● 简述happen-before规则 : ● JUC和Object : Monitor机制区别是什么 : 简述AQS原理 : ● ...

- 进销存管理系统, 刚学C++

各位大神们.有什么补充的能够评论一下吗? #include<iostream> #include<string> using namespace std; int G=0;// ...

- 一段shell脚本

//根据入参增加nginx反向代理#!/bin/bash#set -x log_path="./proc/logs/shellExecute.log"log_path_back=& ...