k64 datasheet学习笔记35---Analog-to-Digital Converter (ADC)

0.前言

本文主要介绍K64的ADC部分的特性,内部架构,信号描述及操作接口等

1.简介

1.1.ADC模块特性

- 线性逐次逼近算法,达16bit分辨率

- 达到4对差分和24个单端模拟量输入

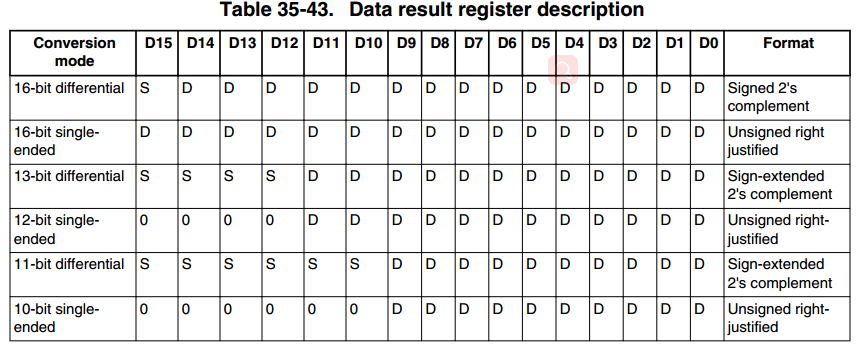

- 输出模式

差分为16bit,13bit,11bit和9bit模式

单端为16bit,12bit,10bit和8bit模式

- 对于差分输出格式为带符号扩展的16bit的2的补码

- 对于单端输出格式为右对齐无符号格式

- 支持单次或连续转换

- 可配置采样时间和转换速率

- 转换完成或硬件平均完成标志和中断

- 有四路输入时钟源可选

- 低功耗模式操作?

- 异步时钟源?

- 带有硬件通道选择的硬件触发器?

- 与设定值比较,可触发中断

- 温度传感器

- 硬件平均

- 可选参考电压:外部或其它

- 自我矫正模式

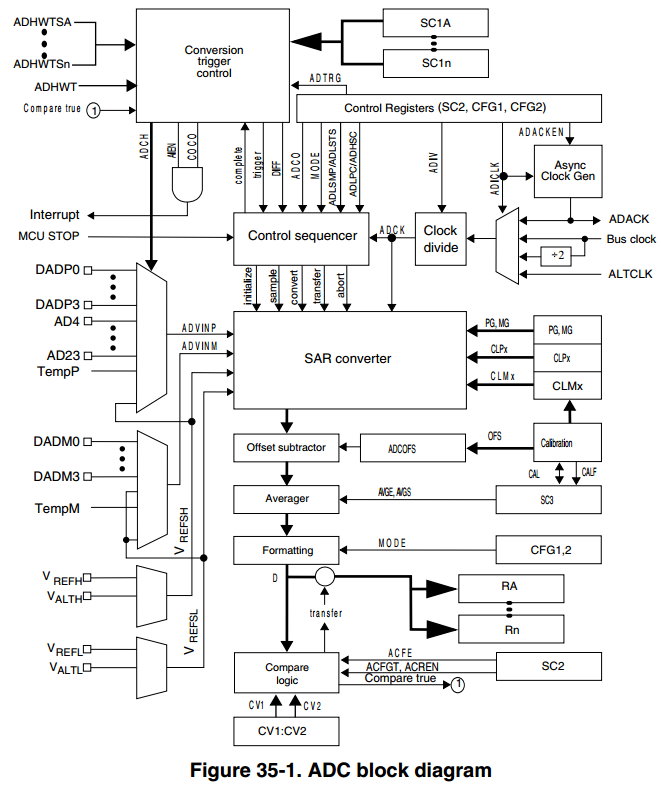

1.2 ADC模块框图

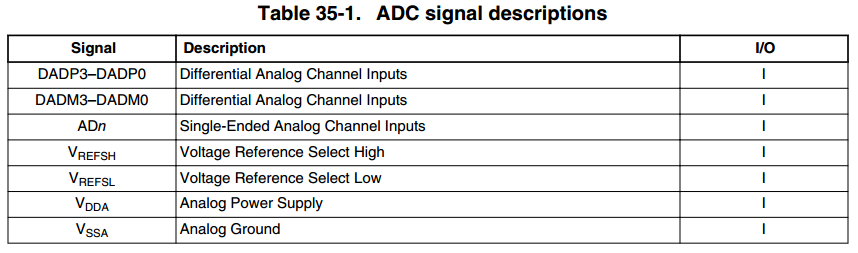

2.ADC信号描述

注:[1]支持4对差分输入和24个单端输入,每个差分需要两个输入:DADPx和DADMx

[2]四个supply/reference/ground连接

[3]采用VDDA作为电源,VSSA作为地

[4]VREFSH和VREFSL 是ADC模块的高和低的参考电压,

VREFSH和VREFSL 可配置为使用external (VREFH and VREFL) 和 alternate (VALTH and VALTL) 两个参考电压对中的一个

[5]SC1n[DIFF] 为0时支持24路单端输入,通过SC1[ADCH] 指定当前转换通道

[6]SC1n[DIFF] 为1支持4路差分输入,通过SC1[ADCH]指定当前转换通道

2.1 Analog power-VDDA

TODO

2.2 Anoalog ground-VSSA

TODO

2.3 参考电压选择

可以有两对正向电压可以选择,每队都包含了VREFSH和VREFSL。

VREFSH电压范围必需在最小的高REF~VDDA,VREFSL必需与VSSA同

两个电压对分别是external (VREFH and VREFL) and alternate (VALTH and VALTL) ,可以通过SC2[REFSEL] 来选择

alternate VALTH and VALTL可以选择外部pin或内部源

有些封装,VREFH连接到VDDA,VREFL连接到VSSA

2.4 Analog 通道输入(ADX)

支持24路单端输入,通过SC1[ADCH] 选择转换通道

2.5 差分Analog通道输入

支持4组差分通道,每组差分输入是一组外部引脚,DADPx and DADMx ,通过SC1[ADCH] 选择转换通道

如果SC1n[DIFF]为低所有的DADPx 可以用作单端输入

3.内存映射与寄存器定义

ADC Status and Control Registers 1 (ADCx_SC1n) :主要设定了差分/单端选择、设置当前转换通道、转换完成中断使能/禁用、读取转换完成标记

ADC Configuration Register 1 (ADCx_CFG1) :选择输入使用源、转换模式选择(转换位数)、采样时间、时钟分频比、低功耗配置

ADC Configuration Register 2 (ADCx_CFG2) :ADC通道选择(a通道/b通道)、异步时钟输出使能、高速转换模式配置、长采样时间选择

ADC Data Result Register (ADCx_Rn) :

Compare Value Registers (ADCx_CVn) :SC2[ACFE]=1 时设定比较值来与转换值进行比较

Status and Control Register 2 (ADCx_SC2) :参考电压选择、DMA使能、比较范围使能、比较大于or小于设定范围、比较使能、转换触发器使能、指示转换是否在进行中

Status and Control Register 3 (ADCx_SC3) :硬件平均数选择、硬件平均使能、连续转换使能、矫正失败标记、开启校准

ADC Offset Correction Register (ADCx_OFS) :offset校准值设置,这个值将从转换值中扣除然后形成转换结果

ADC Plus-Side Gain Register (ADCx_PG) :正端增益矫正因子

ADC Minus-Side Gain Register (ADCx_MG) :负端增益矫正因子

ADC Plus-Side General Calibration Value Register:如果禁用CAL则会采用此处的值做自动矫正

(ADCx_CLPD)

ADC Plus-Side General Calibration Value Register:

(ADCx_CLPS)

ADC Plus-Side General Calibration Value Register:

(ADCx_CLP4)

ADC Plus-Side General Calibration Value Register:

(ADCx_CLP3)

ADC Plus-Side General Calibration Value Register:

(ADCx_CLP2)

ADC Plus-Side General Calibration Value Register:

(ADCx_CLP1)

ADC Plus-Side General Calibration Value Register:

(ADCx_CLP0)

ADC Minus-Side General Calibration Value Register:

(ADCx_CLMD)

ADC Minus-Side General Calibration Value Register:

(ADCx_CLMS)

ADC Minus-Side General Calibration Value Register:

(ADCx_CLM4)

ADC Minus-Side General Calibration Value Register:

(ADCx_CLM3)

ADC Minus-Side General Calibration Value Register:

(ADCx_CLM2)

ADC Minus-Side General Calibration Value Register:

(ADCx_CLM1)

ADC Minus-Side General Calibration Value Register:

(ADCx_CLM0)

4. 功能描述

4.1 时钟选择和分频比控制

1.有4个时钟源可选,然后通过分频比获取需要的时钟ADCK,4路时钟源分别是:

(1)BUS CLK:reset后的默认选项

(2)BUS CKL二分频

(3)ALTCLK:MCU在normal stop模式时使用ALTCLK

(4)ADACK:由ADC内部产生,如果选择这个时钟源,在转换开始时会自动激活,转化结束后自动失效。为了避免延时,可在初始化ADC前使能该时钟

不管选用哪个时钟源,必需符合ADCK,如果太高还需要分频

4.2 参考电压选择

可选择两个参考电压对之一来用作参考电压

4.3 硬件触发和通道选择

1.通过设置SC2[ADTRG] 使能来产生ADHWT 硬件触发使能,当有ADHWTSn 事件发生,即可触发ADC转换

2.通道选择

• ADHWTSA active selects SC1A.

• ADHWTSn active selects SC1n

3.转换结果存放

• ADHWTSA active selects RA register

• ADHWTSn active selects Rn register

4.4 转换控制

1.转换可以由软件或硬件触发

2.ADC模块可以被配置为:

• Low-power operation

• Long sample time

• Continuous conversion

• Hardware average

• Automatic compare of the conversion result to a software determined compare value

4.4.1 启动转换

1.如下几种方式可以启动转换:

1).如果软件触发操作被选择,通过写SC1A且SC1n[ADCH] 非全1,会启动转换

2).硬件触发方式被选择,且硬件触发事件发生

3).当连续转换使能时,结果被传送到数据寄存器即启动新的一次转换

4.4.2 完成转换

当转换结果被传送到数据结果寄存器中标识转换完成

4.4.3 终止转换

下列情况会终止转换:

1.当前正在控制转换时,写入了SC1A

2.写入除SC1A~SC1n寄存器之外的寄存器

3.MCU RESET

4.MCU进入Normal stop mode且ADACK或可选时钟源没有使能

4.4.4. 功耗控制

ADC模块在转换完毕会保持idle,直到转换被初始化

4.4.5 采样时间和total转换时间

TODO

4.4.6 转换时间举例

TODO

4.4.7 硬件平均值功能

TODO

4.5 自动比较功能

TODO

4.6 校准功能

TODO

4.7 用户定义OFFSET功能

TODO

4.8 温度传感器功能

TODO

4.9 MCU 等待模式操作

TODO

4.10 MCU Nortmal stop 模式操作

TODO

4.11 MCU LOW-POWER STOP模式操作

TODO

k64 datasheet学习笔记35---Analog-to-Digital Converter (ADC)的更多相关文章

- k64 datasheet学习笔记1---概述

1.前言 k64 datasheet描述了Freescale MCU的特性.架构和编程模型,主要是面向使用MCU的系统架构和软件应用开发人员. 2.模块划分 datasheet主要按功能对模块进行划分 ...

- k64 datasheet学习笔记45---10/100-Mbps Ethernet MAC(ENET)之功能描述

1.前言 本文是对K64 datasheet 之ENET部分的功能描述,将对每个部分进行详细说明 2.Ethernet MAC frame formats MAC帧组成格式 (1)7字节前导码:如按最 ...

- k64 datasheet学习笔记3---Chip Configuration之Analog

1.前言 本文主要讲述K64芯片配置,关于模拟部分的内容,主要包括:ADC, CMP, DAC, VREF 2.16bit SAR ADC 从上图可以看出ADC主要挂在外设总线0上,由于ADC的输入引 ...

- k64 datasheet学习笔记45---10/100-Mbps Ethernet MAC(ENET)之概述

1.前言 k64 ENET CORE 实现了10M/100Mbps的Ethernet MAC,与IEEE802.3-2002标准兼容. MAC层与全双工/半双工的10M/100Mbps以太网兼容: M ...

- k64 datasheet学习笔记11---Port Control and Interrupts (PORT)

1.前言 Port Control and Interrupt (PORT) 模块提供了port control,digital filtering,和外部中断功能 每个pin的大部分功能可被独立配 ...

- k64 datasheet学习笔记4---Clock distribution

1.前言 本文主要讲述K64时钟配置相关的内容. 2.clock overview 2.1 clock diagram 2.2 对clock diagram的信号说明 (1)MCG决定哪个clock ...

- k64 datasheet学习笔记4---Memory Map

1.前言 本文主要介绍K64地址空间的映射 2. System Memory Map 3. K64地址映射 4. Armv7m地址映射 4.1 Armv7M.System地址段(0XE0000000~ ...

- k64 datasheet学习笔记39---Programmable Delay Block (PDB)

0.前言 TODO 1.特性 TODO 4. 功能描述 4.1 PDB pre-trigger and trigger outputs PDB包含一个计数器,它的输出可以跟几个不同的数字值比较.如果P ...

- k64 datasheet学习笔记25--Multipurpose Clock Generator (MCG)

0.前言 MCG模块为MCU提供了几种可选时钟源.模块包含一个FLL和一个PLL.FLL使用内部或外部参考时钟是可控的,PLL受外部参考时钟控制 模块可以选择FLL或PLL输出时钟,或内/外部参考时钟 ...

随机推荐

- HTML特殊符号(字符实体)大全

TML常用特殊字符:只要你认识了 HTML 标记,你便会知道特殊字符的用处. HTML 原代码 显示结果 描述 < < 小于号或显示标记 > > 大于号或显示标记 & ...

- 2017-12-15python全栈9期第二天第三节之使用while循环输出0到10不包含7

#!/user/bin/python# -*- coding:utf-8 -*-count = 0while count < 10: count += 1 if count == 7 : con ...

- 最接近原点的K个点

一.题目描述 我们有一个由平面上的点组成的列表 points.需要从中找出 K 个距离原点 (0, 0) 最近的点 这里,平面上两点之间的距离是欧几里德距离 你可以按任何顺序返回答案.除了点坐标的顺序 ...

- HDFS-JavaAPI

一.pom.xml <?xml version="1.0" encoding="UTF-8"?> <project xmlns="h ...

- net-snmp开发教程

目录 1................................................................................................ ...

- hive记录-cdh配置hive和sentry

1.cdh添加组件-sentry-选择主机-配置数据库 2.配置数据库 1)mysql -uroot -p 2) create database sentry DEFAULT CHARSET utf8 ...

- Sqlserver中的储存过程

一.什么是存储过程(Stored Procedure) 存储过程是一段存储在数据库的“子程序”,本质是一个可重复使用的SQL代码块,可以理解为数据库端的“方法”. 存储过程的好处: ①提高性能:由于数 ...

- HDU 1030(三角数阵 数学)

题意是问在给定的三角形数阵中从一个数到另一个数所要跨过的边数. 最初的时候很迷,除了发现每层的数字个数与层数间的关系和每层数最后一个数与层数的关系外什么也没看出来,打算先求出数字所在的层数,然后计算到 ...

- MySQL 数据库应用程序编程

普通用户使用客户端应用程序(Client Application)和服务器程序(Server Application)通信以取得服务, 而服务器程序通常要和数据库服务器通信以取得数据存取服务, 这时就 ...

- SQL Server Management Studio 使用技巧

Ø 前言 本文主要介绍 SQL Server Management Studio 工具的使用,相信很多开发人员都比较熟悉此工具,特别是做 C# 开发的程序员,基本上都会经常使用该工具,当然也可以使用 ...