关于VGA显示实验的问题

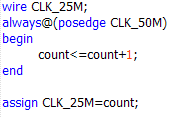

今天做了一个关于VGA的显示实验,但是由于产生的25M时钟不正确所以一直没有图像产生。刚开始的程序如下

关于VGA显示实验的问题的更多相关文章

- 基于FPGA的VGA显示静态图片

终于熬到暑假了,记过三四周的突击带考试,终于为我的大二画上了一个完整的句号,接下来终于可以静心去做自己想做的事情了,前一阵子报了一个线上培训班,学学Sobel边缘检测,之前一直在学习图像处理,但是因为 ...

- 基于FPGA的Uart接收图像数据至VGA显示

系统框图 前面我们设计了基于FPGA的静态图片显示,接下来我们来做做基于FPGA的动态图片显示,本实验内容为:由PC端上位机软件通过串口发送一幅图像数据至FPGA,FPGA内部将图像数据存储,最后扫描 ...

- 基于FPGA的VGA显示实验设计

基于FPGA的VGA显示实验设计 成果展示(优酷视频): 视频: 基于FPGA的VGA显示技术(手机控制) http://v.youku.com/v_show/id_XNjk4ODE3ODUy.htm ...

- VmodCAM图像采集 VGA显示

先上图 总体框图 效果图 效果不是很好,因为暂时用的是zedboard自带的VGA,其只能RGB只有3*3*3的彩色度 VmodCAM原理图 VmodCAM的zedboard管脚约束见:http:// ...

- vga显示彩条

vga显示驱动程序可分为扫描行列和行列同步两个部分 //注意:只有在有效区域内给vga赋值才会有颜色变化 assign vga_b = isready ? vga_s[:] :'d0; assign ...

- 纠错:基于FPGA串口发送彩色图片数据至VGA显示

今天这篇文章是要修改之前的一个错误,前面我写过一篇基于FPGA的串口发送图片数据至VGA显示的文章,最后是显示成功了,但是显示的效果图,看起来确实灰度图,当时我默认我使用的MATLAB代码将图片数据转 ...

- 基于FPGA驱动VGA显示图片的小问题

学习VGA显示图片的过程中,遇到了一个小问题,我在显示屏上开了一个60x60的框,放了一张图片进去显示,但是最终的结果如下图所示. 出现了一个竖黑边,看了看代码,分析了一下逻辑没问题,然而看这个显示那 ...

- FPGA驱动VGA显示静态图片

一 .前言 本文设计思想采用明德扬至简设计法.VGA是最常见的视频显示接口,时序也较为简单.本文从利用显示屏通过VGA方式显示测试图案及静态图片着手带大家接触图像显示应用,算是为后续VGA显示摄像头采 ...

- verilog实现VGA显示方块屏幕保护

verilog实现VGA显示方块屏幕保护 输入和输出 时钟信号 clk 复位信号 reset rgb三颜色输出 [2:0] r,g, [1:0] b 行信号输出 hs 列信号输出 vs 参数设定 设定 ...

随机推荐

- SAS学习笔记18 length、lengthn、lengthc函数

- Pod——状态和生命周期管理及探针和资源限制

一.什么是Podkubernetes中的一切都可以理解为是一种资源对象,pod,rc,service,都可以理解是 一种资源对象.pod的组成示意图如下,由一个叫”pause“的根容器,加上一个或多个 ...

- zookeeper安装和使用 windows环境

简介 ZooKeeper是一个分布式的,开放源码的分布式应用程序协调服务,是Google的Chubby一个开源的实现,是Hadoop和Hbase的重要组件.它是一个为分布式应用提供一致性服务的软件,提 ...

- C#获取Excel表格所有sheet名(Epplus)

原文:C#获取Excel表格所有sheet名(Epplus) 版权声明:本文为博主原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接和本声明. 本文链接:https://blog. ...

- MVC的12种ActionResult介绍以及应用示例【转】

一.介绍 1.ViewResult 表示一个视图结果,它根据视图模板产生应答内容.对应得Controller方法为View. 2.PartialViewResult 表示一个部分视图结果,与ViewR ...

- kong 命令(五)plugin

介绍 plugin 插件 是运用在kong网关各模块的功能.在http请求或响应过程中执行的插件: 可以实现认证.负载.加密等功能. kong官网提供了一些插件:https://docs.konghq ...

- 编程模型&编程思想

编程模型 1.面向对象编程OOP 2.面向切面编程AOP Java静态接口,Java动态代理,字节码提升. 面向切面的两个方面: 拦截判断:方法,注解,参数,异常 拦截执行:前置,后置,返回,异常 3 ...

- Unity UGUI Button 无法点击问题一例

理论上,只要一个按钮自己这一层或者子节点有一个控件勾选了RaycastTarget,并且按钮为Interactable的.并且不被其他可以点击的控件阻挡,那么这个按钮就可以被点击 在调一个界面时发现一 ...

- 最近发现了一篇讲解Vue的虚拟DOM,diff很棒的文章,特定记录转载一下

本文章是转载的,为了方便以后复习,特地记录一下.他人请去原地址观看!!! 文章原地址:https://blog.csdn.net/m6i37jk/article/details/78140159 作者 ...

- Point to class member

#include <iostream> using namespace std; class Student { public: Student(string n, int nu):nam ...