DFT Architecture

Design For Test

- 在实际生产过程中产生的physical defect是导致芯片功能出错的根本原因

- 如何根据结构产生测试向量呢?主要考虑physical defect

- physical defect有多种,针对不同的physical defect有不同的处理方式

- Design - 是为了产生结构性测试向量,利用设计对于fault model数学模型进行求解,求解之后产生结构性的测试向量

- physical defect具有复杂性和多样相,直接对于fault model进行求解,模型会非常大

- DFT - 首先将physical defect进行分解,建立不同的fault model,针对这些fault model(故障模型)进行求解

DFT Structure Test

- 主要介绍function logic进行讲解

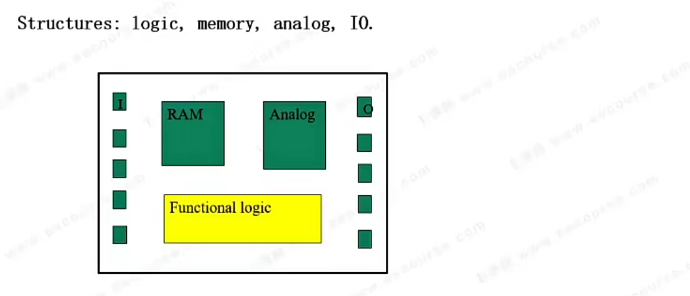

时序电路和组合逻辑电路

- 对于组合电路而言,如果中间出现故障,可以在input pin上输入激励,在output pin上接受结果进行测试

- 对于时序电路,如果要对某个模型进行求解,输入需要经过多级logic进行输入,输出也需要经过多级logic进行输出,因为中间的延时或者其他因素,导致可能检测不出其中的问题

- 时序逻辑电路测试 - 时间更长,难度更大

- 能否将时序逻辑电路转变为组合逻辑电路的方式进行测试?

Scan Synthesis

针对function logic需要做的辅助性设计

- scan replacement - 替换操作

- scan stitching - 连接操作

- scan synthesis不是在RTL级别进行的,scan synthesis是作用在综合之后的网表上的,在综合完成之后,进行插入scan的操作

- scan synthesis插入的方式:可以综合之后,独立进行,或者是包含在逻辑综合过程之中

- scan synthesis作用:将难测试的时序电路转变为一个易于测试的时序逻辑电路

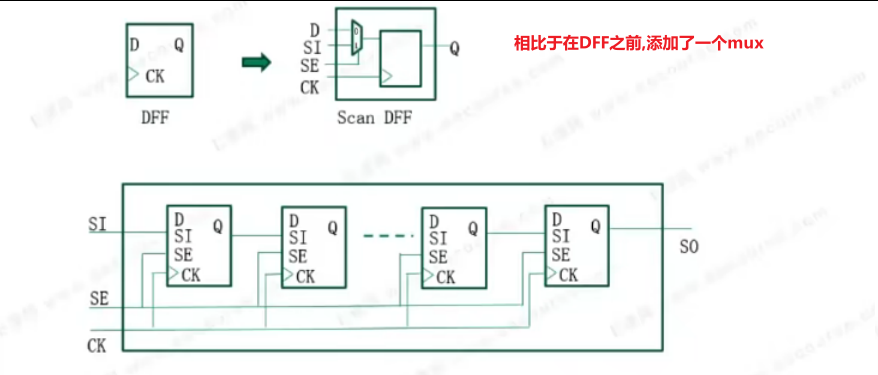

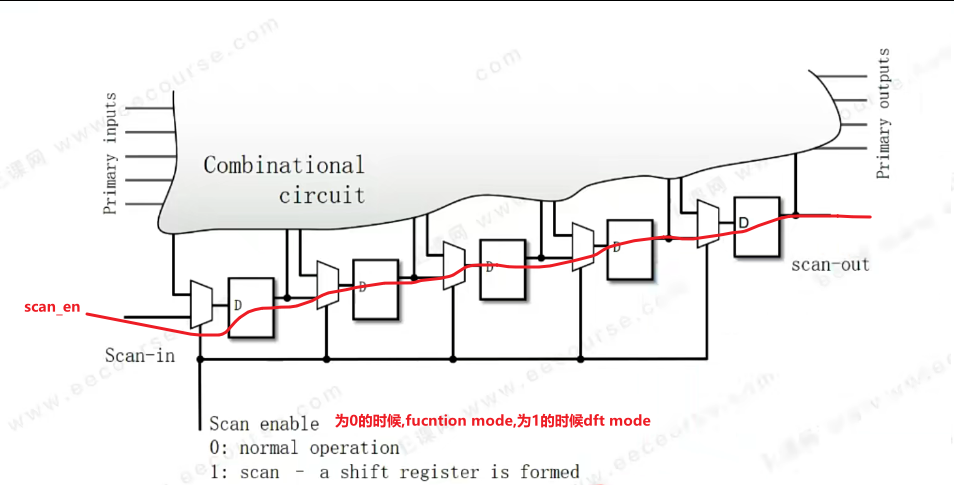

scan replacement & scan stitching

- 在数据输入端添加mux,增加SI,SE pin,当SE为低电平的时候,输出为D,和原来的DFF一致,SE为低的时候,实现function功能

- scan插入不能破坏原来的function logic

- 替换之后SE和SI是floating,scan stitching就是将SI和SE连接出来

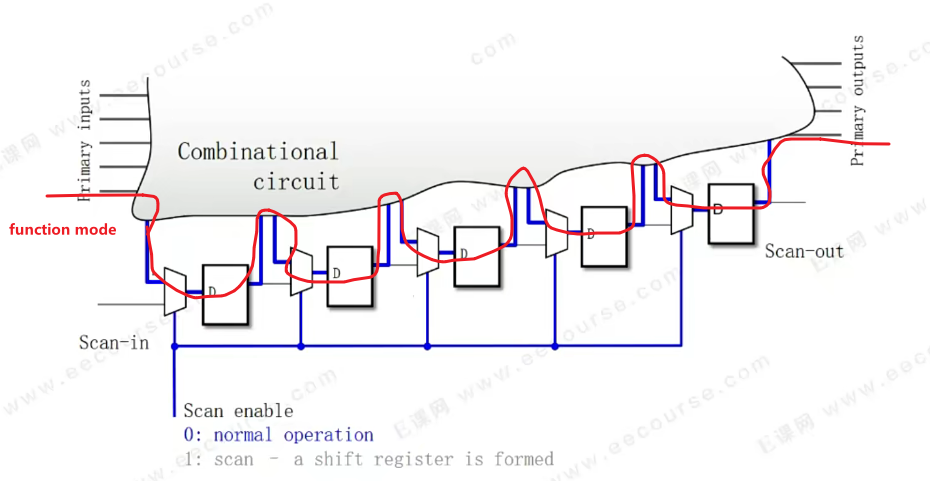

- SE连接:在芯片输入端添加一个sacn_en port,这个port会驱动所有替换之后cell的SE pin,当这个port为0的时候,design工作在function mode下

- SI连接:替换之后的DFF,SI将Q端进行连接,形成chain,连接SI和SO

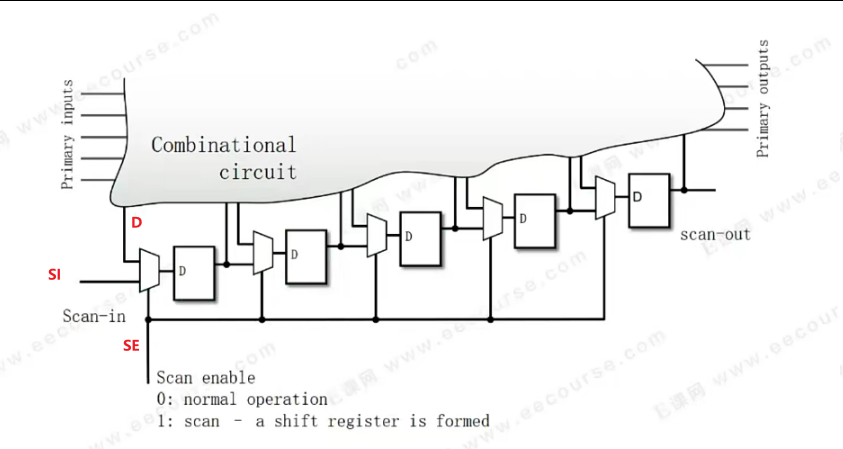

- 辅助性设计完成,需要产生结构性测试向量?如何实现将时序电路的测试转变为组合逻辑电路

Scan Operation

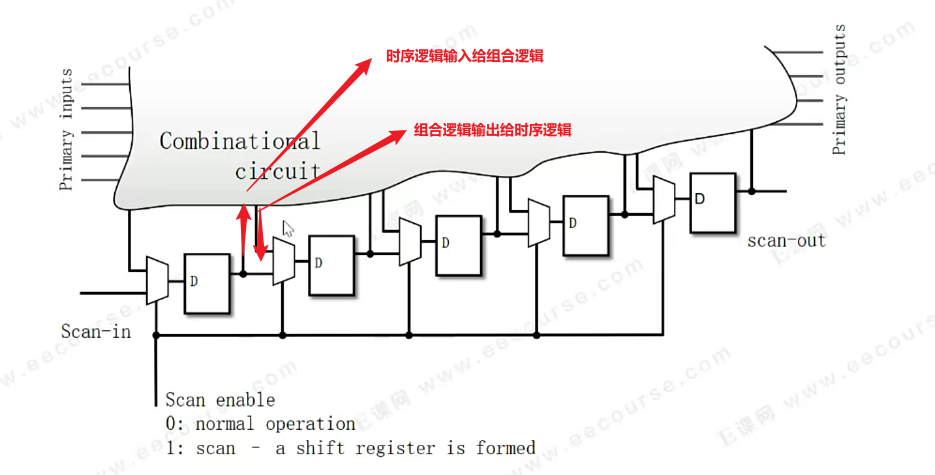

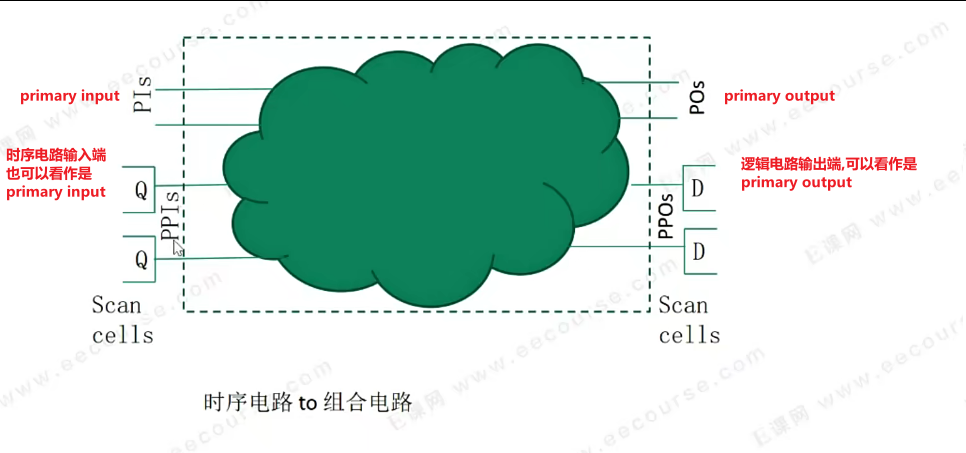

Circuit Transition

- 将时序逻辑转变为组合逻辑模型,进行求解结构性测试向量

- PIs - 直接通过pin输入,POs通过输出pin观察稳定的值

- PPIs和PPOs如何进行输入和观察? PPIs和PPOs是假设的pin,用于转变时序逻辑为组合逻辑,PPIs有很多电路内部的结果,如何进行输入,通过辅助性设计实现SI和SO(输入PPIs和PPOs)

- scan synthesis进行可以在综合的过程中,综合过程是需要考虑时序和面积的,加入scan之后,会添加组合逻辑,在综合过程中可以考虑到scan replacement之后的的cell delay和timing优化

- PPOs观测过程:PIs和PPIs输入之后,经过一段时间,POs和PPOs的值都是稳定的,此时scan enbale为低的时候,function logic是被打通的,此时来一个clock pluse,组合逻辑输入到时序逻辑的值是可以被DFF锁存起来的;scan enable拉高,可以将锁存的值一拍一拍的拿到,可以观测SI

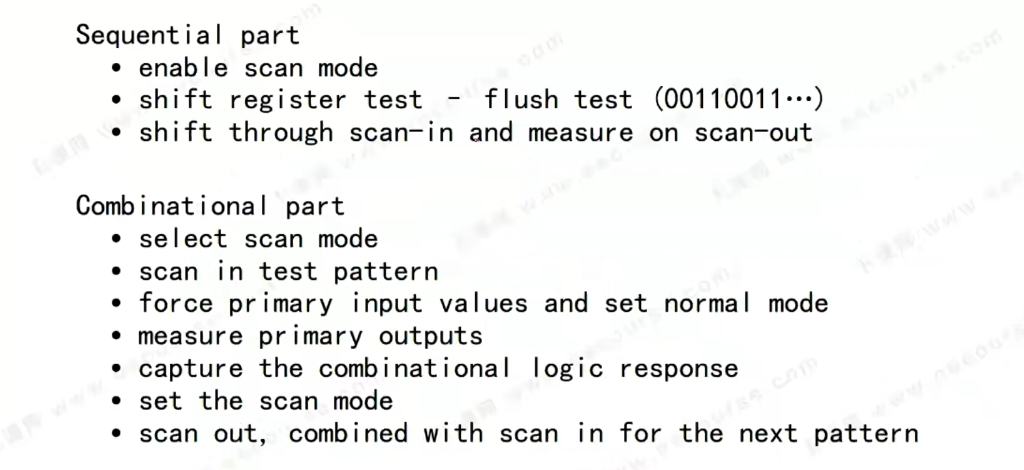

Test Procedure

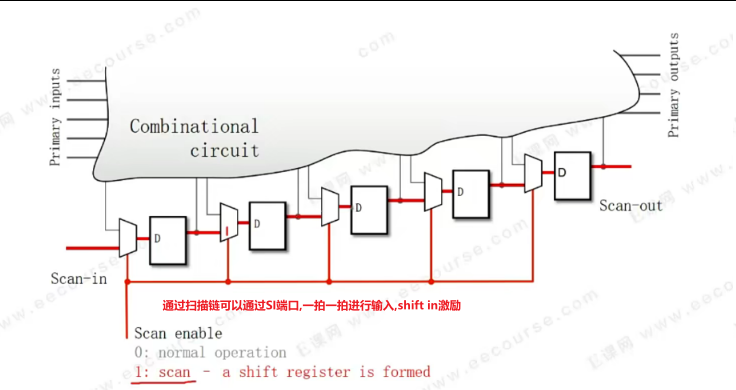

- 对于scan chain进行测试,在扫描链上是否能够正确的shift in和shift out,只有能正确的移入0和1的值,才能在PPO上添加正确的激励

- 对于scan chain进行测试,实际上也包含了对于时序逻辑的测试

- 时序逻辑测试过程:enable scan mode打通扫描链,shifter register test - 输入一组固定的pattern进行测试,通过scan input一拍一拍的输入pattern,通过scan out,一拍一拍向外取出值,看输入pattern的值是否被正确取出,正确取出表示scan chain没有问题

- 组合逻辑测试:scan enable拉高,选择scan mode;sacn in test pattern,是对PPI赋值的过程,如果有5个cell,经过5拍就可以将PPI的值赋好;对PIs进行赋值,通过chip io上进行赋值,赋值完成之后切换到function mode,等待一段时间之后,POs和PPOs都是稳定的;进行比较POs的值;在时钟边沿,捕获PPOs的值锁存到DFF中,然后切换到scan mode,通过scan out端口一拍一拍取出

- 前一条pattern shift out的时候,后一条pattern可以进行shift in,两个过程互不影响

Scan synthesis中经常遇到的问题

- Negative + Positive,一部分cell上升沿驱动,一部分下降沿驱动,连在一起需要考虑什么?

- Clock Domain Crossing

- Scan Design Rule Check(DRC),cell连接起来是不是能够形成scan chain

How to consider scan synthesis in project

- 从项目的角度考虑辅助设计

- scan chain测试时间主要在shift in

- 实际项目中会有很多条scan chain,对于IO数量有要求,在chip level上需要考虑有多少个IO,通常项目中,不会为scan test增加新的IO,通常会考虑IO复用,使用function mode的IO进行复用

- 考虑share IO需要使用Pin Mux

- 考虑减小scan chain的长度,减小时间成本

How many IOs are available for scan testing

- 使用ATE进行测试,需要考虑ATE的channel的数量

- 芯片IO数量会影响Package方式,通常按照最小pin数量的封装方式进行设计

- scan channels/scan enable/test mode/scan clock

Shared IO and Pin Mux

- pin mux io复用,列举出当前chip一共有多少个io,在不同的模式下(function mode/dft mode/bist test/cpu test等)选择不同的io

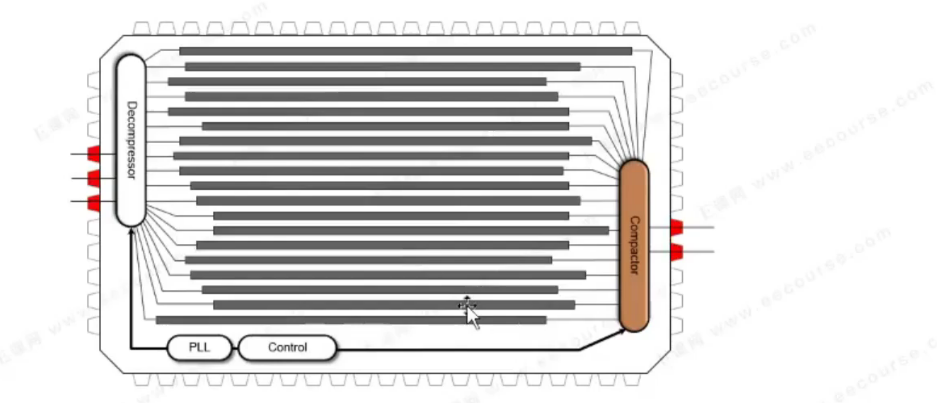

How to define compression ratio

- sacn chain越短,test成本越低

- scan chain越短,IO数量越多

- 通过解码和编码的方式,通过少的输入=,将少量的输入进行编码,得到多种不同的组合,然后通过解码输出,可以减少io pin的使用和减少scan chain length,从而减少成本

- 加入综合之后有100万个DFF,有100对pin,需要shift 10000个cycle才能讲PPI进行输入完成,时间比较长

How to form scan chains?

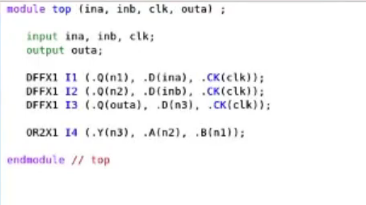

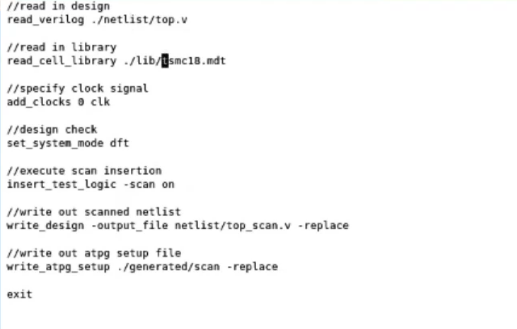

实例

输入综合之后的网表

输入library

执行脚本

DFT Architecture的更多相关文章

- DFT 问答 II

1. Boundary Scan A:Boundary scan 顾名思义,是附加在芯片I/O 周边的扫描测试链,它通过专门的测试端口(TAP)访问.在测试模式下,边界扫描链会接管功能逻辑,对I/O进 ...

- Undefined symbols for architecture arm64解决方案

在iOS开发中经常遇到的一个错误是Undefined symbols for architecture arm64,这个错误表示工程某些地方不支持arm64指令集.那我们应该怎么解决这个问题了?我们不 ...

- Optimal Flexible Architecture(最优灵活架构)

来自:Oracle® Database Installation Guide 12_c_ Release 1 (12.1) for Linux Oracle base目录命名规范: /pm/s/u 例 ...

- EF框架组件详述【Entity Framework Architecture】(EF基础系列篇3)

我们来看看EF的框架设计吧: The following figure shows the overall architecture of the Entity Framework. Let us n ...

- [Architecture] 系统架构正交分解法

[Architecture] 系统架构正交分解法 前言 随着企业成长,支持企业业务的软件,也会越来越庞大与复杂.当系统复杂到一定程度,开发人员会发现很多系统架构的设计细节,很难有条理.有组织的用一张大 ...

- Stack Overflow: The Architecture - 2016 Edition

To get an idea of what all of this stuff “does,” let me start off with an update on the average day ...

- ios build时,Undefined symbols for architecture xxx问题的总结

简单来说,Undefined symbols基本上等于JAVA的ClassNotFoundException,最常见的原因有这几种: build的时候没有加framework 比如说,有一段代码我用了 ...

- Undefined symbols for architecture x86_64: "_OBJC_CLASS_$_The49DayPersonalFullscreenGiftModel", referenced from: objc-class-ref in The49DayPersonalRoomGiftModel.o ld: symbol(s) not found for a

Undefined symbols for architecture x86_64: "_OBJC_CLASS_$_The49DayPersonalFullscreenGiftModel&q ...

- ios开发错误之: Undefined symbols for architecture x86_64

错误如下: Undefined symbols for architecture x86_64: "_OBJC_CLASS_$_RoutingHTTPServer", refere ...

- 转载:一幅图弄清DFT与DTFT,DFS的关系

转载:http://www.cnblogs.com/BitArt/archive/2012/11/24/2786390.html 很多同学学习了数字信号处理之后,被里面的几个名词搞的晕头转向,比如DF ...

随机推荐

- 从零开始用 Axios 请求后端接口

对于前端同学来说,请求后端接口是一个非常通用的东西.在十几年前的时候,我们还用 Ajax 去请求后端接口.但在 2023 年的今天,很多框架都很成熟了,我们有了更加快捷的方式 -- Axios 框架. ...

- selenium之三种等待,强制等待、隐式等待和显式等待

显式等待 presence_of_element_locatedpresence_of_all_elements_locatedvisibility_of_any_elements_located ...

- Go 语言为什么建议多使用切片,少使用数组?

大家好,我是 frank,「Golang 语言开发栈」公众号作者. 01 介绍 在 Go 语言中,数组固定长度,切片可变长度:数组和切片都是值传递,因为切片传递的是指针,所以切片也被称为"引 ...

- P6357 题解

Luogu 题面 题目描述 给定一串长度为 \(n\) 的数字,数字为 \(0 \sim 9\) 之间的任意一个,下标从 \(1\) 记起. 然后进行 \(m\) 次区间查询,每次查找区间 \([l, ...

- CSS实例-切换开关

在线展示: 矩形开关 .switch { position: relative; display: inline-block; width: 60px; height: 34px } .switch ...

- android Handler应用

android在运行时改变ui需要在ui线程中修改才行,不然就会报错或者无法启动应用. 我们怎么可以做事不管呢? 既然不能在ui线程外的地方运行修改ui的代码,我们可以用Handler解决这个问题, ...

- Javac多模块化编译

转载:原文链接 从SDK9开始,Java支持多模块编译.那么,怎么用javac实现多模块编译呢? 项目介绍 先来看看我们的项目. 首先lib文件夹下是依赖模块,有一个hello模块.hello模块包含 ...

- C++产生N以内的随机整数

C++产生N(这里N=100)以内的随机整数的例子: #include <iostream> #include <ctime> using namespace std; int ...

- SaaS 营销怎么做?几点思考

按大部分 SaaS 公司组织架构,梳理了这 4 大业务部门(产品.市场.销售.服务-客户成功)的职责和客户价值链条.如图: 根据客户价值体验地图,分为两块过程: 客户营销过程 客户成功过程 针对 Sa ...

- Java PDF文档转换 — PDF转Excel、SVG转PDF

概述 Spire.PDF for Java支持将PDF文档高质量地转换为XPS.图片.SVG.Word.HTML和PDF/A格式,以及支持将XPS.HTML文档转换为PDF格式.本文将通过代码演示来介 ...