Wishbone接口Altera JTAG UART

某些时候,我们在使用Altera FPGA的时候,尤其是涉及SoC系统的时候,通常需要一个串口与PC交互。使用Altera的USB-Blaster免去了外接一个串口。我们可以使用下面所述的IP核通过USB-Blaster将PC的字符传入FPGA或者从FPGA将字符数据发送至PC。

alt_jtag_atlantic jtag_uart_alt_jtag_atlantic

(

.clk (clk),

.r_dat (r_dat),

.r_ena (r_ena),

.r_val (r_val),

.rst_n (rst_n),

.t_dat (t_dat),

.t_dav (t_dav),

.t_ena (t_ena),

.t_pause (t_pause)

); defparam jtag_uart_alt_jtag_atlantic.INSTANCE_ID = ,

jtag_uart_alt_jtag_atlantic.LOG2_RXFIFO_DEPTH = ,

jtag_uart_alt_jtag_atlantic.LOG2_TXFIFO_DEPTH = ,

jtag_uart_alt_jtag_atlantic.SLD_AUTO_INSTANCE_INDEX = "YES";

下面贴出一个Wishbone接口的JTAG UART的代码描述:

// synthesis translate_off

`timescale 1ns / 1ps

// synthesis translate_on module wb_jtag_uart (

input clk_i,

input rst_i, input wb_stb_i,

input wb_cyc_i,

output wb_ack_o,

input wb_adr_i,

input wb_we_i,

input [:] wb_dat_i,

output [:] wb_dat_o,

output wb_irq_o

); /* synthesis ALTERA_ATTRIBUTE = "SUPPRESS_DA_RULE_INTERNAL=\"R101,C106,D101,D103\"" */ reg ac;

wire activity;

wire av_irq;

wire [ : ] av_readdata;

wire [ : ] av_writedata;

reg av_waitrequest;

reg fifo_AE;

reg fifo_AF;

wire fifo_EF;

wire fifo_FF;

wire fifo_clear;

wire fifo_rd;

wire [ : ] fifo_rdata;

wire [ : ] fifo_wdata;

reg fifo_wr;

reg ien_AE;

reg ien_AF;

wire ipen_AE;

wire ipen_AF;

reg pause_irq;

wire [ : ] r_dat;

wire r_ena;

reg r_val;

wire rd_wfifo;

reg read_0;

wire rfifo_full;

wire [ : ] rfifo_used;

reg rvalid;

reg sim_r_ena;

reg sim_t_dat;

reg sim_t_ena;

reg sim_t_pause;

wire [ : ] t_dat;

reg t_dav;

wire t_ena;

wire t_pause;

wire wfifo_empty;

wire [ : ] wfifo_used;

reg woverflow;

wire wr_rfifo;

wire clk;

wire rst_n;

wire av_read_n;

wire av_write_n;

wire av_address;

wire av_chipselect; assign clk = clk_i;

assign rst_n = ~rst_i;

assign av_address = wb_adr_i;

assign wb_dat_o = av_readdata;

assign av_writedata = wb_dat_i;

assign wb_irq_o = av_irq;

assign wb_ack_o = ~av_waitrequest;

assign av_read_n = ~(wb_cyc_i & wb_stb_i & (~wb_we_i));

assign av_write_n = ~(wb_cyc_i & wb_stb_i & wb_we_i);

assign av_chipselect = wb_cyc_i & wb_stb_i; //avalon_jtag_slave, which is an e_avalon_slave

assign rd_wfifo = r_ena & ~wfifo_empty;

assign wr_rfifo = t_ena & ~rfifo_full;

assign fifo_clear = ~rst_n;

wb_jtag_uart_scfifo_w jtag_uart_scfifo_w

(

.clk (clk),

.fifo_FF (fifo_FF),

.fifo_clear (fifo_clear),

.fifo_wdata (fifo_wdata),

.fifo_wr (fifo_wr),

.r_dat (r_dat),

.rd_wfifo (rd_wfifo),

.wfifo_empty (wfifo_empty),

.wfifo_used (wfifo_used)

); wb_jtag_uart_scfifo_r jtag_uart_scfifo_r

(

.clk (clk),

.fifo_EF (fifo_EF),

.fifo_clear (fifo_clear),

.fifo_rd (fifo_rd),

.fifo_rdata (fifo_rdata),

.rfifo_full (rfifo_full),

.rfifo_used (rfifo_used),

.rst_n (rst_n),

.t_dat (t_dat),

.wr_rfifo (wr_rfifo)

); assign ipen_AE = ien_AE & fifo_AE;

assign ipen_AF = ien_AF & (pause_irq | fifo_AF);

assign av_irq = ipen_AE | ipen_AF;

assign activity = t_pause | t_ena;

always @(posedge clk or negedge rst_n)

begin

if (rst_n == )

pause_irq <= 'b0;

else // only if fifo is not empty...

if (t_pause & ~fifo_EF)

pause_irq <= 'b1;

else if (read_0)

pause_irq <= 'b0;

end always @(posedge clk or negedge rst_n)

begin

if (rst_n == )

begin

r_val <= 'b0;

t_dav <= 'b1;

end

else

begin

r_val <= r_ena & ~wfifo_empty;

t_dav <= ~rfifo_full;

end

end always @(posedge clk or negedge rst_n)

begin

if (rst_n == )

begin

fifo_AE <= 'b0;

fifo_AF <= 'b0;

fifo_wr <= 'b0;

rvalid <= 'b0;

read_0 <= 'b0;

ien_AE <= 'b0;

ien_AF <= 'b0;

ac <= 'b0;

woverflow <= 'b0;

av_waitrequest <= 'b1;

end

else

begin

fifo_AE <= {fifo_FF,wfifo_used} <= ;

fifo_AF <= ('h40 - {rfifo_full,rfifo_used}) <= 8;

fifo_wr <= 'b0;

read_0 <= 'b0;

av_waitrequest <= ~(av_chipselect & (~av_write_n | ~av_read_n) & av_waitrequest);

if (activity)

ac <= 'b1;

// write

if (av_chipselect & ~av_write_n & av_waitrequest)

// addr 1 is control; addr 0 is data

if (av_address)

begin

ien_AF <= av_writedata[];

ien_AE <= av_writedata[];

if (av_writedata[] & ~activity)

ac <= 'b0;

end

else

begin

fifo_wr <= ~fifo_FF;

woverflow <= fifo_FF;

end

// read

if (av_chipselect & ~av_read_n & av_waitrequest)

begin

// addr 1 is interrupt; addr 0 is data

if (~av_address)

rvalid <= ~fifo_EF;

read_0 <= ~av_address;

end

end

end assign fifo_wdata = av_writedata[ : ];

assign fifo_rd = (av_chipselect & ~av_read_n & av_waitrequest & ~av_address) ? ~fifo_EF : 'b0;

assign av_readdata = read_0 ? { {{'b0}},rfifo_full,rfifo_used,rvalid,woverflow,~fifo_FF,~fifo_EF,1'b0,ac,ipen_AE,ipen_AF,fifo_rdata } : { {{'b0}},(7'h40 - {fifo_FF,wfifo_used}),rvalid,woverflow,~fifo_FF,~fifo_EF,'b0,ac,ipen_AE,ipen_AF,{6{1'b0}},ien_AE,ien_AF }; //synthesis read_comments_as_HDL on

// alt_jtag_atlantic jtag_uart_alt_jtag_atlantic

// (

// .clk (clk),

// .r_dat (r_dat),

// .r_ena (r_ena),

// .r_val (r_val),

// .rst_n (rst_n),

// .t_dat (t_dat),

// .t_dav (t_dav),

// .t_ena (t_ena),

// .t_pause (t_pause)

// );

//

// defparam jtag_uart_alt_jtag_atlantic.INSTANCE_ID = 0,

// jtag_uart_alt_jtag_atlantic.LOG2_RXFIFO_DEPTH = 6,

// jtag_uart_alt_jtag_atlantic.LOG2_TXFIFO_DEPTH = 6,

// jtag_uart_alt_jtag_atlantic.SLD_AUTO_INSTANCE_INDEX = "YES";

//

//

//synthesis read_comments_as_HDL off endmodule module wb_jtag_uart_scfifo_w (

// inputs:

clk,

fifo_clear,

fifo_wdata,

fifo_wr,

rd_wfifo, // outputs:

fifo_FF,

r_dat,

wfifo_empty,

wfifo_used

); output fifo_FF;

output [ : ] r_dat;

output wfifo_empty;

output [ : ] wfifo_used;

input clk;

input fifo_clear;

input [ : ] fifo_wdata;

input fifo_wr;

input rd_wfifo; wire fifo_FF;

wire [ : ] r_dat;

wire wfifo_empty;

wire [ : ] wfifo_used; //synthesis read_comments_as_HDL on

// scfifo wfifo

// (

// .aclr (fifo_clear),

// .clock (clk),

// .data (fifo_wdata),

// .empty (wfifo_empty),

// .full (fifo_FF),

// .q (r_dat),

// .rdreq (rd_wfifo),

// .usedw (wfifo_used),

// .wrreq (fifo_wr)

// );

//

// defparam wfifo.lpm_hint = "RAM_BLOCK_TYPE=AUTO",

// wfifo.lpm_numwords = 64,

// wfifo.lpm_showahead = "OFF",

// wfifo.lpm_type = "scfifo",

// wfifo.lpm_width = 8,

// wfifo.lpm_widthu = 6,

// wfifo.overflow_checking = "OFF",

// wfifo.underflow_checking = "OFF",

// wfifo.use_eab = "ON";

//

//synthesis read_comments_as_HDL off endmodule module wb_jtag_uart_scfifo_r (

// inputs:

clk,

fifo_clear,

fifo_rd,

rst_n,

t_dat,

wr_rfifo, // outputs:

fifo_EF,

fifo_rdata,

rfifo_full,

rfifo_used

);

output fifo_EF;

output [ : ] fifo_rdata;

output rfifo_full;

output [ : ] rfifo_used;

input clk;

input fifo_clear;

input fifo_rd;

input rst_n;

input [ : ] t_dat;

input wr_rfifo; wire fifo_EF;

wire [ : ] fifo_rdata;

wire rfifo_full;

wire [ : ] rfifo_used; //synthesis read_comments_as_HDL on

// scfifo rfifo

// (

// .aclr (fifo_clear),

// .clock (clk),

// .data (t_dat),

// .empty (fifo_EF),

// .full (rfifo_full),

// .q (fifo_rdata),

// .rdreq (fifo_rd),

// .usedw (rfifo_used),

// .wrreq (wr_rfifo)

// );

//

// defparam rfifo.lpm_hint = "RAM_BLOCK_TYPE=AUTO",

// rfifo.lpm_numwords = 64,

// rfifo.lpm_showahead = "OFF",

// rfifo.lpm_type = "scfifo",

// rfifo.lpm_width = 8,

// rfifo.lpm_widthu = 6,

// rfifo.overflow_checking = "OFF",

// rfifo.underflow_checking = "OFF",

// rfifo.use_eab = "ON";

//

//synthesis read_comments_as_HDL off endmodule

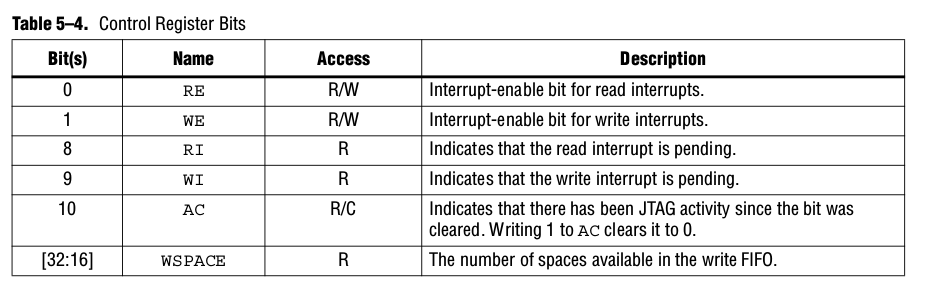

关于这个IP核(alt_jtag_atlantic)的寄存器的说明,在Altera的文档中有所说明。其实非常简单,只有两个32位的寄存器。

Wishbone接口Altera JTAG UART的更多相关文章

- [原创]iFPGA-Cable FT2232H Xilinx / Altera / Lattice 三合一JTAG & UART调试器-详细使用说明

iFPGA-Cable调试器使用说明 全文分为6部分: 第0部分:实物.连线及其驱动安装说明 第1部分:Xilinx JTAG 第2部分:UART 第3部分:Altera JTAG 第4部分:Latt ...

- [原创]iFPGA-Cable FT2232H JTAG & UART调试器

iFPGA-Cable FT2232H JTAG & UART调试器 [特性] 采用FT2232H,双通道接口: 支持UART: 支持JTAG,Digilent SMT-1,TCK最大时钟频率 ...

- Wishbone接口通用RAM

/* ************************************************************************************************ ...

- 【iCore3 双核心板_FPGA】实验二十三:使用JTAG UART终端打印信息

实验指导书及代码包下载: http://pan.baidu.com/s/1c83OPC iCore3 购买链接: https://item.taobao.com/item.htm?id=5242294 ...

- openrisc 之 Wishbone总线学习笔记——接口信号定义

这部分内容就是copy下来的,网上到处都有.先看看接口啥样子,在详细说明 接口定义copy http://blog.csdn.net/ce123/article/details/6929897.百度文 ...

- Uart、SPI和I2C的区别

串口通信:UART.SPI.I2C区别[引用] 1.UART就是两线,一根发送一根接收,可以全双工通信,线数也比较少.数据是异步传输的,对双方的时序要求比较严格,通信速度也不是很快.在多机通信上面 ...

- JLINK使用教程详解,以及与JTAG区别

对于一个新手来说,一切都不容易. 而从头学起也是一件非常美好的事. 观看 调试ARM,要遵循ARM的调试接口协议,JTAG就是其中的一种.当仿真时,IAR.KEIL.ADS等都有一个公共的调试 ...

- openrisc 之 Wishbone总线学习笔记——总线互联

一,总线命名规范 1,wishbone总线接口信号都是高电平有限 2,wishbone接口信号都是以 _i ,或者是 _o 结束.i表示输入, o表示输出. ()表示该信号为总线信号,总线位宽可以大于 ...

- [原创]FPGA JTAG工具设计(二)

经过前期打样 基于FT2232H的JTAG &UART板级已经初步形成 在Viado环境和ISE(13.2+)环境可以使用 速度支持10MHz/15MHz/30MHz 在ISE iMpact下 ...

随机推荐

- awk处理之案例六:awk根据条件插入文本

编译环境 本系列文章所提供的算法均在以下环境下编译通过. [脚本编译环境]Federa 8,linux 2.6.35.6-45.fc14.i686 [处理器] Intel(R) Core(TM)2 Q ...

- linux命令(5):netstat命令

网络监控:netstat –in [显示所有配置接口的状态] 查看端口状态:netstat -anlp | grep 8080 [显示8080端口列出的监听状态] 查看某个进程软件名:netstat ...

- jenkins构建触发器定时任务Build periodically和Poll SCM【转载】

转至博客:上海-悠悠 前言 跑自动化用例每次用手工点击jenkins出发自动化用例太麻烦了,我们希望能每天固定时间跑,这样就不用管了,坐等收测试报告结果就行. 一.定时构建语法 * * * * * ( ...

- centos7 安装rlwrap

https://blog.csdn.net/zhjmozhi/article/details/78347216

- R语言平均值和加权平均值

> a=c(,,) > mean(a) #平均值 [] > wt=c(,,) > weighted.mean(a,wt) #加权平均值 []

- Web测试中容易被忽略的Charset问题

今天继续进行一个更综合的脚本制作,录制设置.进行录制.脚本修改,一切都轻车熟路,进行得很顺利.经过近一个小时的对比和修改,OK,脚本大功告成,终于可以小试牛刀了,嘿嘿. 运行,replay lo ...

- CentOS为中文显示

[sudo yum groupinstall chinese-support]命令即可安装

- STL模板整理 list

介绍: list容器是一种序列式容器,它是STL实现的双向链表,与vector相比它可以实现快速的插入和删除,但是不能够快速的随机访问. 头文件: #include <list> 构造函数 ...

- 洛谷——P1916 小书童——蚂蚁大战

P1916 小书童——蚂蚁大战 题目背景 小A在你的帮助下,开始“刷题”,他在小书童里发现了一款叫“蚂蚁大战”(又称蛋糕保卫战)的游戏.(你懂得) 题目描述 游戏中会出现n只蚂蚁,分别有a1,a2…… ...

- uva 10910(子集和问题)

Marks Distribution Time limit: 3.000 seconds In an examination one student appeared in N subjects an ...