Xilinx FPGA控制器的Everspin STT-DDR4设计指南

自旋转移扭矩磁阻随机存取存储器(STT-MRAM)是一种持久性存储技术,可利用各种工业标准接口提供性能,持久性和耐用性。 Everspin推出了STT-MRAM产品,该产品利用称为JE-DDR4的JEDEC标准DDR4接口的变体,它包含了对完整系统支持所需的独特功能。本文将帮助工程师了解Xilinx FPGA控制器的Everspin STT-DDR4设计指南

2.启用ST-DDR4

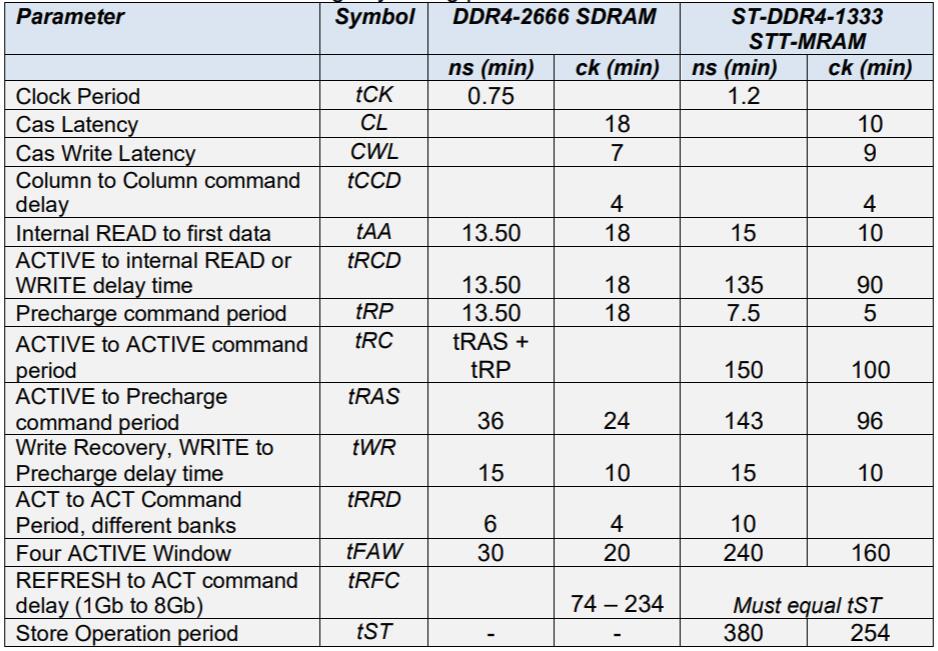

为了使设计人员能够快速集成ST-DDR4支持,该过程从Xilinx Vivado开发环境中生成的现有8Gb DDR4 SDRAM-2666存储器接口生成器(MIG)开始。与8Gb DDR4 SDRAM的差异如下,并将在后续章节中进行说明:

1.时间安排(减少工作频率,增加行访问时间,增加计数器宽度并减小CAS页面大小)

2.加电(校准–校准期间启用了防乱涂模式)

3.掉电(将所有相关数据塞入或移动到持久性存储器阵列中)

4.性能(增加管道深度并提高数据传输效率)

注意:健壮的ST-DDR4持久性存储器设计还需要系统级的纠错码(ECC)方案,但该文档不在本文范围之内。

3. DDR4 SDRAM-1333内存接口

在Xilinx设计环境中,将根据代表8Gb SDRAM DDR4-2666的速度和时序特性的输入参数生成DDR4接口逻辑。

由于MIG无法使用当前JEDEC标准以外的参数创建接口逻辑,因此必须首先创建兼容JEDEC的DDR4控制器。 everspin 1Gb ST-DDR4 1333器件最类似于8Gb DDR4-2666 SDRAM器件,因此请使用8Gb DDR4 SDRAM 2666规格SDRAM DDR4-2666中的时序值,一旦创建了DDR4接口逻辑,就可以修改时序,上电,掉电和性能参数,以启用ST-DDR4持久性存储器。

强烈建议在创建MIG之后,在Vivado中创建一个示例测试台,方法是右键单击.xci文件并选择名为“ Open IP Example Design ...”的菜单项。创建示例设计将创建一个新的Vivado项目。以及模拟新创建的MIG所需的所有测试文件。请参见Xilinx MIG创建教程,使用Vivado MIG为UltraScale设计存储器接口和控制器,以及存储器接口设计中心-UltraScale DDR4/DDR4存储器。

Xilinx FPGA控制器的Everspin STT-DDR4设计指南的更多相关文章

- Xilinx FPGA 的PCIE 设计

写在前面 近两年来和几个单位接触下来,发现PCIe还是一个比较常用的,有些难度的案例,主要是涉及面比较广,需要了解逻辑设计.高速总线.Linux和Windows的驱动设计等相关知识. 这篇文章主要针对 ...

- Xilinx FPGA结构

FPGA是什么?FPGA是现场可编程逻辑阵列,由可编程逻辑资源(LUT和 REG),可编程连线,可编程I/O构成.Xilinx的FPGA的基本结构是一样的,但随着半导体工艺的发展,FPGA的逻辑容量越 ...

- 基于Xilinx FPGA的视频图像采集系统

本篇要分享的是基于Xilinx FPGA的视频图像采集系统,使用摄像头采集图像数据,并没有用到SDRAM/DDR.这个工程使用的是OV7670 30w像素摄像头,用双口RAM做存储,显示窗口为320x ...

- Xilinx FPGA复位逻辑处理小结(转)

Xilinx FPGA复位逻辑处理小结 1. 为什么要复位呢? (1)FPGA上电的时候对设计进行初始化: (2)使用一个外部管脚来实现全局复位,复位作为一个同步信号将所有存储单元设置为一个已知的状态 ...

- 你真的会Xilinx FPGA的复位吗?

Get Smart About Reset: Think Local, Not Global. 对于复位信号的处理,为了方便我们习惯上采用全局复位,博主在很长一段时间内都是将复位信号作为一个I/O口, ...

- Xilinx FPGA高速串行收发器简介

1 Overview 与传统的并行实现方法相比,基于串行I/O的设计具有很多优势,包括:器件引脚数较少.降低了板空间要求.印刷电路板(PCB)层数较少.可以轻松实现PCB设计.连接器较小.电磁干扰降低 ...

- xilinx FPGA全局时钟资源的使用

1.什么是xilinx fpga全局时钟资源 时钟对于一个系统的作用不言而喻,就像人体的心脏一样,如果系统时钟的抖动.延迟.偏移过大,会导致系统的工作频率降低,严重时甚至会导致系统的时序错乱,实现不了 ...

- 2-基于6U VPX的双TMS320C6678+Xilinx FPGA K7 XC7K420T的图像信号处理板

基于6U VPX的双TMS320C6678+Xilinx FPGA K7 XC7K420T的图像信号处理板 综合图像处理硬件平台包括图像信号处理板2块,视频处理板1块,主控板1块,电源板1块,VPX背 ...

- 330-支持PXIE带FMC接口的Xilinx FPGA XC7K325T PCIeX8 接口卡平台

支持PXIE带FMC接口的Xilinx FPGA XC7K325T PCIeX8 接口卡平台 一.板卡概述 本板卡基于Xilinx公司的FPGAXC7K325T-2FFG900 芯片,pin_ ...

随机推荐

- CSS-13-块级元素和行内元素

<!DOCTYPE html> <html> <head> <meta charset="UTF-8"> <title> ...

- Postwoman-接口测试工具

地址是:https://postwoman.io/ ,不过只能使用它们自己提供的测试接口,如果你调试自己的API接口的话,你需要自己部署一套代码. 自己搭建一套Postwomen环境的话,只需要安装了 ...

- 爬虫之协程,selenium

1.什么是代理?代理和爬虫之间的关联是什么? 2.在requests的get和post方法常用的参数有哪些?分别有什么作用?(四个参数) - url headers parmas/data proxi ...

- redis--->微博小项目

redis 微博小项目 centos6.9+lnmp+redis 写的微博小项目,梳理了redis在项目中kes的设计,redis各种数据结构在不同业务场景下的应用等知识点. 这里用的php框架是自己 ...

- 运行MapReduce任务

1:运行MapReduce任务 1:原始数据准备 统计用户的登录次数: 源数据login_log.txt如下: 7whygb5m@linshiyouxiang.net nuahvuhuoia@qq.c ...

- Kafka动态配置实现原理解析

问题导读 Apache Kafka在全球各个领域各大公司获得广泛使用,得益于它强大的功能和不断完善的生态.其中Kafka动态配置是一个比较高频好用的功能,下面我们就来一探究竟. 动态配置是如何设计的? ...

- 一次DB故障引起的反思和MySQL Operator选型

前言 在一次数据库故障后,我们发现业务库会根据业务的等级会划分多个 MySQL 实例,许多业务库会同时属于一个 MySQL 实例,当一个库引发问题后整个实例的状态是不可控的.从而导致这个实例上的所有业 ...

- 死磕java(2)

java数据类型 boolean --true--false byte --8位 short --16位 int --32位 long --64位 char float --32位 double -- ...

- selenium pyunit单元测试框架

selenium pyunit单元测试框架 #PyUnit框架 #coding = utf - 8 #将要被测试的类 class Widget: def __int__(self,size = (40 ...

- Codeforces_831

A.线性判断. #include<bits/stdc++.h> using namespace std; ] = {}; int main() { ios::sync_with_stdio ...