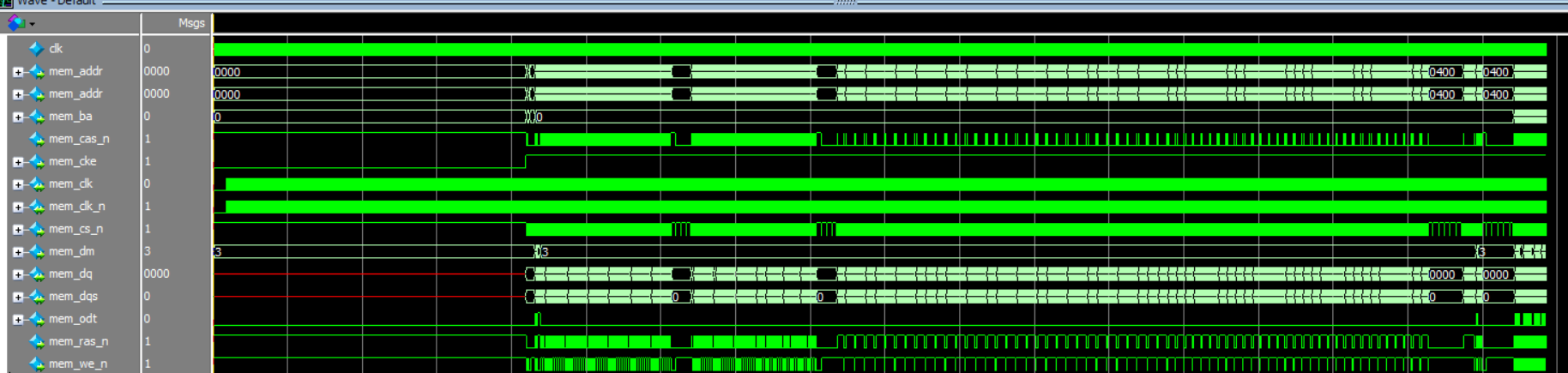

altera DDR2 IP核之仿真

20 -rw-r--r-- 1 Administrator 197121 17128 9月 8 15:41 alt_ddr2_ip_example_top_tb.v

20 -rw-r--r-- 1 Administrator 197121 17128 9月 8 15:41 alt_ddr2_ip_example_top_tb.v.tmp

28 -rw-r--r-- 1 Administrator 197121 25217 9月 8 15:41 alt_ddr2_ip_full_mem_model.v

28 -rw-r--r-- 1 Administrator 197121 25539 9月 8 15:41 alt_ddr2_ip_mem_model.v$ ll

total 6100

-rw-r--r-- 1 Administrator 197121 243144 9月 8 15:16 220model.v

-rw-r--r-- 1 Administrator 197121 2335095 9月 8 15:16 altera_mf.v

-rw-r--r-- 1 Administrator 197121 36404 9月 8 15:16 altera_primitives.v

-rw-r--r-- 1 Administrator 197121 261025 9月 8 15:16 cycloneiii_atoms.v

-rw-r--r-- 1 Administrator 197121 3329040 9月 8 15:16 cycloneiv_hssi_atoms.v

-rw-r--r-- 1 Administrator 197121 31314 9月 8 15:16 sgate.vvsim -l vsim.log -novopt +notimingcheck

-L altera_mf_ver \

-L lpm_ver \

-L sgate_ver \

-L cycloneiii_ver \

-L altera_ver \

work.$tbenchvlog -work work -sv -incr -93 -f vlog.f

vcom -work work -f vcom.f

altera DDR2 IP核之仿真的更多相关文章

- Altera DDR2 IP核学习总结3-----------DDR2 IP核的使用

根据上一篇生成的IP核,例化之后如上图,Local开头的数据是用户侧数据,其他数据暂时不用纠结,不用管. 这些是需要关注的信号,但是初学阶段很难对这些信号形成具体的概念,这里参考明德扬的代码进行二次封 ...

- Altera DDR2 IP核学习总结2-----------DDR2 IP核的生成

打开IP核工具,然后选择Verilog HDL选项,填写路径,写入文件名DDR2_IP.V,点击next PLL reference clock frequency填入板子晶振的频率50MHZ,这里设 ...

- Altera DDR2 IP核学习总结1-----------SRAM,DRAM

SRAM,DRAM,SDRAM和DDR2这些芯片详解网上铺天盖地的各种资料都有,这里只是根据个人习惯做一下总结,方便记忆. 详细资料可以参考https://wenku.baidu.com/view/3 ...

- 调用altera IP核的仿真流程—下

调用altera IP核的仿真流程—下 编译 在 WorkSpace 窗口的 counter_tst.v上点击右键,如果选择Compile selected 则编译选中的文件,Compile All是 ...

- 调用altera IP核的仿真流程—上

调用altera IP核的仿真流程—上 在学习本节内容之后,请详细阅读<基于modelsim-SE的简单仿真流程>,因为本节是基于<基于modelsim-SE的简单仿真流程>的 ...

- Altera三速以太网IP核快速仿真与使用(上篇)

对于比较高级的ip核,altera一般都会提供仿真案例,网上有关于这个IP核的各种仿真方法,但都比较繁琐,前几日,朋友跟我分享了一个比较快速高效的仿真方法,这个方法也是他摸索折腾了一段时间才总结出来的 ...

- 如何使用和了解ALTERA的IP核

可以通过直接对IP核进行仿真验证,通过波形来分析IP核的功能和工作方式,以及各个寄存器之间的工作关系. 也可以通过查看用户指导手册来学习IP核,如下图.

- Altera FIFO IP核时序说明

ALTERA在LPM(library of parameterized mudules)库中提供了参数可配置的单时钟FIFO(SCFIFO)和双时钟FIFO(DCFIFO).FIFO主要应用在需要数据 ...

- modelsim 独立仿真vivado的IP核及仿真脚本

Modelsim独立仿真vivado的IP 最近一直在做local dimming项目的FPGA硬件实现,算法的其中一步就是直方图统计,即数字图像的某一灰度级的像素数,这个直方图的源码找了半天才搞到, ...

随机推荐

- crontab下git命令无效

原因 crontab默认的 path 设置和系统自身的有区别 git 命令放在 /usr/local/bin/ 目录 whereis git 而crontab 却在 /sbin:/bin:/usr ...

- jmeter 获取登录token

1.在登录的请求下新建正则表达式,获取token 2.正则表达式的写法 注意:apply to 默认是选择第二个,但是有获取不到token的情况就选第一个 "accessToken" ...

- 请给Array本地对象增加一个原型方法,它用于删除数组条目中重复的条目(可能有多个),返回值是一个包含被删除的重复条目的新数组。

这是牛客网上的一道题~ 题意:遇到重复元素就删除(留下第一个不重复的即可). 解题思路:双循环一遍数组,arr[i] == arr[j] 成立时,删除 arr[j],并将 arr[j] 直接push到 ...

- CF285D.Permutation Sum

想了很久觉得自己做法肯定T啊,就算是CF机子的3s时限,但我毕竟是 O ( C(15,7)*7!*log ) .... 果然在n=15的点T了...贱兮兮地特判了15过掉了,结果发现题解说就是打表.. ...

- ubuntu18.04 配置chrome ss

为了FQ 不FQ不行啊 安装shaowsocks 1. 用实验室的服务器 sslocal -c xxx.json 2. 下载SwitchyOmega插件 链接: https://pan.baidu.c ...

- Python 汉诺塔

在汉诺塔游戏中,有三个分别命名为A.B.C得塔座,几个大小各不相同,从小到大一次编号得圆盘,每个原盘中间有一个小孔.最初,所有得圆盘都在A塔座上,其中最大得圆盘在最下面,然后是第二大,以此类推. 游戏 ...

- Linux主机安全配置规范

一.账号口令 1 配置口令最小长度 在文件/etc/login.defs中设置 PASS_MIN_LEN,参考值:8 2 配置口令生存周期 在文件/etc/login.defs中设置 ...

- 16路PWM输出的pca9685模块

今天要介绍的就是该模块,该模块是16路pwm模块,使用I2C总线可以控制16路舵机(led). 接线OE空着就可以,其他VCC是芯片供电+5,SCL时钟线,SDA信号线,GND地线. 芯片介绍可以看: ...

- git编译安装

因yum安装的git版本过低,所以尝试使用编译安装git 以下为编译安装时执行的命令 tar xf git-2.9.5.tar.gz cd git-2.9.5yum install curl-deve ...

- JNI加载hal的dlopen()相关操作

1.函数集合 #include <dlfcn.h> void *dlopen(const char *filename, int flag); char *dlerror(void); v ...