基于Verilog HDL 的数字时钟设计

基于Verilog HDL的数字时钟设计

一、实验内容:

利用FPGA实现数字时钟设计,附带秒表功能及时间设置功能。时间设置由开关S1和S2控制,分别是增和减。开关S3是模式选择:0是正常时钟显示;1是进入调分模式;2是进入调时模式;3是进入秒表模式,当进入秒表模式时,S1具有启动和停止功能,S2具有复位归零功能。只有四位数码管,所以没有做万年历,下一步会在这个基础上加入定时闹钟。

二、实验板

自个制作的实验板,用的是Altera CycloneIII EP3C40Q240C8N。上面的这块板是简单的外围电路,有流水灯、EEPROM、蜂鸣器、MAX3232、拨码开关、开关按键。PS2解码、VGA、AD转换等外围电路正在筹划中。

二、实验原理图设计

1、数码管原理图:利用74HC245驱动7段共阴极数码,其中F_X是代表接入到FPGA的I/O口。

2、开关原理图

三、整体架构设计

1、模块结构

2、RTL Viewer

四、各个击破

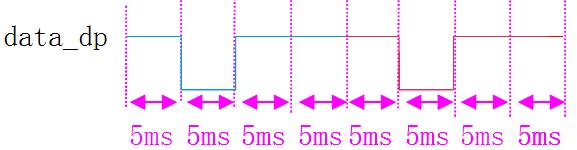

第1步:数码管显示,四位数码管的a~g、dp都是复用的,得先让四位数码管能分别显示不同的数据。大家都应该想到了“同步动态扫描”。我是这样做的:每位数码工作5ms,并采取流水方式进行循环操作(列扫描),每位数码即将工作那一刻,同时给a~g送入数据,数据保留5ms并进行定时更新数据(行扫描),行与列保持同步。定时开关,定时发送数据。下图有点错误,其实是在低电平是有效的,高低电平反了。

第2步:小数点显示,为了与时钟显示格式更为逼真,让中间的小数点一直亮着(充分利用资源吧),其他小数点要灭掉,很不幸运,不能直接把data_dp管脚直接拉高或拉低,这里是给该管脚产生周期为20ms,占空比为3/4的一个时钟信号,下图高低电平反了。

第3步:要让不同数码显示不同数据,那么就得事先编好每位数码管要显示的数据。由于时钟与秒表显示的最大数据不一样,得单独编码,这步很简单,一看代码就知道。

第4步:开关的信号输入,涉及到开关,那么就得消抖。这里借鉴特权的方法实现的。

把要做的实验思路搞清楚后,那么数字时钟设计应该很快就会完成。

五、各模块的信号输入/输出定义

|

Setting.v |

||

|

Pin Name |

I/O |

Description |

|

clk |

input |

主时钟27MHZ |

|

rst_n |

input |

系统复位,低有效 |

|

add_in |

input |

开关S1的输入 |

|

sub_in |

input |

开关S2的输入 |

|

model_in |

input |

开关S3的输入 |

|

Hour_Ten |

output |

时的十位 |

|

Hour_One |

output |

时的个位 |

|

Minute_Ten |

output |

分的十位 |

|

Minute_One |

output |

分的个位 |

|

Display_Model |

output |

控制时钟与秒表的显示切换 |

|

M_Start |

output |

启动/停止秒表计数器 |

|

M_Reset |

output |

复位归零 |

|

control_wei.v |

||

|

Pin Name |

I/O |

Description |

|

clk |

input |

主时钟27MHZ |

|

rst_n |

input |

系统复位,低有效 |

|

select_wei |

output |

控制数码管流水工作 |

|

miaobiao.v |

||

|

Pin Name |

I/O |

Description |

|

clk |

input |

主时钟27MHZ |

|

rst_n |

input |

系统复位,低有效 |

|

M_Start |

input |

启动/停止秒表计数器 |

|

M_Reset |

input |

复位归零 |

|

S_data1 |

output |

秒表:第一位数码管数据编码 |

|

S_data2 |

output |

秒表:第二位数码管数据编码 |

|

S_data3 |

output |

秒表:第三位数码管数据编码 |

|

S_data4 |

output |

秒表:第四位数码管数据编码 |

|

control_display.v |

|||

|

Pin Name |

I/O |

Description |

|

|

clk |

input |

主时钟27MHZ |

|

|

rst_n |

input |

系统复位,低有效 |

|

|

H_data1 |

input |

时钟:第一位数码管数据 |

|

|

H_data2 |

|

时钟:第二位数码管数据 |

|

|

H_data3 |

input |

时钟:第三位数码管数据 |

|

|

H_data4 |

input |

时钟:第四位数码管数据 |

|

|

S_data1 |

input |

秒表:第一位数码管数据 |

|

|

S_data2 |

input |

秒表:第二位数码管数据 |

|

|

S_data3 |

input |

秒表:第三位数码管数据 |

|

|

S_data4 |

input |

秒表:第四位数码管数据 |

|

|

Display_Model |

input |

控制时钟与秒表的显示切换 |

|

|

data |

output |

送出7段a~g数据 |

|

|

data_dp |

output |

小数点 |

|

|

clock_top.v |

||

|

Pin Name |

I/O |

Description |

|

clk |

input |

主时钟27MHZ |

|

rst_n |

input |

系统复位,低有效 |

|

add_in |

input |

开关S1的输入 |

|

sub_in |

input |

开关S2的输入 |

|

model_in |

input |

开关S3的输入 |

|

data |

output |

送出7段a~g数据 |

|

select_wei |

output |

控制数码管流水工作 |

|

data_dp |

output |

小数点 |

六:代码的实现

control_wei.v

/***********************************************/

//四位数码管进行流水控制,每位数码管工作5MS

/***********************************************/

module control_wei(

clk,

rst_n,

select_wei,

);

input clk;

input rst_n;

output[:] select_wei; /**********************************************/

parameter T5MS = 'd134_999;

/**********************************************/

reg[:] select_wei;

reg[:] cnt;

always @(posedge clk or negedge rst_n)

if(!rst_n) cnt <= 'd0;

else if(cnt == T5MS)

cnt <= 'd0;

else

cnt <= cnt + 'b1;

/**********************************************/

//通过移位方式进行流水工作,定时开关

always @(posedge clk or negedge rst_n)

if(!rst_n) begin

select_wei <= 'd7;

end

else if(cnt == T5MS) begin

if(select_wei == 'd14)

select_wei <= 'd7;

else

select_wei <= {'b1,select_wei[3:1]};

end

endmodule

setting.v

module setting(

//input

clk,

rst_n,

add_in,//增加按钮

sub_in,//减去按钮

model_in,//模式选择 //output

Hour_Ten,

Hour_One,

Minute_Ten,

Minute_One,

Display_Model,

M_Start,

M_Reset,

);

input clk;

input rst_n;

input add_in;

input sub_in;

input model_in; output [:] Hour_Ten;

output [:] Hour_One;

output [:] Minute_Ten;

output [:] Minute_One;

output Display_Model;

output M_Start;

output M_Reset; /************************************/

parameter T20MS = 'd539_999;

parameter T1S = 'd26_999_999;

parameter T60S = 'd1_619_999_999;

/************************************************/

//检测下降沿脉冲key_en = key_rst_r & (~key_rst);

//key_rst_r要晚一个时钟节拍才能得到key_rst的值

//key_rst在1变为0时,key_en置位

//key_rst 1 1 0 1 1

//key_rst_r 1 1 0 1 1

//~key_rst 0 0 1 0 0

//--------------------------

//key_en 0 0 1 0 0 //检测上升沿脉冲key_en = (~key_rst_r) & key_rst;

//key_rst在0变为1时,key_en置位

//key_rst 0 0 1 0 0

//key_rst_r 0 0 1 0 0 //key_rst 0 0 1 0 0

//~key_rst_r 1 1 0 1 1

//--------------------------

//key_en 0 0 1 0 0

/************************************************/

reg[:] key_rst;

always @(posedge clk or negedge rst_n)

if(!rst_n) key_rst <= 'b111;

else key_rst <= {add_in,sub_in,model_in}; reg[:] key_rst_r;

always @(posedge clk or negedge rst_n)

if(!rst_n) key_rst_r <= 'b111;

else key_rst_r <= key_rst; wire[:] key_en;

assign key_en = key_rst_r & (~key_rst);

/************************************************/

//按键消抖动

/************************************************/

reg[:] cnt;

always @(posedge clk or negedge rst_n)

if(!rst_n) cnt <= 'd0;

else if(key_en) cnt <= 'd0;

else cnt <= cnt + 'b1;

//每隔20ms就取按键上的值

reg[:] pin_status;

always @(posedge clk or negedge rst_n)

if(!rst_n) pin_status <= 'b111;

else if(cnt == T20MS) pin_status <= {add_in,sub_in,model_in}; reg[:] pin_status_r;

always @(posedge clk or negedge rst_n)

if(!rst_n) pin_status_r <= 'b111;

else pin_status_r <= pin_status;

//前20MS的值与后20MS的值

wire[:] pin_status_ctrl;

assign pin_status_ctrl = pin_status_r & (~pin_status); /**************************************************************************************************/

//60S计数器

reg [:] cnt60s;

always @(posedge clk or negedge rst_n)

if(!rst_n) cnt60s <= 'd0;

else if((cnt60s == T60S) || (!isCount)) cnt60s <= 'd0;

else if(isCount)

cnt60s <= cnt60s + 'b1;

/**************************************************************************************************/

//模式控制

//00:时钟正常跑模式

//01:调分模式,在该模式时间计数器停止计数

//10: 调时模式,在该模式时间计数器停止计数

//11:秒表模式,在该模式时间计数器正常计数

reg[:] Time_model;

always @(posedge clk or negedge rst_n)

if(!rst_n) Time_model <= 'b00;

else if(pin_status_ctrl[])

begin

if(Time_model == 'b11)

Time_model <= 'b00;

else

Time_model <= Time_model + 'b1;

end /************************************************/

reg Display_Model;//时钟与秒表显示

reg isCount;//控制时间计数器

reg M_Start;//控制秒表计数器

reg M_Reset;//秒表复位

reg M_flag;//开关S1按第一次代表启动,紧接在按一次代表停止

reg [:] flag;//用来标志reg1是否到了2,到了2,reg2只能加到4

reg [:] reg1;//时的第一位:0~2

reg [:] reg2;//时的第二位:当第一位为0和1时,可以是0~9,当第一位为2时,只能是0~9,

reg [:] reg3;//分的第一位:只能是0~5

reg [:] reg4;//分的第二位:是0~9

always @(posedge clk or negedge rst_n)

if(!rst_n) begin

Display_Model <= 'b0;

isCount <= 'b0;

M_Start <= 'b0;

M_Reset <= 'b0;

M_flag <= 'b0;

reg1 <= 'd0;

reg2 <= 'd0;

reg3 <= 'd0;

reg4 <= 'd0;

flag <= 'd0;

end

else

case(Time_model)

//时钟正常开始跑

'b00:

begin

Display_Model <= 'b0;

isCount <= 'b1;//启动计数

if(cnt60s == T60S)

begin

reg4 <= reg4 + 'b1;

if(reg4 == 'd9)

begin

reg4 <= 'd0;

reg3 <= reg3 + 'b1;

if(reg3 == 'd5)

begin

reg3 <= 'd0;

if(reg1 == 'd2)

begin

reg2 <= reg2 + 'b1;

if(reg2 == 'd3)

begin

reg2 <= 'd0;

reg1 <= 'd0;

end

end

else

begin

reg2 <= reg2 + 'b1;

if(reg2 == 'd9)

begin

reg2 <= 'd0;

reg1 <= reg1 + 'b1;

end

end

end end

end

end //调分模式

'b01:

begin

isCount <= 'b1;

if(pin_status_ctrl[])//加

begin

reg4 <= reg4 + 'b1;

if(reg4 == 'd9)

begin

reg4 <= 'd0;

reg3 <= reg3 + 'b1;

if(reg3 > 'd5)

reg3 <= 'd0;

end

end

else if(pin_status_ctrl[])//减

begin

reg4 <= reg4 - 'b1;

if(reg4 == 'd0)

begin

reg4 <= 'd9;

reg3 <= reg3 - 'b1;

if(reg3 == 'd5)

reg3 <= 'd0;

end

end

end //调时模式

'b10:

begin

isCount <= 'b1;

if(pin_status_ctrl[])//加

begin

if(flag == 'd2)

begin

reg2 <= reg2 + 'b1;

if(reg2 >= 'd3)

begin

reg2 <= 'd0;

reg1 <= 'd0;

flag <= 'd0;

end

end

else

begin

reg2 <= reg2 + 'b1;

if(reg2 == 'd9)

begin

flag <= flag + 'b1;

reg2 <= 'd0;

reg1 <= reg1 + 'b1;

if(reg1 == 'd2)

begin

reg1 <= 'd0;

end

end

end

end

else if(pin_status_ctrl[])//减

begin

reg2 <= reg2 - 'b1;

if(reg2 == 'd0)

begin

reg2 <= 'd9;

reg1 <= reg1 - 'b1;

if(reg1 == 'd2)

reg1 <= 'd0;

end

end

end 'b11:begin

isCount <= 'b1;//时间计数还得继续接着跑

Display_Model <= 'b1;//显示秒表

if(pin_status_ctrl[])//启动秒表计数

begin

if(M_flag == 'b1) begin

M_flag <= 'b0;

M_Start <= 'b0;

end

else begin

M_flag <= M_flag + 'b1;

M_Start <= 'b1;

M_Reset <= 'b0; end

end

else if(pin_status_ctrl[])//复位并停止

begin

M_Start <= 'b0;

M_flag <= 'b0;

M_Reset <= 'b1;

end

end

endcase

/************************************************/

assign Hour_Ten = reg1;

assign Hour_One = reg2;

assign Minute_Ten = reg3;

assign Minute_One = reg4;

/************************************************/ endmodule

control_data.v

module control_data(

//input

clk,

rst_n,

Hour_Ten,

Hour_One,

Minute_Ten,

Minute_One, //output

H_data1,

H_data2,

H_data3,

H_data4

);

input clk;

input rst_n;

input [:] Hour_Ten;

input [:] Hour_One;

input [:] Minute_Ten;

input [:] Minute_One;

output [:] H_data1;

output [:] H_data2;

output [:] H_data3;

output [:] H_data4;

/***********************************/

parameter SEG_NUM0 = 'h3f,//c0,

SEG_NUM1 = 'h06,//f9,

SEG_NUM2 = 'h5b,//a4,

SEG_NUM3 = 'h4f,//b0,

SEG_NUM4 = 'h66,//99,

SEG_NUM5 = 'h6d,//92,

SEG_NUM6 = 'h7d,//82,

SEG_NUM7 = 'h07,//F8,

SEG_NUM8 = 'h7f,//80,

SEG_NUM9 = 'h6f;//90,

/***********************************/

//时钟数据编码

/***********************************/

//数码管一要显示的列表数据(0~2)

reg [:] data1_temp;

always @(posedge clk or negedge rst_n)

if(!rst_n)

data1_temp <= 'h3f;

else

case(Hour_Ten)

'd0: data1_temp <= SEG_NUM0;

'd1: data1_temp <= SEG_NUM1;

'd2: data1_temp <= SEG_NUM2;

default: data1_temp <= SEG_NUM0;

endcase

/***********************************/

//数码管二要显示的列表数据(0~9)

reg [:] data2_temp;

always @(posedge clk or negedge rst_n)

if(!rst_n)

data2_temp <= 'h3f;

else

case(Hour_One)

'd0: data2_temp <= SEG_NUM0;

'd1: data2_temp <= SEG_NUM1;

'd2: data2_temp <= SEG_NUM2;

'd3: data2_temp <= SEG_NUM3;

'd4: data2_temp <= SEG_NUM4;

'd5: data2_temp <= SEG_NUM5;

'd6: data2_temp <= SEG_NUM6;

'd7: data2_temp <= SEG_NUM7;

'd8: data2_temp <= SEG_NUM8;

'd9: data2_temp <= SEG_NUM9;

default: data2_temp <= SEG_NUM0;

endcase

/***********************************/

//数码管三要显示的列表数据 (0~5)

reg [:] data3_temp;

always @(posedge clk or negedge rst_n)

if(!rst_n)

data3_temp <= 'h3f;

else

case(Minute_Ten)

'd0: data3_temp <= SEG_NUM0;

'd1: data3_temp <= SEG_NUM1;

'd2: data3_temp <= SEG_NUM2;

'd3: data3_temp <= SEG_NUM3;

'd4: data3_temp <= SEG_NUM4;

'd5: data3_temp <= SEG_NUM5;

default: data3_temp <= SEG_NUM0;

endcase

/***********************************/

//数码管四要显示的列表数据(1~9)

reg [:] data4_temp;

always @(posedge clk or negedge rst_n)

if(!rst_n)

data4_temp <= 'h3f;

else

case(Minute_One)

'd0: data4_temp <= SEG_NUM0;

'd1: data4_temp <= SEG_NUM1;

'd2: data4_temp <= SEG_NUM2;

'd3: data4_temp <= SEG_NUM3;

'd4: data4_temp <= SEG_NUM4;

'd5: data4_temp <= SEG_NUM5;

'd6: data4_temp <= SEG_NUM6;

'd7: data4_temp <= SEG_NUM7;

'd8: data4_temp <= SEG_NUM8;

'd9: data4_temp <= SEG_NUM9;

default: data4_temp <= SEG_NUM0;

endcase

/*****************************************/

assign H_data1 = data1_temp;

assign H_data2 = data2_temp;

assign H_data3 = data3_temp;

assign H_data4 = data4_temp;

/*****************************************/

endmodule

control_display.v

module control_display(

//input

clk,

rst_n,

H_data1,

H_data2,

H_data3,

H_data4, S_data1,

S_data2,

S_data3,

S_data4, Display_Model, //output

data,

data_dp

);

input clk;

input rst_n;

//时钟模式要显示数据

input [:] H_data1;

input [:] H_data2;

input [:] H_data3;

input [:] H_data4;

//秒表模式要显示数据

input [:] S_data1;

input [:] S_data2;

input [:] S_data3;

input [:] S_data4;

input Display_Model;//0:时钟模式,1:秒表模式 output [:] data;//不包括小数点

output data_dp;

/******************************************/

parameter T5MS = 'd134_999;

parameter T10MS = 'd269_999;

parameter T20MS = 'd539_999;

/****************************************************************/

reg [:]cnt_ms;

always @(posedge clk or negedge rst_n)

if(!rst_n)

cnt_ms <= 'd0;

else if(cnt_ms == T20MS)

cnt_ms <= 'd0;

else

cnt_ms <= cnt_ms + 'b1; /****************************************************************/

//小数点显示

reg [:] i;

reg data_dp;

always @(posedge clk or negedge rst_n)

if(!rst_n)

i <= 'd0;

else

case(i)

'd0:

if(cnt_ms != T5MS)

data_dp = 'b0;

else begin

data_dp= 'b1;

i <= i + 'b1;

end 'd1:

if(cnt_ms != T10MS)

data_dp = 'b1;

else begin

data_dp <= 'b0;

i <= i + 'b1;

end 'd2:

if(cnt_ms != T20MS)

data_dp <= 'b0;

else

i <= 'd0;

endcase

/******************************************/

//定时发送数据

reg [:] cnt;

reg [:] num;//每隔5MS,num加1

always @(posedge clk or negedge rst_n)

if(!rst_n) begin

cnt <= 'd0;

num <= 'd0;

end

else if(cnt == T5MS) begin

num <= num + 'b1;

cnt <= 'd0;

end

else

cnt <= cnt + 'b1;

/******************************************/

//通过Display_Model来确定是要送秒表数据还是时钟数据

reg [:] data_temp;

always @(posedge clk or negedge rst_n)

if(!rst_n)

data_temp <= 'h3f;

else

case(num)

'd0: data_temp <= Display_Model ? S_data1:H_data1;//给第一个数码管送数据

'd1: data_temp <= Display_Model ? S_data2:H_data2;//给第二个数码管送数据

'd2: data_temp <= Display_Model ? S_data3:H_data3;//给第二个数码管送数据

'd3: data_temp <= Display_Model ? S_data4:H_data4;//给第二个数码管送数据

endcase

/******************************************/

assign data = data_temp;

/******************************************/

endmodule

miaobiao.v

module miaobiao(

//input

clk,

rst_n,

M_Start,

M_Reset, //ouput

S_data1,

S_data2,

S_data3,

S_data4

);

input clk;

input rst_n;

input M_Start;//控制秒表计数器

input M_Reset;//秒表复位

output [:] S_data1;

output [:] S_data2;

output [:] S_data3;

output [:] S_data4; /************************************************************/

parameter T_fenMiao = 'd269_999;

parameter SEG_NUM0 = 'h3f,//c0,

SEG_NUM1 = 'h06,//f9,

SEG_NUM2 = 'h5b,//a4,

SEG_NUM3 = 'h4f,//b0,

SEG_NUM4 = 'h66,//99,

SEG_NUM5 = 'h6d,//92,

SEG_NUM6 = 'h7d,//82,

SEG_NUM7 = 'h07,//F8,

SEG_NUM8 = 'h7f,//80,

SEG_NUM9 = 'h6f;//90,

/************************************************************/

//分秒计数器

reg [:] Cnt_FenMiao;

always @(posedge clk or negedge rst_n)

if(!rst_n) Cnt_FenMiao <= 'd0;

else if((Cnt_FenMiao == T_fenMiao) || (!M_Start)) Cnt_FenMiao <= 'd0;

else if(M_Start)

Cnt_FenMiao <= Cnt_FenMiao + 'b1;

/************************************************************/

//分秒向秒进位

reg [:] reg1;

reg [:] reg2;

reg [:] reg3;

reg [:] reg4;

always @(posedge clk or negedge rst_n)

if(!rst_n) begin

reg1 <= 'd0;

reg2 <= 'd0;

reg3 <= 'd0;

reg4 <= 'd0;

end

else if(M_Reset) begin

reg1 <= 'd0;

reg2 <= 'd0;

reg3 <= 'd0;

reg4 <= 'd0;

end

else if(Cnt_FenMiao == T_fenMiao)

begin

if(reg4 == 'd9) begin

reg4 <= 'd0;

if(reg3 == 'd9) begin

reg3 <= 'd0;

if(reg2 == 'd9) begin

reg2 <= 'd0;

if(reg1 == 'd5)

reg1 <= 'd0;

else reg1 <= reg1 + 'b1;

end

else

reg2 <= reg2 + 'b1;

end

else

reg3 <= reg3 + 'b1;

end

else

reg4 <= reg4 + 'b1;

end

/************************************************************/

//数据编码

/************************************************************/

//数码管一要显示的列表数据(0~5)

reg [:] S_data1_temp;

always @(posedge clk or negedge rst_n)

if(!rst_n) S_data1_temp <= 'h3f;

else

case(reg1)

'd0: S_data1_temp <= SEG_NUM0;

'd1: S_data1_temp <= SEG_NUM1;

'd2: S_data1_temp <= SEG_NUM2;

'd3: S_data1_temp <= SEG_NUM3;

'd4: S_data1_temp <= SEG_NUM4;

'd5: S_data1_temp <= SEG_NUM5;

default: S_data1_temp <= SEG_NUM0;

endcase

/***********************************/

//数码管二要显示的列表数据(0~9)

reg [:] S_data2_temp;

always @(posedge clk or negedge rst_n)

if(!rst_n) S_data2_temp <= 'h3f;

else

case(reg2)

'd0: S_data2_temp <= SEG_NUM0;

'd1: S_data2_temp <= SEG_NUM1;

'd2: S_data2_temp <= SEG_NUM2;

'd3: S_data2_temp <= SEG_NUM3;

'd4: S_data2_temp <= SEG_NUM4;

'd5: S_data2_temp <= SEG_NUM5;

'd6: S_data2_temp <= SEG_NUM6;

'd7: S_data2_temp <= SEG_NUM7;

'd8: S_data2_temp <= SEG_NUM8;

'd9: S_data2_temp <= SEG_NUM9;

default: S_data2_temp <= SEG_NUM0;

endcase

/*****************************************/

//数码管三要显示的列表数据(0~9)

reg [:] S_data3_temp;

always @(posedge clk or negedge rst_n)

if(!rst_n) S_data3_temp <= 'h3f;

else

case(reg3)

'd0: S_data3_temp <= SEG_NUM0;

'd1: S_data3_temp <= SEG_NUM1;

'd2: S_data3_temp <= SEG_NUM2;

'd3: S_data3_temp <= SEG_NUM3;

'd4: S_data3_temp <= SEG_NUM4;

'd5: S_data3_temp <= SEG_NUM5;

'd6: S_data3_temp <= SEG_NUM6;

'd7: S_data3_temp <= SEG_NUM7;

'd8: S_data3_temp <= SEG_NUM8;

'd9: S_data3_temp <= SEG_NUM9;

default: S_data3_temp <= SEG_NUM0;

endcase

/***********************************/

//数码管四要显示的列表数据(0~9)

reg [:] S_data4_temp;

always @(posedge clk or negedge rst_n)

if(!rst_n) S_data4_temp <= 'h3f;

else

case(reg4)

'd0: S_data4_temp <= SEG_NUM0;

'd1: S_data4_temp <= SEG_NUM1;

'd2: S_data4_temp <= SEG_NUM2;

'd3: S_data4_temp <= SEG_NUM3;

'd4: S_data4_temp <= SEG_NUM4;

'd5: S_data4_temp <= SEG_NUM5;

'd6: S_data4_temp <= SEG_NUM6;

'd7: S_data4_temp <= SEG_NUM7;

'd8: S_data4_temp <= SEG_NUM8;

'd9: S_data4_temp <= SEG_NUM9;

default: S_data4_temp <= SEG_NUM0;

endcase

/*******************************************************/

assign S_data1 = S_data1_temp;

assign S_data2 = S_data2_temp;

assign S_data3 = S_data3_temp;

assign S_data4 = S_data4_temp;

/*******************************************************/

endmodule

clock_top

module clock_top(

//input

clk,

rst_n,

add_in,

sub_in,

model_in, //output

data,

select_wei,

data_dp,

);

input clk;

input rst_n;

input add_in;

input sub_in;

input model_in; output [:] data;

output [:] select_wei;

output data_dp; wire [:] Hour_Ten;

wire [:] Hour_One;

wire [:] Minute_Ten;

wire [:] Minute_One;

wire [:] H_data1,H_data2,H_data3,H_data4;

wire [:] S_data1,S_data2,S_data3,S_data4;

wire Display_Model;

wire M_Start;

wire M_Reset; control_wei U1(

//input

.clk(clk),

.rst_n(rst_n), //output

.select_wei(select_wei),

); setting U2(

//input

.clk(clk),

.rst_n(rst_n),

.add_in(add_in),//增加按钮

.sub_in(sub_in),//减去按钮

.model_in(model_in),//模式选择 //output

.Hour_Ten(Hour_Ten),

.Hour_One(Hour_One),

.Minute_Ten(Minute_Ten),

.Minute_One(Minute_One),

.Display_Model(Display_Model),

.M_Start(M_Start),

.M_Reset(M_Reset),

); control_data U3(

//input

.clk(clk),

.rst_n(rst_n),

.Hour_Ten(Hour_Ten),//from to U2

.Hour_One(Hour_One),//from to U2

.Minute_Ten(Minute_Ten),//from to U2

.Minute_One(Minute_One),//from to U2 //output

.H_data1(H_data1),

.H_data2(H_data2),

.H_data3(H_data3),

.H_data4(H_data4)

); control_display U4(

//input

.clk(clk),

.rst_n(rst_n),

.H_data1(H_data1),//from to U3

.H_data2(H_data2),//from to U3

.H_data3(H_data3),//from to U3

.H_data4(H_data4),//from to U3

.S_data1(S_data1),//from to U5

.S_data2(S_data2),//from to U5

.S_data3(S_data3),//from to U5

.S_data4(S_data4),//from to U5

.Display_Model(Display_Model),//from to U2 //output

.data(data),

.data_dp(data_dp)

); miaobiao U5(

//input

.clk(clk),

.rst_n(rst_n),

.M_Start(M_Start),//from to U2

.M_Reset(M_Reset),//from to U2 //ouput

.S_data1(S_data1),

.S_data2(S_data2),

.S_data3(S_data3),

.S_data4(S_data4),

);

endmodule

基于Verilog HDL 的数字时钟设计的更多相关文章

- 基于Verilog HDL 各种实验

菜鸟做的的小实验链接汇总: 1.基于Verilog HDL 的数字时钟设计 2.乘法器 3.触发器(基本的SR触发器.同步触发器.D触发器) 4.基于Verilog HDL的ADC ...

- 基于Verilog HDL整数乘法器设计与仿真验证

基于Verilog HDL整数乘法器设计与仿真验证 1.预备知识 整数分为短整数,中整数,长整数,本文只涉及到短整数.短整数:占用一个字节空间,8位,其中最高位为符号位(最高位为1表示为负数,最高位为 ...

- 基于Verilog HDL 的数字电压表设计

本次实验是在“基于Verilog HDL的ADC0809CCN数据采样”实验上进一步改进,利用ADC0809采集到的8位数据,进行BCD编码,以供查表方式相加进行显示,本次实验用三位数码管. ADC0 ...

- 基于FPGA的简易数字时钟

基于FPGA的可显示数字时钟,设计思路为自底向上,包含三个子模块:时钟模块,进制转换模块.led显示模块.所用到的FPGA晶振频率为50Mhz,首先利用它得到1hz的时钟然后然后得到时钟模块.把时钟模 ...

- VHDL 数字时钟设计

序言 这个是我在做FPGA界的HelloWorld--数字钟设计时随手写下的,再现了数字钟设计的过程 目标分析 时钟具有时分秒的显示,需6个数码管.为了减小功耗采用扫描法显示 按键设置时间,需要对按键 ...

- 基于Verilog HDL的超前进位全加器设计

通常我们所使用的加法器一般是串行进位,将从输入的ci逐位进位地传递到最高位的进位输出co,由于电路是有延迟的,这样的长途旅行是需要时间的,所以为了加快加法器的运算,引入了超前进位全加器. 全加器的两个 ...

- paper:基于verilog HDL 的高速可综合FSM设计

1.寄存器输出型状态机 VS 组合逻辑输出型状态机 2.状态编码方法 这块讲的不好,也比较少. 3.系统设计中模块划分的指导性原则

- 基于Verilog HDL的二进制转BCD码实现

在项目设计中,经常需要显示一些数值,比如温湿度,时间等等.在数字电路中数据都是用二进制的形式存储,要想显示就需要进行转换,对于一个两位的数值,对10取除可以得到其十位的数值,对10取余可以得到个位的数 ...

- 基于Verilog HDL的ADC0809CCN数据采样

本实验是用ADC0809CCN进行数据采样,并用7段数码管进行显示. ADC0809由一个8路模拟开关.一个地址锁存与译码器.一个A/D转换器和一个三态输出锁存器组成.多路开关可选通8个模拟通道,允许 ...

随机推荐

- Linux下开启nfs服务

1.什么是NFS(Network FileSystem) NFS 就是 Network FileSystem 的缩写,最早之前是由 Sun 所发展出来的.他最大的功能就是可以透过网络,让不同的机器.不 ...

- LeetCode OJ 108. Convert Sorted Array to Binary Search Tree

Given an array where elements are sorted in ascending order, convert it to a height balanced BST. 把一 ...

- 购物车(Shopping cart) —— B2C网站核心产品设计 (二)

购物车是做什么的? 我们先来看一下现实超市中的购物车,一个带四个轱辘的铁筐子,客人推来推去,看到什么东西喜欢,就扔进去,觉得东西差不多了,就推到收银台. 那B2C网站中的购物车又是一个什么东西呢? 从 ...

- app调用支付宝支付 笔记

1.提交各种申请 2.通过后进入支付宝开放平台 --> 管理中心 -->创建应用 --> 填写相关信息 提交等待审核通过(1,2天) 3.下载集成包(https://doc. ...

- 全选js实现

前端全选框 <input type='checkbox' name='allSelect' onclick='sel(this)'></input> //有i个选择框 < ...

- oracle数据库字符集的修改

本文摘自:http://blog.csdn.net/nsj820/article/details/65711051.改客户端字符集:通过WINDOWS的运行菜单运行Regedit,修改注册表 Star ...

- NoSql的产生

主流的关系型数据库:Microsoft SQLServer, IBM DB2, Oracle, MySQL, Microsoft Access, Sybase,IBM Informix 随着互联网we ...

- Hibernate 系列教程6-双向多对多

双向多对多inverse配置 如果关系两边都使用默认inverse=false配置,表示关系两边都可以管理中间表的数据 关系其中一边设置inverse=true配置,表示自己放弃管理中间表关系,由对方 ...

- IDL和生成代码分析

IDL:接口描述语言 这里使用thrift-0.8.0-xsb这个版本来介绍IDL的定义以及简单实例分析. 1. namespace 定义包名 2.struct 结构体,定义服务接口的参数和返回值用到 ...

- NSTimer内存方面的探究

今天研究一个框架,看到它对NSTimer的处理,感觉很有意思.于是自己在各种情况下都研究了一下,现总结如下. 我们用到NSTimer时,似乎习惯于会在dealloc方法中把它invalidate掉,但 ...