ARM Cortex Design Considerations for Debug

JTAG was the traditional mechanism for debug connections for ARM7/9 parts, but with the Cortex-M family, ARM introduced the Serial Wire Debug (SWD) Interface. SWD is designed to reduce the pin count required for debug from the 5 used by JTAG (including GND) down to 3. In addition, one of the pins freed up by this can be used for the low cost SWO tracing technology - for more details see the FAQ "Overview of Trace support in LPCXpresso IDE".

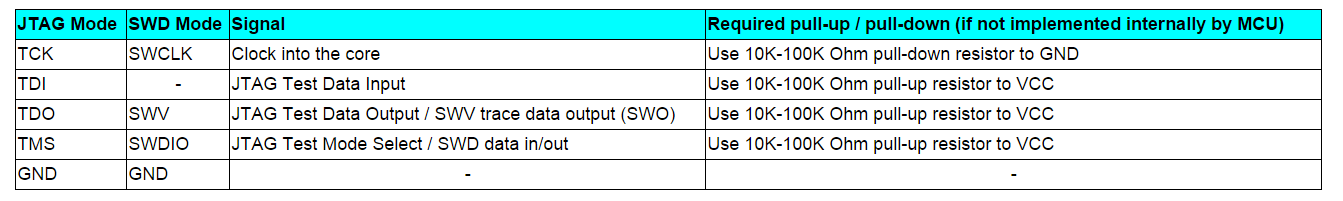

The SWD/SWV pins are overlaid on top of the JTAG pins as follows:

Some MCUs do not include internal pull-up or pull-down resistors on JTAG/SWD pins. You will need to review the datasheet for the specific MCU being used to confirm. Where internal resistors are not provided, these should be added externally onto your board as detailed above. You may use resistors between 10K and 100K for these signals. This will prevent the signals from floating when they are not connected to anything. Failure to do this will lead to, at best, unreliable debug connections, or more likely no ability to debug at all.

If an internal resistor is provided for a pin by the MCU, then an external resistor is not required for that pin. But if external resistor is provided in such cases, then it must match that provided internally by the MCU.

Note for TCK/SWCLK, although a pull-down is recommended, you can alternatively use a pull-up. The main thing is that it does not float. Note in particular that if the MCU provides an internal pull-up on this signal, then adding an external pull-down on the board is not recommended.

Note that Cortex-M0/M0+ parts does not support SWV trace.

Other important debug related signals

When designing your board, you should also take the following signals into account for debug purposes. Failure to do this will lead to, at best, unreliable debug connections, or more likely no ability to debug at all.

- RESET

- Connect this pin to the (active low) reset input of the target MCU

- We would strongly recommend also including RESET in addition to SWDIO, CLK and GND. For debugging, the tools may try to pull this in certain circumstances (depending upon debug probe, debug configuration settings and tools).

- ISP

- Most NXP MCU's have an ISP pin which (when pulled low) can be used to cause the MCU to enter a bootloader on reset.

- For example on LPC17xx this is P2.10 and on LPC11xx and LPC13xx it is P0.1.

- Always ensure that you have a 10K to 100K Ohm pull up resistor on the ISP pin, otherwise you are unlikely to be able to make a successful debug connection.

- VTref

- The Voltage Target Reference pin supplies some debug probes (such as LPC-Link2) with the debug rail voltage of the target to match its I/O logic level. For more information, see "Logic Levels and Ground" below.

- RTCK, DBGSEL

- Some NXP LPC2000 devices have special pins that enable the JTAG interface. For example, on the NXP LPC2129 the signal RTCK must be driven low during RESET to enable the JTAG interface. You may want to add jumpers to your hardware to accomplish this.

Logic Levels and Ground

VTref (the Voltage Target Reference pin, direction from target to debug probe) supplies some debug probes such as LPC-Link2 and Red Probe+ with the debug rail voltage of the target to match its I/O logic level. VTref can be tied directly to the target VDDIO rail or through a resistor. If VTref is tied high through a resistor, its value must be no greater than 100Ω.

The original LPC-Link1 only supported 3.3V and did not require VTref whereas the LPC-Link2 uses dual-supply buffers that allows the Link2 to work with targets using a different voltage (between 1.8V - 4.3V).

On the LPC-Link2, when JP2 is shunted this will power the target side of the dual-supply buffer and provide power to the target through a diode on VTref. With JP2 open the target must supply the VTref to power the target side of the dual-supply buffer.

When a debug probe attempts to adjust logic levels based on the voltage it sees on VTref, this is referenced to whatever GND it has to work with. The voltage at VTref is coming from your target, thus you need a good GND, shared with your target hardware.

Note that debug probes can be killed (like most USB devices) by excessive over current through ground of the probe and back through the PC used for debugging. The usual cause of this is that your target has it's own PSU and has a ground differential slightly different from your debug PC. Please do not rely on your debug probe to ground your PC to the same potential as your target.

Power

Even when you have designed your debug circuit according to the above considerations, you should also check that sufficient power is being supplied to your target in order to obtain a reliable debug connection. If you are using a USB port on your PC to power your target, make sure that your PC is able to supply the required power over USB - many PC USB ports do not meet USB power requirements.

Debug Connector Pinouts

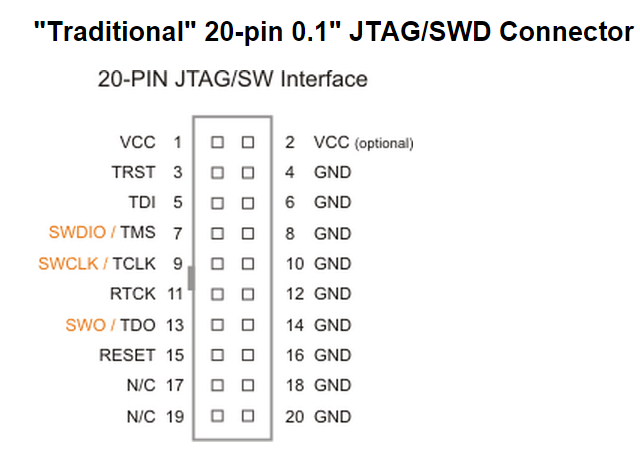

ARM has defined three debug connector pinouts that are in common use, a "traditional" 20 pin connector, a Cortex 10 pin connector and a Cortex 20 pin Debug+ETM connector...

- This connector was originally defined for connection to ARM7/9 parts over JTAG, but is still sometimes found in Cortex-M systems (for connections over JTAG or SWD).

- Note that RTCK (Return clock) is only used on older ARM cores (ARM7TDMI and ARM9 family) before the debug was properly decoupled from the core clock domain.

- Dimensions of the ARM JTAG connector are 1.29" x 0.722" (33mm x 18.5mm).

- Suitable connector headers include :

- Harwin: M50-3500542

- Mouser: 855-M50-3500542

- Samtec shrouded header: FTSH-105-01-F-D-K

- The 10-pin Samtec FTSH-105-01 connector has the dimensions: 0.25" x 0.188" (6.35mm x 4.78mm).

- Some boards use un-shrouded 10-pin headers. Always ensure that you connect your cable correctly, typically by matching the "1" marked on the board to the red -stripe on the cable.

- The 10-pin cable is Samtec part number FFSD-05-D-12.00.01-N

- This small 20-pin (0.05") connector provides access to SWD, SWV, JTAG, and ETM (4-bit) signals available on Cortex-M3/M4 devices.

- The 20-pin header (Samtec FTSH-110-01) has the dimensions: 0.50" x 0.188" (12.70mm x 4.78mm).

- Although LPCXpresso IDE does not currently support the direct use of the ETM (Embedded Trace Macrocell), a number of boards use this form of connector as one of or as their main debug connector.

- A special Cortex 10-pin debug -> Cortex 20-pin debug+ETM connector cable will typically be required to debug such boards.

ARM Cortex Design Considerations for Debug的更多相关文章

- swddude -- A SWD programmer for ARM Cortex microcontrollers.

Introducing swddude I love the ARM Cortex-M series of microcontrollers. The sheer computational po ...

- Implementation of Serial Wire JTAG flash programming in ARM Cortex M3 Processors

Implementation of Serial Wire JTAG flash programming in ARM Cortex M3 Processors The goal of the pro ...

- Game: Map Design Considerations 游戏地图设计指南

依据前文伏击战场景手稿, 用Tile Studio "草草"制作出该场景的地图: 生成的C源码: #ifndef _open_war_1Gfx_c #define _open_wa ...

- 【ARM-Linux开发】ARM7 ARM9 ARM Cortex M3 M4 有什么区别

ARM7 ARM9 ARM Cortex M3 M4 区别 arm7 arm9 可以类比386和奔腾, 不同代,arm9相比arm7指令集和性能都有所增强,arm7和arm9都有带mmu和无mmu的版 ...

- 《Amazon Aurora: Design Considerations for High Throughput Cloud-Native Relational Databases》论文总结

Aurora总结 说明:本文为论文 <Amazon Aurora: Design Considerations for High Throughput Cloud-Native Relation ...

- 灵动微电子ARM Cortex M0 MM32F0010 UART1和UART2中断接收数据

灵动微电子ARM Cortex M0 MM32F0010 UART1和UART2中断接收数据 目录: 1.MM32F0010UART简介 2.MM32F0010UART特性 3.MM32F0010使用 ...

- 灵动微电子ARM Cortex M0 MM32F0010 Timer定时器中断定时功能的配置

灵动微电子ARM Cortex M0 MM32F0010 Timer定时器中断定时功能的配置 目录: 1.Timer1高级定时器Timer3通用定时器Timer14基本定时器简介 2.Timer1高级 ...

- 灵动微电子ARM Cortex M0 MM32F0010 GPIO 的配置驱动LED灯

灵动微电子ARM Cortex M0 MM32F0010 GPIO的配置 目录: 1.前言 2.学习方法简要说明 3.要点提示 4.注意事项 5.MM32F0010系统时钟的配置 6.MM32F001 ...

- ARM Cortex Debug Port Access Port DP AP JTAG-DP SW-DP SWJ-DP JTAG-AP MEM-AP

随机推荐

- ios TextField限制输入两位小数

只需要实现textField的这个代理方法就可以实现 - (BOOL)textField:(UITextField *)textField shouldChangeCharactersInRange: ...

- 记一道有趣的Twitter面试题

微信上的“程序员的那些事”想必是很多码农们关注的公众账号之一,我也是其粉丝,每天都会看看里面有没有什么趣事,前段时间“程序员的那些事”分享了一篇博文<我的Twitter技术面试失败了>挺有 ...

- Javascript - Vue - vue对象的生命周期

vue对象的生命周期 从vue的创建到销毁会经过一系列的事件,这是vue对象的生命周期. 创建期间的生命周期函数 <div id="box"> <h3 id ...

- JQuery效果隐藏/显示

hide() 方法 语法 $(selector).hide(speed,callback) show() 方法 语法 $(selector).show(speed,callback) 参数 描述 sp ...

- mysql percona安装

注:此方式目前安装存在问题(弃用此方式) 1.在官方网站下载percona XtraBackup https://www.percona.com/downloads/XtraBackup/LATES ...

- 【Android开发】之Fragment重要函数讲解

上一节我们讲到了Fragment的生命周期(都是基于android.support.v4.app包下的Fragment),学习之后相信大家对它的生命周期有了很深入的了解了,如果还有不懂得,可以再看一下 ...

- Android 5.0 API

Android 5.0 (LOLLIPOP) 为用户和应用开发者提供了新功能.本文旨在介绍其中最值得关注的新 API. 如果您有已发布的应用,请务必看一看 Android 5.0 行为变更,了解您的应 ...

- MySQL ACID及四种隔离级别的解释

以下内容出自<高性能MySQL>第三版,了解事务的ACID及四种隔离级有助于我们更好的理解事务运作. 下面举一个银行应用是解释事务必要性的一个经典例子.假如一个银行的数据库有两张表:支票表 ...

- CSU 1948: 超级管理员(普通费用流&&zkw费用流)

Description 长者对小明施加了膜法,使得小明每天起床就像马丁的早晨一样. 今天小明早上醒来发现自己成了一位仓管员.仓库可以被描述为一个n × m的网格,在每个网格上有几个箱子(可能没有).为 ...

- 《Photoshop智能手机APP界面设计》学习笔记-转

第一章 APP用户界面基础 1.1 手机UI设计相关基本概念 1.1.1 什么是UI设计 UI(User's Interface)即用户界面,它不仅仅是美化界面,还需要研究用户,让界面变得更友好.简洁 ...