Verilog代码和FPGA硬件的映射关系(三)

组合逻辑和FPGA之间的映射关系我们知道了,那时序逻辑和FPGA之间又是一种怎样的映射关系呢?我们就以前面寄存器章节的例子来向大家说明,也一同把当时为什么用异步复位更节约资源的原因告诉大家。我们先来看一下同步复位D触发器的RTL代码,如下所示:

同步复位D触发器

//--------------------------------------------------

module flip_flop(

input wire sys_clk ,

input wire sys_rst_n ,

input wire key_in , output reg led_out

); //led_out:led灯输出的结果为key_in按键的输入值

always@(posedge sys_clk)

if(sys_rst_n == 'b0)

led_out <= 'b0;

else

led_out <= key_in; endmodule

//--------------------------------------------------

代码编写完后依然需要点击“Start Analysis & Synthesis”图标进行分析和综合。然后双击“Netlist Viewers”下的“RTL Viewer”查看RTL视图。如图1所示,可以看到一个 D触发器的结构,也可以称为寄存器,还附加了一个选择器,用于同步复位的控制,和代码设计的结果是完全一致的。

图1

点击“Start Compilation”图标全编译进行布局布线,完成后我们可以看到“Flow Summary”资源使用量,如图2所示,可以看到使用了LE中的一个组合逻辑资源和一个时序逻辑资源。

图2

然后打开Chip Planner视图。Chip Planner打开后的界面如图3所示,我们可以看到在版图模型中有一个块蓝色区域的颜色变深,说明该区域的资源被占用,在FPGA内部硬件结构简介中我们知道这是一个逻辑阵列块LAB,我们将该区域放大。

图3

如图4所示,放大后可以看到蓝色变深的区域中有16个小块,这16个小块就是LE,其中只有一个LE的颜色发生了变化,这次不仅有蓝色,还有红色,说明该处的资源被使用了,双击这个LE即可观察其内部的结构。

图4

打开LE后内部的结构如该视图中点击下面复位信号的名字后会看到在LE的内部结构图中用绿色标注路径,如5所示,其中蓝色显示的是真实使用到的结构,灰色的是未使用到的结构,我们可以看到①、②、③为三个输入,其中③为时钟的输入端,然后一个输出,和RTL代码的描述是对应的。因为我们设计的是时序逻辑,所以这次我们可以发现比组合逻辑多出来的结构主要是红色框所表示的寄存器。

图5

在该视图中点击下面复位信号的名字后会看到在LE的内部结构图中用绿色标注路径,如图6所示,可以知道①为复位信号的输入端,②为key_in信号的输入端。

图6

我们再来看一下异步复位D触发器的RTL代码,如下所示:

异步复位D触发器

//--------------------------------------------------

module flip_flop(

input wire sys_clk ,

input wire sys_rst_n ,

input wire key_in , output reg led_out

); //led_out:led灯输出的结果为key_in按键的输入值

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 'b0)

led_out <= 'b0;

else

led_out <= key_in; endmodule

//--------------------------------------------------

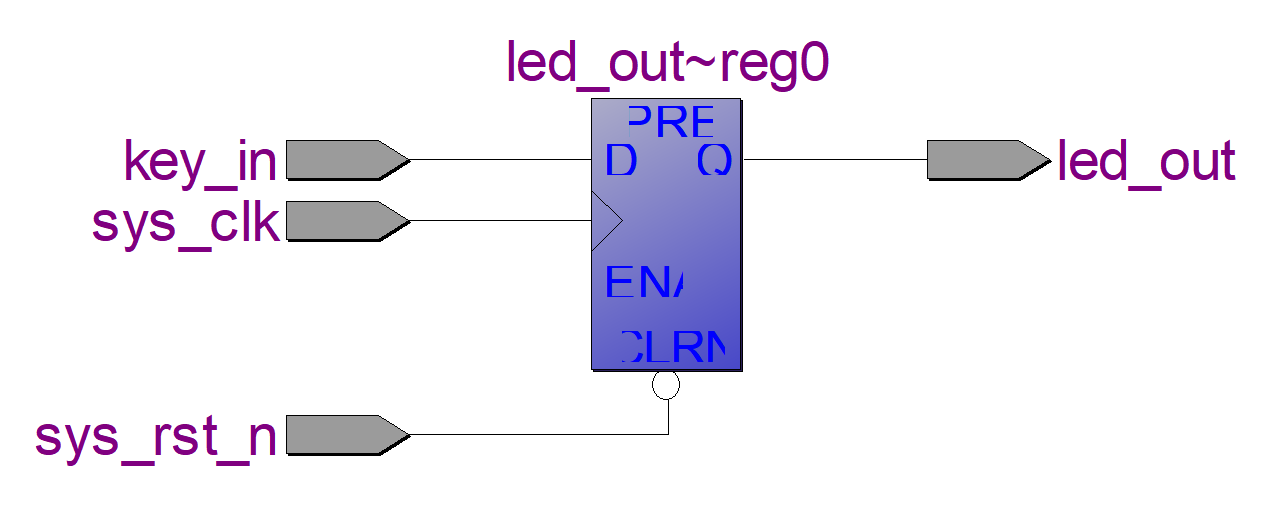

代码编写完后依然需要点击“Start Analysis & Synthesis”图标进行分析和综合。然后双击“Netlist Viewers”下的“RTL Viewer”查看RTL视图。如图7所示,我们可以看到一个 D触发器的结构,和代码设计的结果是完全一致的。

图7

图7

点击“Start Compilation”图标全编译进行布局布线,完成后我们可以看到“Flow Summary”资源使用量报告,如图8所示,可以看到只使用了LE中的一个时序逻辑资源。

图8

然后打开Chip Planner视图。Chip Planner打开后的界面如图9所示,我们可以看到在版图模型中在同样的位置也有一个块蓝色区域的颜色变深,说明该区域的资源被占用,在FPGA内部硬件结构简介中我们知道这是一个逻辑阵列块LAB,我们将该区域放大。

图9

如图10所示,放大后可以看到蓝色变深的区域中有16个小块,这16个小块就是LE,其中只有一个LE的颜色发生了变化,也有蓝色和红色,说明该处的资源被使用了,双击这个LE即可观察其内部的结构。

图10

打开LE后内部的结构如图11所示,其中蓝色显示的是真实使用到的结构,灰色的是未使用到的结构,我们可以看到①、②、③为三个输入,其中③为时钟的输入端,②仍为key_in的输入端,而复位信号①的位置则发生了变化,直接连到了寄存器上。

图11

看到这里我们不禁会有两个疑问,异步复位D触发器LE内部结构图明明显示使用了查找表,为什么却在“Flow Summary”资源使用量报告中却显示没有使用该部分资源?为什么同步复位D触发器比异步复位D触发器多使用了一部分资源呢?

首先来说第一个问题,虽然异步复位D触发器LE内部结构图明明显示使用了LUT,但是几乎没有任何逻辑需要使用LUT,相当于通过查找表将key_in信号连接到寄存器的输入端,所以在“Flow Summary”资源使用量报告中显示没有使用该部分资源。

然后是第二个问题,如图12所示,我们将寄存器部分的视图放大来看,可以发现该寄存器本身就包含一个异步清零信号“aclr”,且该清零信号还标识为“!ACLR”,也就是低电平有效,这下我们终于明白了为什么代码中使用异步低复位了,因为这部分资源本来就有,不需要额外创造,而如果我们使用同步高复位,就会增加额外的逻辑,需要使用LUT资源,所以同步复位D触发器比异步复位D触发器多使用了一个LUT,大家可以试想一下如果我们使用的很多同步复位D触发器的时候就会占用很多不必要的LUT资源,从而造成资源的浪费,希望大家以后在编写代码的时候注意。

图12

欢迎加入FPGA技术学习交流群,本群致力于为广大FPGAer提供良好的学习交流环境,不定期提供各种本行业相关资料!QQ交流群号:450843130

Verilog代码和FPGA硬件的映射关系(三)的更多相关文章

- Verilog代码和FPGA硬件的映射关系(一)

代码和硬件之间的映射关系是一个很奇妙的过程,也展现出人类的智慧.单片机内部的硬件结构都是固定的,无法改变,我们通过代码操作着寄存器的读写,来执行各种复杂的任务.FPGA的硬件结构并不像单片机一样是固定 ...

- Verilog代码和FPGA硬件的映射关系(二)

大家可能会有这样的疑问,我们编写的Verilog代码最终会在FPGA上以怎样的映射关系来实现功能呢?我们以一个最简单的组合逻辑与门为例来向大家说明.RTL代码如下所示: //------------- ...

- Verilog代码和FPGA硬件的映射关系(四)

其实在FPGA的开发中理想情况下FPGA之间的数据要通过寄存器输入.输出,这样才能使得延时最小,从而更容易满足建立时间要求.我们在FPGA内部硬件结构中得知,IOB内是有寄存器的,且IOB内的寄存器比 ...

- Verilog代码和FPGA硬件的映射关系(五)

既然我们可以指定寄存器放在IOB内,那我们同样也可以指定PLL的位置.首先要确保我们有多个PLL才行.如图1所示,我们所使用的EP4CE10F17C8芯片刚好有两个. 图 1 为了演示这个例子,我们使 ...

- FPGA边沿检测Verilog代码

FPGA边沿检测Verilog代码(上升沿,下降沿,双边沿) 实现思路:用两个一位寄存器直接异或可以实现 代码实现: module edge_detect( input clk, input rs ...

- 学会使用Hdlbits网页版Verilog代码仿真验证平台

给大家推荐一款网页版的 Verilog代码编辑仿真验证平台,这个平台是国外的一家开源FPGA学习网站,通过“https://hdlbits.01xz.net/wiki/Main_Page” 地址链接进 ...

- ASP.NET Core的路由[1]:注册URL模式与HttpHandler的映射关系

ASP.NET Core的路由是通过一个类型为RouterMiddleware的中间件来实现的.如果我们将最终处理HTTP请求的组件称为HttpHandler,那么RouterMiddleware中间 ...

- hibernate笔记--使用注解(annotation)方式配置单(双)向多对一的映射关系

前面几篇都是介绍的用配置文件来实现实体类到数据库表的映射,这种方式是比较麻烦的,每一个pojo类都需要写一个相应的*.hbm.xml,无疑增加了很多代码量,不过也有优点就是利于维护,为了方便开发,Hi ...

- hibernate笔记--单(双)向的多对多映射关系

在讲单向的多对多的映射关系的案例时,我们假设我们有两张表,一张角色表Role,一张权限表Function,我们知道一个角色或者说一个用户,可能有多个操作权限,而一种操作权限同时被多个用户所拥有,假如我 ...

随机推荐

- POJ 3581 Prime Gap(二分)

Prime Gap Time Limit: 5000MS Memory Limit: 65536K Total Submissions: 11009 Accepted: 6298 Descriptio ...

- 7) 项目准备流程 和 django权限六表

一.项目准备 1. 创建django项目 2. 创建数据库 —— init文件中声明mysql —— settings中配置数据库 import pymysql pymysql.install_as_ ...

- 经过踩坑,搭建成功的Appium自动化测试环境

因为最近本人准备搞app自动化,所以就搭建环境过程记录下来(主要踩过好几个坑) 期间有点烦躁,后面调整了下心态还是成功弄好了. 一.Appium环境搭建准备软件 所需要到的软件如下: 1.安装JDK1 ...

- MySQL 8.0.20 源码安装数据库软件

官方支持的平台: https://www.mysql.com/support/supportedplatforms/database.html

- thinkphp-getshell Bypass

年前写的了,做测试用,主要利用 session getshell 或者thinkphp 的log //勿用attack 测试 import requests import time import ...

- K - Leapin' Lizards HDU - 2732 网络流

题目链接:https://vjudge.net/contest/299467#problem/K 这个题目从数据范围来看可以发现是网络流,怎么建图呢?这个其实不是特别难,主要是读题难. 这个建图就是把 ...

- basicRF双向灯光控制

题目: 实现基于BasicRF无线点对点通信的双向灯光控制,具体要求如下: 1> 节点A 和节点B 的PANID设置为0x1234,通道号设置为17,节点地址自定义.<2> 按下节点 ...

- Spring Boot 整合 Apache Dubbo

Apache Dubbo是一款高性能.轻量级的开源 Java RPC 框架,它提供了三大核心能力:面向接口的远程方法调用,智能容错和负载均衡,以及服务自动注册和发现. 注意,是 Apache Dubb ...

- Spring Cloud学习 之 Spring Cloud Ribbon(执行流程源码分析)

Spring Boot版本:2.1.4.RELEASE Spring Cloud版本:Greenwich.SR1 文章目录 分析: 总结: 分析: 在上篇文章中,我们着重分析了RestTempla ...

- JVM垃圾回收器(三)

垃圾回收知识点 引用计数 给对象添加一个引用计数器,每当一个地方引用这个对象,这个计算器就加1.如果引用失效,那计算器就减1.如果计算器数量为0,那这个对象就是失效的. 但是如果2个对象虽然不用了,但 ...