基于FPGA的DDS任意波形发生器设计

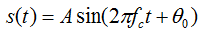

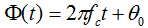

从两式可以看出,正弦信号是关于相位的一个周期函数,下图更加直观的描述相位与幅度的关系,16个相位与16个幅度值相对应,即每一个相位值对应一个幅度值,比如1100对应的相位为3π/2,对应的幅度值为-1.

相位和幅值的一一对应关系就好比存储器中地址和存储内容的关系,如果把一个周期内每个相位对应的幅度值存入存储器当中,那么对于任意频率的正弦信号,在任意时刻,只要已知相位Φ(t),也就知道地址,就可通过查表得到s(t)。下图是DDS的基本结构框图:

相位累加器在每个时钟脉冲输入时,把频率控制字累加一次,相位累加器的输出数据就是信号的相位,用输出的数据作为波形存储器(ROM)的相位取样地址,这样就可以把存取在波形存储器内的波形抽样值经查找表查处,完成相位到幅值的转换。频率控制字相当于Φ(t)中的2πfc,相位控制字相当于Φ(t)中的θ0。

为了获得较高的频率分辨率,则只有增加相位累加器的字长N,故一般N都取值较大。但是受存储器容量的限制,存储器地址线的位数w不可能很大,一般都要小于N。这样存储器的地址线一般都只能接在相位累加器输出的高w位,而相位累加器输出余下的(N-W)个低位则只能被舍弃,这就是相位截断误差的来源。

频率分辨率,即频率的变化间隔

三、实现代码

module DDS (sys_clk,sys_rst_n,freq_word,phase_word,wave_out);input sys_clk ; //系统工作时钟input sys_rst_n ; //复位,低有效input [31:0] freq_word ; //频率控制字,控制输出波形频率input [11:0] phase_word ; //相位控制字,控制初始相位output[9:0] wave_out ; //输出波形,位宽10bitreg [31:0] freq_word_reg ;reg [11:0] phase_word_reg ;reg [31:0] phase_adder ; //相位累加器reg [9:0] rom_address ; //存储深度2^10always @(posedge sys_clk or negedge sys_rst_n) beginif (sys_rst_n ==1'b0) beginfreq_word_reg <= 32'h0000;endelsefreq_word_reg <= freq_word;endalways @(posedge sys_clk or negedge sys_rst_n) beginif (sys_rst_n ==1'b0) beginphase_word_reg <= 12'h0000;endelsephase_word_reg <= phase_word;endalways @(posedge sys_clk or negedge sys_rst_n) beginif (sys_rst_n ==1'b0) beginphase_adder <= 32'h0000;endelsephase_adder <= phase_adder + freq_word_reg; //对频率控制字进行累加endalways @(posedge sys_clk or negedge sys_rst_n) beginif (sys_rst_n ==1'b0) beginrom_address <= 32'h0000;endelserom_address <= phase_adder[31:20] + phase_word_reg;endsin_rom DDS_ROM_U0 (.address (rom_address) ,.clock (sys_clk) ,.q (wave_out));endmodule

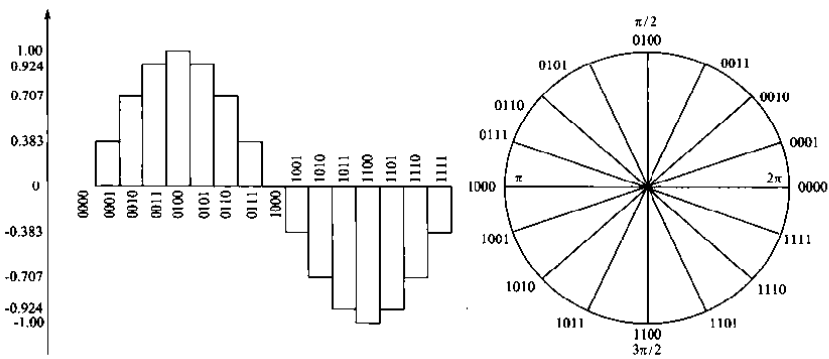

`timescale 1 ns/ 1 nsmodule DDS_tb();reg [31:0] freq_word ;reg [11:0] phase_word ;reg sys_clk ;reg sys_rst_n ;wire [9:0] wave_out ;DDS i1 (.freq_word(freq_word),.phase_word(phase_word),.sys_clk(sys_clk),.sys_rst_n(sys_rst_n),.wave_out(wave_out));initialbeginsys_clk = 0;sys_rst_n = 0;freq_word = 0;phase_word = 0;#2000;sys_rst_n = 1;freq_word = 32'd1024; //25Mphase_word = 32'd0; //相位0度#200000000;freq_word = 32'd2048; //50Mphase_word = 32'd512; //相位90度#200000000;$stop;endalways sys_clk = #20 ~sys_clk; //系统时钟25Mendmodule

基于FPGA的DDS任意波形发生器设计的更多相关文章

- 基于FPGA的DDS设计(一)

最近在学习基于FPGA的DDS设计,借此机会把学习过程记录下来,当作自己的学习笔记也希望能够帮助到学习DDS的小伙伴. DDS(Direct Digital Synthesizer)直接数字合成器,这 ...

- 文献翻译|Design of True Random Number Generator Based on Multi-stage Feedback Ring Oscillator(基于多级反馈环形振荡器的真随机数发生器设计)

基于多级反馈环形振荡器的真随机数发生器设计 摘要 真随机数生成器(trng)在加密系统中起着重要的作用.本文提出了一种在现场可编程门阵列(FPGA)上生成真随机数的新方法,该方法以 多级反馈环形振荡器 ...

- (DDS)正弦波形发生器——幅值、频率、相位可调(二)

(DDS)正弦波形发生器--幅值.频率.相位可调(二) 主要关于调相方面 一.项目任务: 设计一个幅值.频率.相位均可调的正弦波发生器. 频率每次增加10kHz 相位每次增加 PI/2 幅值每次增加两 ...

- (DDS)正弦波形发生器——幅值、频率、相位可调(一)

(DDS)正弦波形发生器--幅值.频率.相位可调 一.项目任务: 设计一个幅值.频率.相位均可调的正弦波发生器. 频率每次增加1kHz. 相位每次增加 2*PI/256 幅值每次增加两倍 二.文章内容 ...

- 基于FPGA的VGA可移植模块终极设计【转】

本文转载自:http://www.cnblogs.com/lueguo/p/3373643.html 略过天涯 基于FPGA的VGA可移植模块终极设计 一.VGA的诱惑 首先,VGA的驱动,这事, ...

- 基于DDS的任意波形发生器

实验原理 DDS的原理 DDS(Direct Digital Frequency Synthesizer)直接数字频率合成器,也可叫DDFS. DDS是从相位的概念直接合成所需波形的一种频率合成技术. ...

- 基于FPGA的DDS设计(二)

在DDS设计中,如果相位累加器每个时钟周期累加1,就会输出频率为195.313KHz的波形.如果每个时钟周期累加2,就会输出频率为2*195.313KHz的波形·······,如果每两个时钟周期累加1 ...

- 基于FPGA(DDS)的正弦波发生器

记录背景:昨晚快下班时,与同事rk聊起怎么用FPGA实现正弦波的输出.我第一反应是利用高频的PWM波去滤波,但感觉这样的波形精度肯定很差:后来想起之前由看过怎么用FPGA产生正弦波的技术,但怎么都想不 ...

- 基于FPGA的通信信号源的设计

通信信号源设计原理 通过设计一个DDS信号源,然后将该信号作为载波信号,再对基带信号进行2ASK.2FSK.2PSK.2DPSK调制,进而产生多种通信信号. 设计框图如下: 将PN序列进行2ASK.2 ...

随机推荐

- Linux打开防火墙telnet端口

检查端口情况:netstat -an | grep 22 关闭端口号:iptables -A INPUT -p tcp --drop 端口号-j DROP ipt ...

- jq操作select集合

jq操作select集合 时间:2012年12月07日分类:Javascript 最近一段时间发现,老是要跟select,option相关的东西打交道,而且有的时候还会搞错,于是,抽了一点时间整理了一 ...

- VC代码生成里面的/MT /MTd /MD /MDd的意思

VC代码生成里面的/MT /MTd /MD /MDd的意思. 意思上已经很明白了.但是往往很多人弄不清楚到底怎么选择. /MT是 "multithread, static version ” ...

- HDU - 5015 233 Matrix(杨辉三角/前缀+矩阵快速幂)

233 Matrix In our daily life we often use 233 to express our feelings. Actually, we may say 2333, 23 ...

- Javascript实现打开或退出浏览器全屏

废话不多说,直接上代码: <!DOCTYPE html PUBLIC "-//W3C//DTD XHTML 1.0 Strict//EN" "http://www. ...

- untiy AnimationEvent添加返回参数

using UnityEngine; using System.Collections; public class Try : MonoBehaviour { public class Action ...

- SublimeText3 snippet 编写总结

SublimeText3 snippet 编写总结 SublimeText的snippet定义功能也十分强大, 类似VAssist. 在菜单tool->New Snippet中定义. 打开后显 ...

- Sanic框架

Sanic框架 1. 入门 Sanic 是一款类似Flask的Web服务器,它运行在Python 3.5+上. 除了与Flask功能类似之外,它还支持异步请求处理,这意味着你可以使用Python3.5 ...

- 【考试记录】2018 山东省队集训第一轮D4(雾)

T1题意: 给你一个$n\times m$的矩阵$B$,求它能由最少多少个形如两个向量之积$(n\times 1)\times(1\times m)$的矩阵相加得到. 题解: 考虑上界,最多需要$mi ...

- 2019湘潭校赛 G(并查集)

要点 题目传送 题目本质是每个点必属于两个集合中的一个,伴随的性质是:如果一个人说别人true,则他们一定属于同一阵营:如果说别人fake,一定不属于同一阵营. 每个点拆为\(i\)和\(i + n\ ...