Nand flash基本原理

Nand flash基本原理

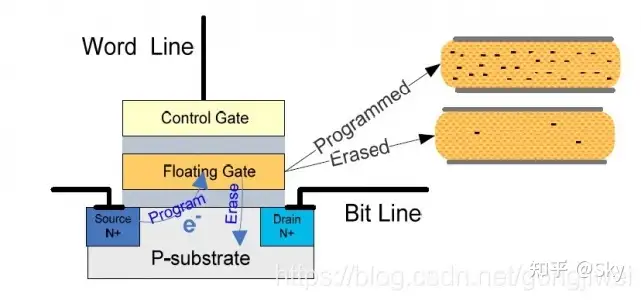

Flash的内部存储是金属-氧化层-半导体-场效晶体管(MOSFET),里面有个悬浮门(Floating Gate),是真正存储数据的单元。

数据在Flash内存单元中是以电荷(electrical charge) 形式存储的。存储电荷的多少,取决于图中的控制门(Control gate)所被施加的电压,其控制了是向存储单元中冲入电荷还是使其释放电荷。而数据的表示,以所存储的电荷的电压是否超过一个特定的阈值Vth 来表示。

1.对于NAND Flash的写入(编程),就是控制Control Gate去充电(对Control Gate加压),使得悬浮门存储的电荷够多,超过阈值Vth,就表示0。

2.对于NAND Flash的擦除(Erase),就是对悬浮门放电,低于阀值Vth,就表示1。

NAND Flash的架构:

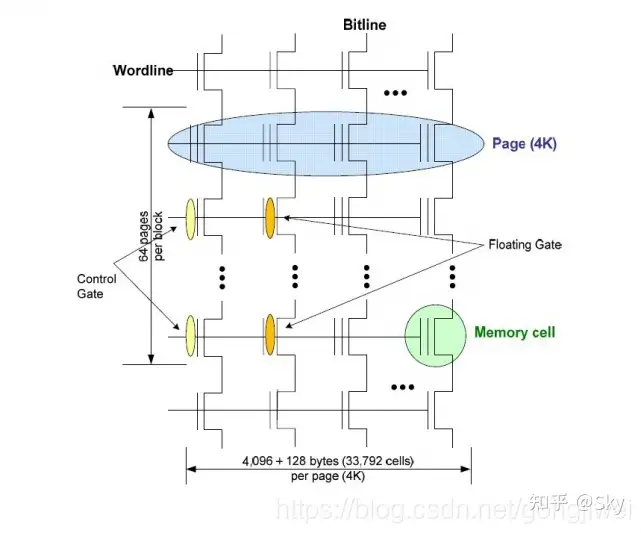

如上图所示,这是一个8Gb 50nm的SLC颗粒内部架构。

每个page有33,792个单元,每个单元代表1bit(SLC),所以每个page就是4096Byte + 128Byte(SA)。

每个Block有64个page组成,所以每个Block容量为262,114Byte + 8192Byte (SA)

page是NAND Flash上最小的读/写单位(一个page上的单元共享一根字符线Word line),块是最小的擦除单位(。不同厂牌不同型号颗粒有不同的page和block大小。

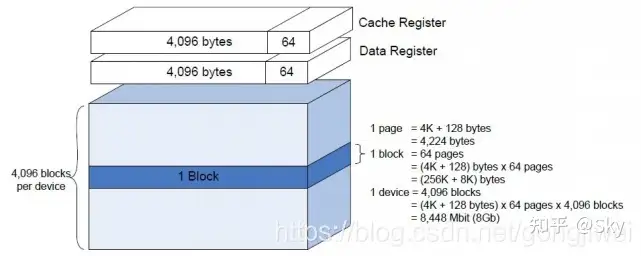

下图是个8Gb 50nm的SLC颗粒。

4KB的页尺寸,256KB的块尺寸。图中4096字节用于存储数据,另外128字节用来做管理和ECC用。

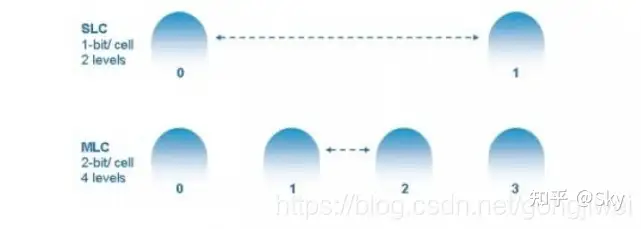

SLC 和 MLC 区别:

SLC主要针对军工,企业级应用,有着高速写入,低出错率,长耐久度特性。

MLC主要针对消费级应用,有着2倍容量于SLC,低成本,适合USB闪盘,手机,数码相机等储存卡。如今也被用于消费级固态硬盘上。

由上图可以看到,MLC和SLC虽然使用相同的电压值,但是电压之间的阀值被分成了4份,直接影响了性能和稳定性。主要有下面几点:

1.相邻的存储电荷的悬浮门间会互相干扰,造成悬浮门里的电荷不稳定出现bit错误,MLC由于阀值相比SLC更接近,造成出错几率更大。

2.MLC读写性能降低,写入更是降低50%以上,因为需要确认充入电荷的量,这需要更精确的处理。SLC只有0和1,也就是有和没有,而MLC会有00,01,10,11 4个状态,在充入电荷后还要去判断是哪个状态,自然就慢了。

3.因为上面说的,造成额外的读写压力,所以功耗明显增大。

4.因为额外的读写压力,造成闪存的写入耐久度和数据保存期受到影响。

eMLC和eSLC的耐久度提升是用牺牲了数据保存期和增加读写时间换来的。(也就是性能会更差点)

Nand flash基本原理的更多相关文章

- ECC校验原理以及在Nand Flash中的应用

本篇文章主要介绍ECC基本原理以及在Nand Flash中的应用,本文记录自己对ECC校验原理的理解和学习. ECC介绍 ECC,全称为Error Correcting Code, ...

- NOR flash和NAND flash区别,RAM 和ROM区别

ROM和RAM指的都是半导体存储器,ROM是Read Only Memory的缩写,RAM是Random Access Memory的缩写.ROM在系统停止供电的时候仍然可以保持数据,而RAM通常都是 ...

- NOR flash和NAND flash区别,RAM 和ROM区别d

ROM和RAM指的都是半导体存储器,ROM是Read Only Memory的缩写,RAM是Random Access Memory的缩写.ROM在系统停止供电的时候仍然可以保持数据,而RAM通常都是 ...

- nor flash 和nand flash 的区别

ROM和RAM指的都是半导体存储器,ROM是Read Only Memory的缩写,RAM是Random Access Memory的缩写.ROM在系统停止供电的时候仍然可以保持数据,而RAM通常都是 ...

- NAND FLASH 物理结构分析

转自:http://blog.51cto.com/hardywang/2053915 NAND Flash是一种非易失性随机访问存储介质,基于浮栅(Floating Gate)晶体管设计,通过浮栅来锁 ...

- 在 U-BOOT 对 Nand Flash 的支持

1.1 U-BOOT 对从 Nand Flash 启动的支持 1.1.1 从 Nand Flash 启动 U-BOOT 的基本原理 1. 前 4K 的问题 如果 S3C2410 被配置成从 ...

- S3C2440从NAND Flash启动和NOR FLASH启动的问题

1.为什么NAND FLASH不能直接运行程序 NAND FLASH本身是连接到了控制器上而不是系统总线上.CPU运行机制为:CPU启动后是要取指令执行的,如果是SROM.NOR FLASH ...

- 嵌入式Linux驱动学习之路(二十三)NAND FLASH驱动程序

NAND FLASH是一个存储芯片. 在芯片上的DATA0-DATA7上既能传输数据也能传输地址. 当ALE为高电平时传输的是地址. 当CLE为高电平时传输的是命令. 当ALE和CLE都为低电平时传输 ...

- (一)Nand FLASH 原理讲解

NAND FLASH 优势 : 可以用当硬盘 这里好像型号是 K9F2G08 基本结构: 不是很难自己看看,暂时不要看

- NAND flash sub-pages

http://www.linux-mtd.infradead.org/doc/ubi.html#L_subpage NAND flash sub-pages As it is said here, a ...

随机推荐

- 一 , FileChanle

package nio; import java.io.IOException; import java.io.RandomAccessFile; import java.nio.ByteBuffer ...

- [转帖]oracle rac后台进程和LMS说明

本文摘抄录oracle官方文档,oracle rac使用的后台进程,用以备忘,记录之. About Oracle RAC Background Processes The GCS and GES pr ...

- [转帖]Tail Latency学习

https://www.cnblogs.com/Rohn/p/15123758.html Latency,中文译作延迟,Tail Latency即尾延迟. 实际生产中的Latency是一种(概率)分布 ...

- [转帖]linux时间戳转换成时间指令_时间戳转换公式

原文地址:http://wanping.blogbus.com/logs/28663569.html 1.时间戳转换为正常显示的时间格式 Freebsd 系统下: 转换命令为: date -r 111 ...

- [转帖]Springboot容器化镜像设置堆内存大小

参考资料:Best Practices: Java Memory Arguments for Containers - DZone Java 有三种方式设置最大堆内存大小: 1. -Xmx 2. -X ...

- [转帖]讨论在 Linux Control Groups 中运行 Java 应用程序的暂停问题原创

https://heapdump.cn/article/1930426 说明 本篇原文来自 LinkedIn 的 Zhenyun Zhuang,原文:Application Pauses When R ...

- 是否开启超线程对CPU不同命令的影响情况

背景 最近公司购买了一台服务器, 要进行一次性能测试. 基于此, 我这边进行了一下超线程与否的测试验证 使用stress-ng的命令,对所有的 CPU 方法进行测试 然后只分析 bogo ops/s ...

- qperf 简要总结 - 延迟与带宽信息

总结 同一个虚拟机: 延迟: 12us 带宽: 6GB/S 同一个物理机上面的虚拟机: 延迟: 50us-100us 带宽: 1.2GB/S 同一个交换机上面的虚拟机: 延迟: 60us 带宽: 12 ...

- Linux部分参数的学习

Linux部分参数的学习 简介 之前总结过很多Nginx或者是部署软件时的一些注意事项. 但是感觉对linux系统参数部分掌握的不是很好. 今天周末想着整理一下,作为备忘. limits.conf i ...

- 【图论,网络流】CF1525F Goblins And Gnomes

Problem Link 你在打怪.你有一个 \(n\) 个点 \(m\) 条边的 DAG,接下来会有 \(k\) 波怪来袭,第 \(i\) 波怪有 \(i\) 个,它们会各自选择走一条路径,要求它们 ...