使用自由软件Icarus Verilog Simulator进行仿真

Icarus Verilog Simulator(http://iverilog.icarus.com/home)使用iverilog作为源代码编译器,编译生成vvp程序文本,使用vvp作为运行时引擎,支持vcd波形Dump,支持lxt格式波形,可以使用gtkwave来Debug波形。

各大Linux发行版和Windows系统均可以直接安装iverilog/gtkwave,iverilog/vvp/gtkwave参数可以通过man *查看。

一个简单的Testbench示例:

//***********************************************************************************************

// File : tb_top.sv

// Author : Lyu Yang

// Date : 2018-12-09

// Description : Simple Testbench using iVerilog

//***********************************************************************************************

`timescale 1ns/1ns

module tb_top; logic clk;

logic [:] cnt; initial forever # clk = ~clk; initial begin

clk = ;

cnt = ;

repeat()

begin

@(posedge clk);

cnt = cnt + ;

$display("@%4t ns: cnt = 0x%-04X", $time, cnt);

end

#;

$finish;

end initial begin

//$dumpfile("tb_top.vcd");

$dumpfile("tb_top.lxt");

$dumpvars();

end endmodule

使用上述工具集的Makefile示例:

#***********************************************************************************************

# File : Makefile

# Author : Lyu Yang

# Date : --

# Description : Makefile for iVerilog

#*********************************************************************************************** all: cmp vvp lxt cmp:

iverilog -g2005-sv tb_top.sv -o tb_top.vvp vvp:

vvp tb_top.vvp -fst -sdf-verbose -lxt2 lxt:

gtkwave tb_top.lxt & clean:

@rm -rf tb_top.vvp tb_top.lxt

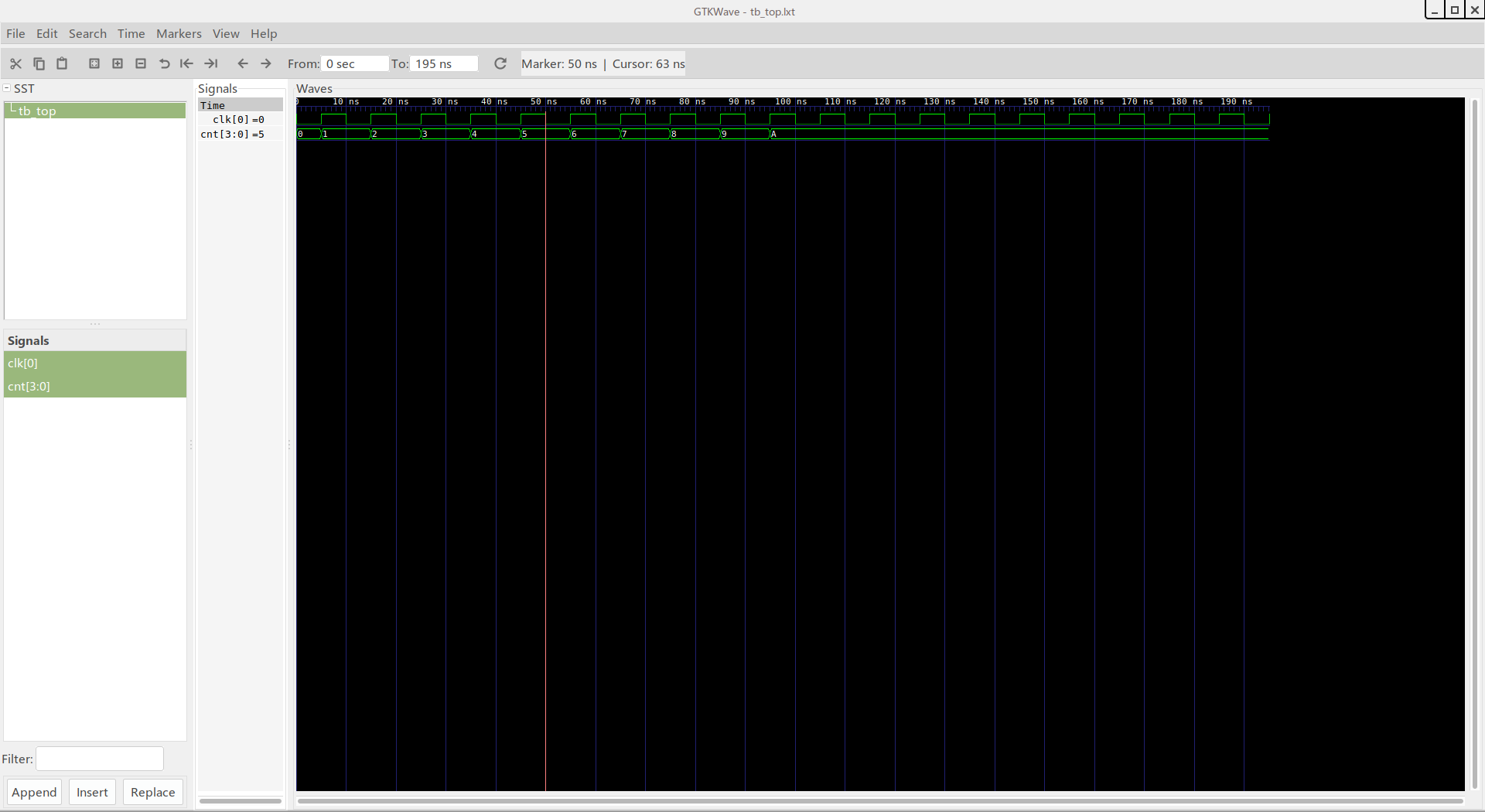

波形窗口:

使用自由软件Icarus Verilog Simulator进行仿真的更多相关文章

- Icarus Verilog和GTKwave使用简析

Icarus Verilog和GTKwave使用简析 来源 http://blog.csdn.net/husipeng86/article/details/60469543 本文测试文件在window ...

- VCS使用学习笔记(1)——Verilog相关的仿真知识

本文主要学习Verilog的仿真特性,以及仿真器对Verilog的处理,算是对Verilog知识的增量学习.本文内容与我的另一篇博文(http://www.cnblogs.com/IClearner/ ...

- Verilog篇(三)仿真原理

首先引入一个例子: `timescale 1ns/100ps module TB; ...

- 数字IC设计工程师的知识结构

刚毕业的时候,我年少轻狂,以为自己已经可以独当一面,庙堂之上所学已经足以应付业界需要.然而在后来的工作过程中,我认识了很多牛人,也从他们身上学到了很多,从中总结了一个IC设计工程师需要具备的知识架构, ...

- 全平台轻量级 Verilog 编译器 & 仿真环境

一直苦于 modelsim 没有Mac版本,且其体量过大,在学习verilog 时不方便使用. 终于找到一组轻量级且全平台 ( Linux+Windows+macOS ) 的编译仿真工具组. Icar ...

- 学会使用Hdlbits网页版Verilog代码仿真验证平台

给大家推荐一款网页版的 Verilog代码编辑仿真验证平台,这个平台是国外的一家开源FPGA学习网站,通过“https://hdlbits.01xz.net/wiki/Main_Page” 地址链接进 ...

- vsim生成VCD波形文件(verilog)

Vsim(ModelSim)生成VCD波形文件(verilog) 两种方法 方法一: 调用ModelSim自己的命令生成,仿真脚本中加入如下一句即可 vcd file mytb.vcd 方法二: 调用 ...

- 全平台轻量开源verilog仿真工具iverilog+GTKWave使用教程

前言 如果你只是想检查Verilog文件的语法是否有错误,然后进行一些基本的时序仿真,那么Icarus Verilog 就是一个不错的选择.相比于各大FPGA厂商的IDE几个G的大小,Icarus V ...

- 用Sublime Text搭建简易IDE编写Verilog代码

前言 Verilog是一种硬件描述语言(HDL),该语言在Windows上有集成开发环境可以使用,如ModelSim,但ModelSim的编辑器不太好用因此笔者萌生了用Sublime Text3来编写 ...

随机推荐

- 【Java】 参数的传递:值传递与引用传递讨论

内容稍多,可直接看第4点的讨论结果 前言 在涉及到传递参数给方法时,容易出现一些参数传递错误的问题,这就涉及到了参数的传递问题,必须搞清楚:参数是如何传递到方法中的?一般来说,参数的传递可以分为两种: ...

- linux 命令行对mysql数据进行备份和还原

一.备份 1.进入mysql目录 cd /var/lib/mysql (进入mysql目录,根据安装情况会有差别) 2.备份 mysqldump -u root -p密码 数据库名 数据表名 > ...

- ubuntu16.04 安装symfony3.3.11 碰到的问题:extension dom is required | oops an error occurred 500

问题1:Uncaught exception 'RuntimeException' with message 'Extension DOM is required' 解决:sudo apt-get i ...

- 回文树练习 Part1

URAL - 1960 Palindromes and Super Abilities 回文树水题,每次插入时统计数量即可. #include<bits/stdc++.h> using ...

- Alter GDG limit

//JOBCARD... //*-------------------------------------------------------------------* //* Alter GDG l ...

- load Properties

/* */ public static final Properties loadProperties(String propertyFileRelativePath) /* */ { /* 67 * ...

- OI回忆录(流水账)

今天是NOI2017疏散日,晚上回到家在电脑前写下这篇回忆录. 初中参加过几次普及组,拿过一等奖,自招进slyz. 高一参加过CTSC2016,狗牌滚粗qwq 高二参加过WC2017,CTSC2017 ...

- 【BZOJ】3195: [Jxoi2012]奇怪的道路【状压/奇偶性】【思路】

3195: [Jxoi2012]奇怪的道路 Time Limit: 10 Sec Memory Limit: 128 MBSubmit: 802 Solved: 529[Submit][Statu ...

- Python168的学习笔记7

关于多线程操作. 对于IO操作,如访问网站,写入磁盘这种需要时间等待响应的操作,多个cpu也几乎不能提高效率. 对于CPU密集型操作,如这个格式转换,可以通过多个cpu同时去进行. 但是对于pytho ...

- Oracle连接步骤

JDBC实现数据所有的操作: 数据库连接需要的步骤 1.数据库的驱动程序:oracle.jdbc.driver.OracleDriver; 2.连接地址:jdbc:oracle:thin:@主机地址: ...