1080P60视频源---verilog

1080P60视频源---verilog

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: chensimin

//

// Create Date: 2019/03/15 10:09:21

// Design Name:

// Module Name: video_source

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////// module video_source ( input wire clk,

input wire rest,

output reg [:] video_y = 'h3FF,

output reg [:] video_c = 'h3FF,

output wire data_enable,

output reg sync_h = ,

output reg sync_v = ); //--------------------------------------------------------------------------------------------------------------- reg [:] h_count = ; always @(posedge clk or posedge rest)

begin

if(rest)

h_count <= 'd2199;

else if(h_count == 'd2199)

h_count <= 'd0;

else

h_count <= h_count + 'd1;

end //--------------------------------------------------------------------------------------------------------------- reg h_end = ; always @(posedge clk or posedge rest)

begin

if(rest)

h_end <= 'b0;

else if(h_count == 'd2198)

h_end <= 'b1;

else

h_end <= 'b0;

end //--------------------------------------------------------------------------------------------------------------- reg [:] v_count = ; always @(posedge clk or posedge rest)

begin

if(rest)

v_count <= 'd1;

else if(v_count == 'd1125 & h_count == 12'd2199)

v_count <= 'd1;

else if(h_end)

v_count <= v_count + 'd1;

end //--------------------------------------------------------------------------------------------------------------- wire b0, b1, b2, b3, b4, b5, b6, b7;

wire [:] condition_b; assign b0 = v_count >= 'd1 & v_count < 12'd41 ;

assign b1 = v_count == 'd41 & h_count <= 12'd2198 ;

assign b2 = v_count >= 'd42 & v_count < 12'd1121 ;

assign b3 = v_count == 'd1121 & h_count <= 12'd2198 ;

assign b4 = v_count == 'd1121 & h_count == 12'd2199 ;

assign b5 = v_count >= 'd1122 & v_count < 12'd1125 ;

assign b6 = v_count == 'd1125 & h_count <= 12'd2198 ;

assign b7 = v_count == 'd1125 & h_count == 12'd2199 ; assign condition_b = {b0, b1, b2, b3, b4, b5, b6, b7}; //--------------------------------------------------------------------------------------------------------------- reg v = ; always @(posedge clk or posedge rest)

begin

if(rest)

v <= 'b0;

else

begin

case(condition_b)

'b1000_0000:

v <= 'b1;

'b0100_0000:

v <= 'b1;

'b0010_0000:

v <= 'b0;

'b0001_0000:

v <= 'b0;

'b0000_1000:

v <= 'b1;

'b0000_0100:

v <= 'b1;

'b0000_0010:

v <= 'b1;

'b0000_0001:

v <= 'b1;

default:

v <= 'b0;

endcase

end

end //--------------------------------------------------------------------------------------------------------------- wire [:] condition_a ; assign a0 = h_count == 'd2199 ; // 3FF

assign a1 = h_count == 'd0 ; // 000

assign a2 = h_count == 'd1 ; // 000

assign a3 = h_count == 'd2 ; // EAV

assign a4 = h_count >= 'd3 & h_count <= 274 ; // Blank

assign a5 = h_count == 'd275 ; // 3FF

assign a6 = h_count == 'd276 ; // 000

assign a7 = h_count == 'd277 ; // 000

assign a8 = h_count == 'd278 ; // SAV

assign a9 = h_count >= 'd279 & h_count <= 2198 ; // Active assign condition_a = {a0, a1, a2, a3, a4, a5, a6, a7, a8, a9}; //--------------------------------------------------------------------------------------------------------------- reg eav = ;

reg sav = ; always @(posedge clk or posedge rest)

begin

if(rest)

begin

video_y <= 'h3FF;

eav <= 'b0;

sav <= 'b0;

end

else

begin eav <= 'b0;

sav <= 'b0; case(condition_a)

'b100_0000_000:

video_y <= 'h3FF;

'b010_0000_000:

video_y <= 'h000;

'b001_0000_000:

video_y <= 'h000;

'b000_1000_000:

begin

eav <= 'b1;

if( v_count >= & v_count <= )

video_y <= {'b1, 1'b0, 'b0, 1'b1, 'b0^1'b1, 'b0^1'b1, 'b0^1'b0, 'b0^1'b0^'b1, 1'b0, 'b0};

else

video_y <= {'b1, 1'b0, 'b1, 1'b1, 'b1^1'b1, 'b0^1'b1, 'b0^1'b1, 'b0^1'b1^'b1, 1'b0, 'b0};

end

'b000_0100_000:

video_y <= 'h040;

'b000_0010_000:

video_y <= 'h3FF;

'b000_0001_000:

video_y <= 'h000;

'b000_0000_100:

video_y <= 'h000;

'b000_0000_010:

begin

sav <= 'b1;

if( v_count >= & v_count <= )

video_y <= {'b1, 1'b0, 'b0, 1'b0, 'b0^1'b0, 'b0^1'b0, 'b0^1'b0, 'b0^1'b0^'b0, 1'b0, 'b0};

else

video_y <= {'b1, 1'b0, 'b1, 1'b0, 'b1^1'b0, 'b0^1'b0, 'b0^1'b1, 'b0^1'b1^'b0, 1'b0, 'b0};

end

'b000_0000_001:

video_y <= 'h0CD;

default:

video_y <= 'h040;

endcase

end

end //--------------------------------------------------------------------------------------------------------------- always @(posedge clk or posedge rest)

begin

if(rest)

video_c <= 'h3FF;

else

begin case(condition_a)

'b100_0000_000:

video_c <= 'h3FF;

'b010_0000_000:

video_c <= 'h000;

'b001_0000_000:

video_c <= 'h000;

'b000_1000_000:

begin

if( v_count >= & v_count <= )

video_c <= {'b1, 1'b0, 'b0, 1'b1, 'b0^1'b1, 'b0^1'b1, 'b0^1'b0, 'b0^1'b0^'b1, 1'b0, 'b0};

else

video_c <= {'b1, 1'b0, 'b1, 1'b1, 'b1^1'b1, 'b0^1'b1, 'b0^1'b1, 'b0^1'b1^'b1, 1'b0, 'b0};

end

'b000_0100_000:

video_c <= 'h040;

'b000_0010_000:

video_c <= 'h3FF;

'b000_0001_000:

video_c <= 'h000;

'b000_0000_100:

video_c <= 'h000;

'b000_0000_010:

begin

if( v_count >= & v_count <= )

video_c <= {'b1, 1'b0, 'b0, 1'b0, 'b0^1'b0, 'b0^1'b0, 'b0^1'b0, 'b0^1'b0^'b0, 1'b0, 'b0};

else

video_c <= {'b1, 1'b0, 'b1, 1'b0, 'b1^1'b0, 'b0^1'b0, 'b0^1'b1, 'b0^1'b1^'b0, 1'b0, 'b0};

end

'b000_0000_001:

video_c <= 'h0CD;

default:

video_c <= 'h040;

endcase

end

end //--------------------------------------------------------------------------------------------------------------- reg h = ; always @(posedge clk or posedge rest)

begin

if(rest)

h <= 'b0;

else if(h_count == | ( h_count >= & h_count <= ))

h <= 'b0;

else

h <= 'b1;

end //--------------------------------------------------------------------------------------------------------------- assign data_enable = h & ~v; //--------------------------------------------------------------------------------------------------------------- always @(posedge clk or posedge rest)

begin

if(rest)

sync_h <= 'b0;

else if(h_count >= & h_count <= )

sync_h <= 'b1;

else

sync_h <= 'b0;

end //--------------------------------------------------------------------------------------------------------------- always @(posedge clk or posedge rest)

begin

if(rest)

sync_v <= 'b0;

else if(v_count >= & v_count < )

sync_v <= 'b1;

else if(v_count == & h_count <=)

sync_v <= 'b1;

else

sync_v <= 'b0;

end //--------------------------------------------------------------------------------------------------------------- endmodule /* add_force {/video_source/clk} -radix hex {1 0ns} {0 50000ps} -repeat_every 100000ps

add_force {/video_source/rest} -radix hex {1 0ns} {0 200ns} */

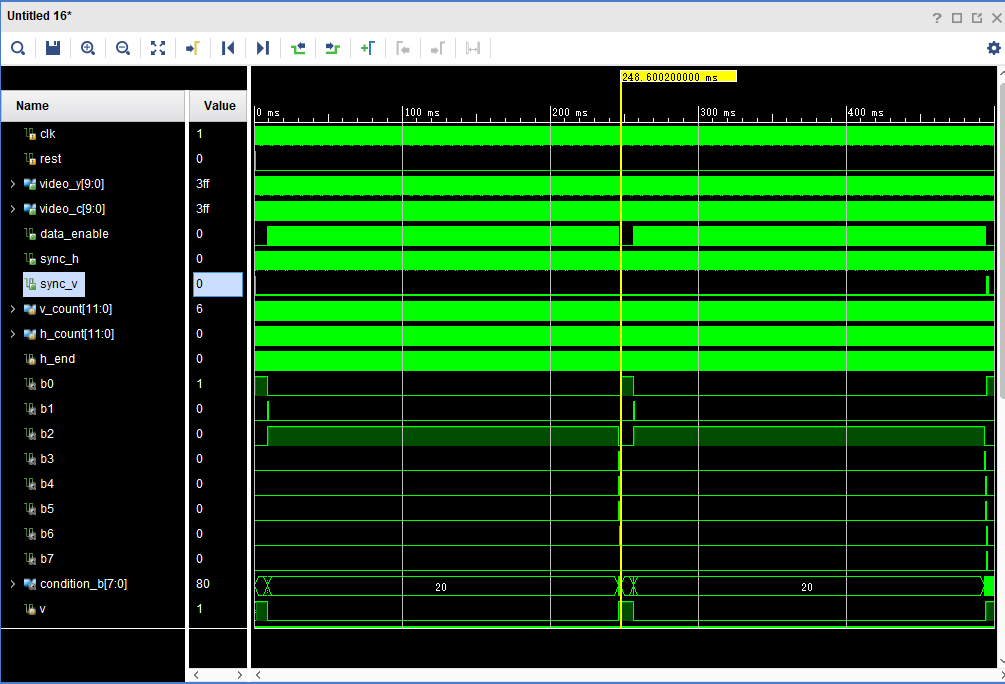

仿真结果:

1080P60视频源---verilog的更多相关文章

- C站投稿189网盘视频源(UP主篇)

C站投稿189网盘视频源(UP主篇) 现在C站(吐槽弹幕网)的视频来源基本靠的都是189网盘,比如番剧区的每个视频基本来源于此,不像AB两站,拥有自己的资源服务器,为啥呢?没钱啊.都是外来的视频.本站 ...

- 视频处理控件TVideoGrabber中如何混合多个视频源(2)

在前面的<视频处理控件TVideoGrabber混合多个视频源(1)>一文中,已经对TVideoGrabber中混合视频源做了一些内容的说明,本文将继续前文: >>>TV ...

- 视频处理控件TVideoGrabber中如何混合多个视频源(1)

其实一个或是几个作为普通的视频源使用的TVideoGrabber组件,可以进行混合来作为一个TVideoGrabber组件使用,这些普通的组件可以是视频捕捉设备或是视频剪辑等.同时这个混合的组件独立于 ...

- PC电脑运行Android模拟器总是弹出“视频源”窗体的原因和解决方案

原因: PC电脑运行Android模拟器时弹出“视频源”窗体,会让你"选择视频设备",如:HP TruevIsion HD,而这个视频设备就是你电脑中的内置摄像头,这个内置摄像头在 ...

- Python开发技术详解(视频+源码+文档)

Python, 是一种面向对象.直译式计算机程序设计语言.Python语法简捷而清晰,具有丰富和强大的类库.它常被昵称为胶水语言,它能够很轻松的把用其他语言制作的各种模块(尤其是C/C++)轻松地联结 ...

- 安卓TV开发(八) 移动智能终端多媒体爬虫技术 获取加载网页视频源

转载请标明出处:http://blog.csdn.net/sk719887916/article/details/40049137,作者:skay 从上一篇学习中,学习了多媒体技术中的怎么去用josu ...

- 安卓TV开发(七) 移动智能终端多媒体之在线解析网页视频源

载请标明出处:http://blog.csdn.net/sk719887916/article/details/40049137,作者:skay 结束了所有UI绘制的学习,智能设备常用的应用音视频类, ...

- 使用pjsip传输已经编码的视频,源码在github

pjsip功能很强,做sip rtp语音通话库首选.在2.0之后,也支持视频.不过,它的视频功能缺省是从视频设备采集,然后进行编译,再发送出去的.假设,我们已经有了视频源,比如IP摄像机,不需要采集和 ...

- EasyPlayer RTSP Android安卓播放器实现视频源快速切换

EasyPlayer现在支持多视频源快速切换了,我们介绍一下是如何实现的. 这个需求通常应用在一个客户端需要查看多个视频源的情况,比如多个监控场景轮播. 由于EasyPlayer的播放端已经放在Fra ...

随机推荐

- Hadoop Hive HBase Spark Storm概念解释

HadoopHadoop是什么? 答:一个分布式系统基础架构. Hadoop解决了什么问题? 答:解决了大数据(大到一台计算机无法进行存储,一台计算机无法在要求的时间内进行处理)的可靠存储(HDFS) ...

- linux-docker下安装禅道全部

友情提示:按照步骤走,99%的人会安装成功,1%的人可以咨询度娘 64位电脑安装禅道,满足发送邮件功能 第一步: docker ps 查看docker中的容器是否有禅道(docker ps -a ...

- Exp0 Kali安装 Week1

20165214 2018-2019-2 <网络对抗技术>Exp0 Kali安装 Week1 任务要求 Kali的下载.安装.共享.软件源. 步骤 1.从Kali的官网下载镜像文件.(直接 ...

- 三星S8相机黑画面解决

最近手机刷机卸载系统软件后有遇到相机黑化面不能工作的情况,同时闪光灯也无法开启,人脸识别也无法使用.具体情况如下图. 后来接上电脑打开logcat,发现相机相关的错误,说libquramresize. ...

- TkbmMWClientQuery的计算字段在CalcFields事件触发次数太多

kbmmw有两处BUG和作者提下,一个是TkbmMWClientQuery的计算字段在CalcFields事件触发次数太多,另一个是在TkbmMemTable的加载数据时字段会执行OnValidate ...

- 在Linux服务器上使用Vbox安装虚拟机

先去官网(www.virtualbox.org)上下载对应Linux系统的Vbox版本. 我这边用的是Oracle Linux 7系统(KDE安装) 使用rpm安装virtualbox 发现报错,按照 ...

- Arm11-mini6410入坑

Mini6410 学习Stm32的时候原子哥的资料真全啊,而且原子哥在他论坛也解答问题.然而现在学习ARM买了一套友善之臂的开发板,官方的资料只能刚好入门而已,其实入门都算不上.看了一下,网上的资料很 ...

- Anagram字符串处理(STL真方便啊。。)

题意:给出一些字符串,认为各个字符个数相同的字符串就是相同的,不区分大小写,找出这些字符串中不与其他字符串相同的字符串并挨个输出 用char orgin[][]把每个字符串保存起来,然后对每个字符串都 ...

- css解决多行溢出显示省略号

多行溢出 仅作为记录方便查找 display: -webkit-box; -webkit-box-orient: vertical; -webkit-line-clamp: number; /*n行溢 ...

- CSS盒子内容

内边距 内边距(padding):内容与边框之间的距离 注意:padding 只能移动盒子的内容 padding属性联写: padding: 10px: 内边距的上下左右都移动 padding: 10 ...