Verilog频率计设计

这是以前的一个可编程逻辑课上机实验三

实验报告

数字频率计的基本设计思路是在给定一个time开始测量的时候产生的T的个数,也就是采用一个标准的基准时钟,在单位时间(1秒)里对被测信号的脉冲数进行计数。测频法包括直接测频法、等精度频率测量法、周期法等。

数字频率计的原理如图6-1所示。对系统时钟的信号分频后产生1Hz的输出频率被作为控制模块的时钟输入,由控制模块产生的计数使能信号和清零信号对计数模块进行控制,而由其产生的锁存信号load对锁存模块进行控制,一旦计数使能信号为高电平,并且时钟上升沿到来,计数器便开始正常计数,清零信号到来则计数清零,而当锁存信号为高电平时,数据便被锁存器锁存,然后将锁存的数据输出到显示模块显示出来,数据锁存保证系统可以稳定显示数据,显示译码驱动电路将二进制表示的计数结果转换成相应的能够在数码显示管上可以显示的十进制结果。

(1)分频器模块

分频器模块将对系统时钟进行分频,输出1Hz赫兹的信号,作为测频控制模块的输入信号。例如,假设系统时钟为1024Hz,则对其进行2的10次方分频即可得到1Hz的分频输出信号。

(2)测频控制模块

测频控制模块的输出包括计数器的使能端,清零端以及数据锁存器的锁存信号。分别控制计数器的计数和清零。当锁存信号为高电平时,计数器的计数结果被锁存并输出到显示模块显示。

module testctl(clk,tsten,clr,load);

input clk;

output tsten,clr,load;

reg loadcnt,div2,clr;

always@(posedge clk)

div2<=~div2;

always@(clk,div2)

begin

if (clk== && div2==)

clr=;

else

clr=;

end

assign load=~div2;

assign tsten=div2;

endmodule

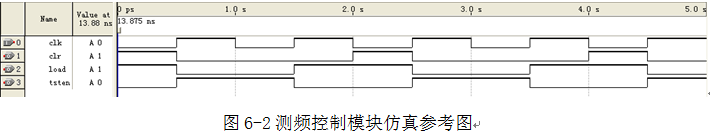

该模块的仿真结果可参考图6-2。

(3)计数器模块

计数器是完成计数步骤的一个单元。它也可用与分频、定时、产生节拍脉冲和脉冲序列等。本设计中为了可以使计数器正常工作,必须只有当使能端为1的时候才开始计数,每个时钟的上升沿到来时计数器加1,当累加到10的时候就清零,同时产生进位信号,同时计数器也应带有清零信号,一旦清零信号有效时,计数器立即清零。

(4)锁存器模块

锁存,就是把信号暂存以维持某种电平状态。测量模块的工作任务成功后,在load信号的上升沿到来时把测量值存入reg当中,之后发送到显示模块当中。锁存器主要是为了保护数据,使其在下次触发或者复位时仍然有效。

(5)显示模块

LED显示器在许多的数字系统中作为显示输出设备,使用非常广泛。它内部有七个发光的a、b、d、e、f和g二极管。通过点亮不同的LED字段,可显示数字0,1,┅,9和A,b,C,d,E,F等不同的字符及自定义一些段发光代表简单符号。

(6)顶层模块

按照图一所示的数字频率计的框图,调用各单元模块,完成数字频率计的顶层设计,并进行仿真,实现频率测量。

练习

(1)分频器模块

module fre_div (clk, clk_out);

input clk;

output clk_out;

reg [:] counter;

reg clk_out;

parameter N = ; //改变N的值变成任意偶分频,同时counter的范围需要相应修改 always @ (posedge clk)

begin

if (counter == N/ - ) //偶分频数一半时反相

begin

clk_out <= ~clk_out;

counter <= ; //置0,从0计数

end

else

counter <= counter + ;

end

endmodule

(2)测频控制模块

module testctl (clk_out_ctl, tsten, rst_ctl, load);

input clk_out_ctl;

output tsten, rst_ctl, load;

reg rst_ctl, div2;

always @(posedge clk_out_ctl) begin

div2 = ~div2;

end

always @(clk_out_ctl or div2) begin

if (clk_out_ctl == && div2 == ) begin

rst_ctl = ;

end

else

begin

rst_ctl = ;

end

end

assign load = ~div2;

assign tsten = div2;

endmodule

(3)计数器模块(改正在注释里)

module counter (enable,clk_t,rst_count,dout,cout);

input enable,clk_t,rst_count;

output [:] dout;

output cout;

reg cout;

reg [:] dout;

always @(posedge clk_t) begin//有问题,always @(posedge clk_t or posedge rst_count) //异步复位

if (!rst_count) begin// if (rst_count) begin dout = 16'd0; cout = 1'b0; end //先写复位,首先考虑复位信号

if (enable) begin// else begin

if(dout == ) begin // if (enable) begin

dout = 'd0; // if(dout == 65535) begin dout = 16'd0; cout = 'b1; end

cout = 'b1; // else dout = dout + 16'd1;

end // end

else begin // end

dout = dout + 'd1;

end

end

end

else begin

dout = 'd0;

cout = 'b0;

end

end

endmodule

(4)锁存器模块

module latch_out (in_dout, save_dout, load_in);

input load_in;

input [:] in_dout;

output [:] save_dout;

reg [:] reg_in;

wire [:] save_dout;

always @(load_in)

if (load_in)

reg_in = in_dout;

assign save_dout = reg_in;

endmodule

(5)显示模块

【1】二进制转BCD码模块(参考)

module bin_bcd_cp (bin, wan, qian, bai, shi, ge, bcd);

input [:] bin;

output [:] bcd;

output reg [:] wan;

output reg [:] qian;

output reg [:] bai;

output reg [:] shi;

output reg [:] ge;

integer i;

always @(bin) begin

wan = 'd0;

qian = 'd0;

bai = 'd0;

shi = 'd0;

ge = 'd0;

for (i = ; i >= ; i = i - ) begin

if (wan > ) wan = wan + ;

if (qian > ) qian = qian + ;

if (bai > ) bai = bai + ;

if (shi > ) shi = shi + ;

if (ge > ) ge = ge + ; wan = wan << ;

wan[] = qian[];

qian = qian << ;

qian[] = bai[];

bai = bai << ;

bai[] = shi[];

shi = shi << ;

shi[] = ge[];

ge = ge << ;

ge[] = bin[i];

end

end

assign bcd = {{{'b0}}, wan, qian, bai, shi, ge};

endmodule

【2】八段显示数码管

module seg7 (data_in, data_out );

input [:] data_in ;

output [:] data_out ;

reg [:] data_out ;

always @(data_in) begin

data_out = 'b1111111;

case (data_in )

'b0000: data_out = 8'b1100_0000; //

'b0001: data_out = 8'b1111_1001; //

'b0010: data_out = 8'b1010_0100; //

'b0011: data_out = 8'b1011_0000; //

'b0100: data_out = 8'b1001_1001; //

'b0101: data_out = 8'b1001_0010; //

'b0110: data_out = 8'b1000_0011; //

'b0111: data_out = 8'b1111_1000; //

'b1000: data_out = 8'b1000_0000; //

'b1001: data_out = 8'b1001_1000; //

'b1010: data_out = 8'b1000_1000; // A

'b1011: data_out = 8'b1000_0011; // b

'b1100: data_out = 8'b1010_0111; // c

'b1101: data_out = 8'b1010_0001; // d

'b1110: data_out = 8'b1000_0110; // E

'b1111: data_out = 8'b1000_1110; // F

default: data_out = 'b1111_1111;

endcase

end

endmodule

(6)顶层模块

把各个模块生成symbol,通过创建 block diagram/schematic file 手动连线生成。

RTL:

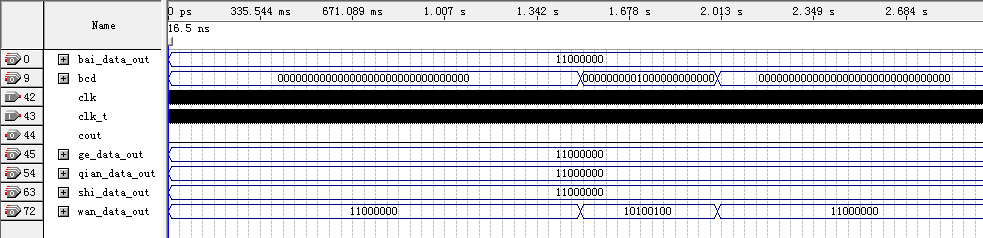

仿真波形:

注:各个小模块的仿真测试都要一个一个做(在此我省略了)

如有错误还请指出,如有侵权还请告知,如需转载请注明出处!

本人博客:http://www.cnblogs.com/yllinux/

Verilog频率计设计的更多相关文章

- 从头学起Verilog(三):Verilog逻辑设计

引言 经过了组合逻辑和时序逻辑的复习,终于到了Verilog部分.这里主要介绍Verilog一些基础内容,包括结构化模型.TestBench编写和仿真.真值表模型. 这部分内容不多,也都十分基础,大家 ...

- 用Verilog语言设计一个3-8译码器

case语句 if_case语句 源码下载 Github >>

- Verilog设计技巧实例及实现

Verilog设计技巧实例及实现 1 引言 最近在刷HDLBits的过程中学习了一些Verilog的设计技巧,在这里予以整理.部分操作可能降低代码的可读性和Debug的难度,请大家根据实际情况进行使用 ...

- Verilog代码规范I

Verilog代码规范I "规范"这问题 "规范"这个富含专业气息的词汇(个人感觉),其实规范这种东西,就是大家都约定熟成的东西,一旦你不遵守这个东西,专业人士 ...

- Verilog学习笔记简单功能实现(三)...............同步有限状态机

在Verilog中可以采用多种方法来描述有限状态机最常见的方法就是用always和case语句.如下图所示的状态转移图就表示了一个简单的有限状态机: 图中:图表示了一个四状态的状态机,输入为A和Res ...

- Verilog HDL基础语法讲解之模块代码基本结构

Verilog HDL基础语法讲解之模块代码基本结构 本章主要讲解Verilog基础语法的内容,文章以一个最简单的例子"二选一多路器"来引入一个最简单的Verilog设计文件的 ...

- verilogHDL设计中的同步时序逻辑

引用自夏宇闻教授 1.同步时序逻辑: 是指表示状态的寄存器组的值只能在唯一确定的触发条件发生改变. 只能由时钟的正跳变沿或者负跳变沿触发的状态机就是一例,always@(posedge clk). 1 ...

- 【转】uvm 与 system verilog的理解

http://www.cnblogs.com/loves6036/p/5779691.html 数字芯片和FPGA的验证.主要是其中的功能仿真和时序仿真. 验证中通常要搭建一个完整的测试平台和写所需要 ...

- 跨时钟域设计【一】——Slow to fast clock domain

跨时钟域设计是FPGA设计中经常遇到的问题,特别是对Trigger信号进行同步设计,往往需要把慢时钟域的Trigger信号同步到快时钟域下,下面是我工作中用到的慢时钟域到快时钟域的Verilog HD ...

随机推荐

- Js 处理 错误图片...(不用jquery)

document.addEventListener("error", function (e) { var elem = e.target; if (elem.tagName.to ...

- Tomcat故障

1.1 故障日志 31-May-2018 16:11:41.136 INFO [http-nio-8017-exec-5] org.apache.coyote.http11.AbstractHttp1 ...

- Android_靠谱的监听软键盘状态的方法

public class MyActivity extends AppCompatActivity { /** * 当前界面中的软件盘的状态 */private boolean isKeyBoardO ...

- restframework 的一些操作

路飞学城项目: 1 Vue 2 restframework框架(一周) 3 学城项目(一周-两周) day98 1 CBV(class based view) 与 FBV(function based ...

- 如何使用java代码进行视频格式的转换(FLV)

如何使用java代码进行视频格式的转换(FLV) 一,前言 在给网页添加视频播放功能后,发现上传的视频有各种格式,那么就需要将他么转换成FLV,以很好的支持在线视频播放. 公司一直在使用中,配合使用, ...

- 导入AppiumLibrary报错: ImportError: cannot import name 'InvalidArgumentException

导入AppiumLibrary报错: ImportError: cannot import name 'InvalidArgumentException报错原因 selenium.common.exc ...

- Silverlight 减小 Xap 的大小

当Silverlight工程引用了很多dll后,加载的速度就会很慢,通过下面方式可以减小xap包的大小 勾选 “通过使用应用程序库缓存减小xap大小”,勾选此项后vs会自动将微软自身和外部引用不变的d ...

- RTT之AT命令组件

包含客户端和服务器:用于GPRS和3G的通讯命令格式.四种基本功能 测试功能:AT+<x>=? 用于查询命令参数格式及取值范围: 查询功能:AT+<x>? 用于返回命令参数当前 ...

- cpp 学习笔记

1.C++中模仿gets是 getline(cin, string object) #include <bits/stdc++.h> #define IOS ios::sync_with ...

- MATLAB线性回归方程与非线性回归方程的相关计算

每次比赛都需要查一下,这次直接总结到自己的博客中. 以这个为例子: 2.线性方程的相关计算 x=[1,2,3,4,5]';%参数矩阵 X=[ones(5,1),x];%产生一个5行一列的矩阵,后接x矩 ...