Windows状态栏图标显示异常

计数器,FPGA设计中最常用的设计,然而有些地方需要多加注意。

一、勿要多计

打算计10下,所以我计数器就写计到10:cnt==10,程序如下所示。

1、设计文件

module jsq

//========================< 端口 >==========================================

(

input wire clk ,

input wire rst_n ,

input wire en ,

output reg [ :] cnt

);

//========================< 信号 >==========================================

reg en_flag ;

wire add_cnt ;

wire end_cnt ; //========================< 程序 >==========================================

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

en_flag <= ;

end

else if(en) begin

en_flag <= ;

end

else if(end_cnt) begin

en_flag <= ;

end

end always @(posedge clk or negedge rst_n) begin

if(!rst_n)

cnt <= ;

else if(add_cnt) begin

if(end_cnt)

cnt <= ;

else

cnt <= cnt + ;

end

end assign add_cnt = en_flag;

assign end_cnt = add_cnt && cnt== ; //我想计10下 endmodule

2、仿真文件

`timescale 1ns/1ps //时间精度

`define Clock //时钟周期 module jsq_tb; //========================< 端口 >==========================================

reg clk ; //时钟,50Mhz

reg rst_n ; //复位,低电平有效

reg en ;

wire [ :] cnt ; //==========================================================================

//== 模块例化

//==========================================================================

jsq u_jsq

(

.clk (clk ),

.rst_n (rst_n ),

.en (en ),

.cnt (cnt )

); //==========================================================================

//== 时钟信号和复位信号

//==========================================================================

initial begin

clk = ;

forever

#(`Clock/) clk = ~clk;

end initial begin

rst_n = ; #(`Clock*+);

rst_n = ;

end //==========================================================================

//== 设计输入信号

//==========================================================================

initial begin

en = ;

#(`Clock*+); //初始化完成

en = ;

#(`Clock*);

en = ;

#(`Clock*);

$stop;

end endmodule

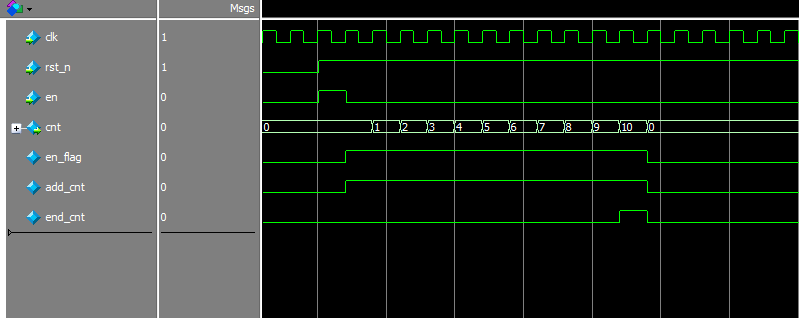

3、Modelsim仿真图像

观察图像可以看到,计数器 cnt 计到了 cnt==10 这里,可是当我仔细数数时却发现,计数是从 0 开始计的,从 0 到 10,所以实际计了 11 下!和我之前写代码时脑中所想不一致!所以,如果只想计10下,那实际写代码应该写 9 才对。

总结:计数器想计 n 下,那写代码只能写 cnt==n-1。

二、勿要少记

数据 data 和数据使能 data_en 同时来,我想数一下到底来了多少个数据。

1、代码设计

module jsq

(

input wire clk ,

input wire rst_n ,

input wire [ :] data ,

input wire data_en ,

output reg [ :] cnt

); always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

cnt <= ;

end

else if(data_en) begin

cnt <= cnt + ;

end

else begin

cnt <= ;

end

end endmodule

2、仿真设计

`timescale 1ns/1ps //时间精度

`define Clock //时钟周期 module jsq_tb; //========================< 端口 >==========================================

reg clk ; //时钟,50Mhz

reg rst_n ; //复位,低电平有效

reg [ :] data ;

reg data_en ;

wire [ :] cnt ; //==========================================================================

//== 模块例化

//==========================================================================

jsq u_jsq

(

.clk (clk ),

.rst_n (rst_n ),

.data (data ),

.data_en (data_en ),

.cnt (cnt )

); //==========================================================================

//== 时钟信号和复位信号

//==========================================================================

initial begin

clk = ;

forever

#(`Clock/) clk = ~clk;

end initial begin

rst_n = ; #(`Clock*+);

rst_n = ;

end //==========================================================================

//== 设计输入信号

//==========================================================================

initial begin

data_en = ;

data = ;

#(`Clock*+); //初始化完成 data_en = ;

data = ;

#(`Clock);

data = ;

#(`Clock);

data = ;

#(`Clock);

data = ;

#(`Clock);

data = ;

#(`Clock);

data = ;

#(`Clock);

data = ;

#(`Clock);

data = ;

#(`Clock);

data = ;

#(`Clock);

data = ;

#(`Clock);

data = ;

data_en = ; #(`Clock*);

$stop;

end endmodule

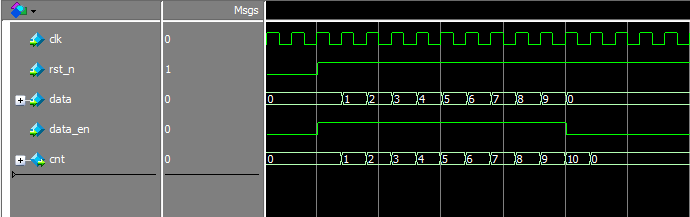

3、Modelsim仿真图像

观察图像可以看到,计数器 cnt 计到了 cnt==10 这里,而我的 data_en 确实是维持了 10 个周期的。这种情况下,cnt 计到多少就是多少,第0下是不作数的。如果按照上面的情况,以为真实计数是 10-1=9下,反而是错的了。当然如果其他信号需要用到 cnt来搞事情,那还是需要写 cnt==n-1的,这就又回到上面第一种情况了。

此外 cnt 较 data_en 延后了一个周期,当 data_en 都拉低了,而后 cnt 才计到 cnt==10,这是时序逻辑的特点,并非出错。

总结:计数器计算一段波形的持续时间,最终即到 cnt==n,那波形时间就是n,不需要 -1。

Windows状态栏图标显示异常的更多相关文章

- Win32项目生成的程序exe图标显示异常的问题

问题 如图: 用VS2013生成exe执行文件时发现的问题,起初以为是没添加ico图像的最小尺寸,后来查看ico并不是这个问题. Baidu.Google了半天找到原因:文件资源管理器的图标缓存bug ...

- PC上图标显示异常 白色框框处理方案

步骤如下: 1.打开360安全卫士,点击图标显示异常的立即修复 2.修复完,图标就正常了 3.分析原因: 可能是我用了魔方优化大师(TweakerCube)优化了桌面快捷方式(去掉箭头)引起的,而且是 ...

- thinkphp使后台的字体图标显示异常

thinkphp使后台的字体图标显示异常 相似问题 1.thinkPHP的这些图标都不显示了-CSDN论坛https://bbs.csdn.net/topics/391823415 解答: 发现在别的 ...

- WIN10图标显示异常

1.打开控制面板,右上边查看方式选择边小图标显示 2.打开显示里面的自定义缩放级别 3.设置级别为125% 然后点击 应用 4.注销或者重启,然后将异常的快捷方式点击打开,就会恢复正常,至少我的是回 ...

- win7记事本txt图标显示异常解决方法

链接:https://zhidao.baidu.com/question/2076205353435701108.html ...

- WIN7下重建图标缓存(解决MFC.exe桌面图标显示异常问题)

WIN7下重建图标缓存 使用WIN7时,MFC工程生成的应用程序图标,如果更改为自定义的ICON图标之后可能在桌面上显示的依旧是上一次的图标,改个名或换个路径都能恢复正常,说明在WIN7系统下图标的缓 ...

- office word excel等图标显示异常

1.查看注册表:查看参数对应的路径被删除,计算机搜索新的文件路径更改路径即可.以此类推~ 计算机\HKEY_CLASSES_ROOT\Excel.Sheet.12\DefaultIcon 正常exce ...

- Windows右下角图标显示不正常

我的win7系统,右下角图标透明,分不清哪个是哪个.点击也没有任何反应. 解决办法: 点击运行输入cmd,在命令提示符下输入下列命令即可恢复. taskkill /im explorer.exe /f ...

- Windows 托盘区域显示图标

NOTIFYICONDATA structure 这个结构体包含了向通知区域(底部任务栏右下角区域,下面都称为托盘)显示的信息.需要使用函数Shell_NotifyIcon. 结构体成员 typede ...

随机推荐

- 第03组 Alpha冲刺(4/4)

队名:不等式方程组 组长博客 作业博客 团队项目进度 组员一:张逸杰(组长) 过去两天完成的任务: 文字/口头描述: 制定了初步的项目计划,并开始学习一些推荐.搜索类算法 GitHub签入纪录: 暂无 ...

- nuxt项目服务端渲染应用部署、使用pm2守护进程及遇到的问题处理

服务端渲染应用部署应该先编译构建,然后再启动 Nuxt 服务,可通过以下两个命令来完成: nuxt build nuxt start 我们已经在pakage.json里配置好script命令 { &q ...

- gitlab 上传代码

#生成公钥ssh-keygen -t ed25519 -C "xxx@tianwang.com"#拷贝公钥pbcopy < ~/.ssh/id_ed25519.pub 在网页 ...

- (持续更新) C# 面试技术点、常见SQL技术点 和 解决高并发的相关技术

这篇博客 持续更新. 方便小伙伴们学习与面试前的复习

- jmeter(四十五)常用Beanshell脚本

整理了一批jmeter常用的beanshell脚本供大家参考! 时间戳 import java.text.SimpleDateFormat; import java.util.Calendar; im ...

- OpenStack创建网络和虚拟机、dhcp设备、虚拟路由器、虚拟机访问外网原理分析

创建网络和虚拟机流程: 1.创建网络和子网 背后发生了什么: Neutron让控制节点上针对此子网的dhcp(虚拟设备)启动,用于给该子网下的实例分配ip 2.生成虚拟机 背后发生了什么: 用户通过G ...

- Flask纪要

flask学习过程 1框架基础 2redis高性能key-value数据库 3视图具有装饰器的路由函数 4模板html文件 面向对象操作数据库orm 5蓝图 6单元测试 7GitHub 8项目 学习的 ...

- EF获取当天的数据集合

).DefaultIfEmpty().Count(); 主要是使用了: DbFunctions.DiffDays

- promise 和 async await比较

async搭配await是ES7提出的,它的实现是基于Promise.这里使用它对比Promise的用法,这里只是简单的适合日常业务的使用场景. async.await是ES7中的提案,通过同步方 ...

- 关于Oracle to_date函数的高级用法

由于种种原因,在我们的系统中,账套期间(PERIOD_NAME)由于格式设置的原因,数据库层存储的格式如下 Mar-19,而不是常规的2019-03. 我们无法更改数据库,涉及到的点太多. 但是期间数 ...